# **IJCAR 2008**

4th International Joint Conference on Automated Reasoning

Sydney, Australia, August 10-15, 2008

# **Workshop Program**

# 5th International Verification Workshop – VERIFY'08

Bernhard Beckert and Gerwin Klein (Chairs)

WS 1 - August 10/11

## Preface

The VERIFY workshop series aims at bringing together people who are interested in the development of safety and security critical systems, in formal methods, in the development of automated theorem proving techniques, and in the development of tool support. Practical experiences gained in realistic verifications are of interest to the automated theorem proving community and new theorem proving techniques should be transferred into practice. The overall objective of the VERIFY workshops is to identify open problems and to discuss possible solutions under the theme "What are the verification problems? What are the deduction techniques?".

This volume contains the research papers presented at the 5th International Verification Workshop (VERIFY'08) held August 10–11, 2008 in Sydney, Australia. This workshop was the fifth in a series of international meetings since 2002. It was affiliated with the 4th International Joint Conference on Automated Reasoning (IJCAR 2008).

Each paper submitted to the workshop was reviewed by three referees, and an intensive discussion on the borderline papers was held during the online meeting of the Program Committee. 7 research papers were accepted based on originality, technical soundness, presentation, and relevance. We wish to sincerely thank all the authors who submitted their work for consideration. And we would like to thank the Program Committee members and other referees for their great effort and professional work in the review and selection process. Their names are listed on the following pages.

In addition to the contributed papers, the program included two excellent keynote talks. We are grateful to Prof. Gilles Barthe (IMDEA Software, Madrid, Spain) and Prof. Gernot Heiser (National ICT and Univ. of New South Wales, Sydney, Australia) for accepting the invitation to address the workshop.

August 2008 Bernhard Beckert

Gerwin Klein

# Program Co-Chairs and Organisers

Bernhard Beckert University of Koblenz-Landau, Germany Gerwin Klein National ICT Australia, Sydney, Australia

## **Program Committee**

Serge Autexier DFKI and University Saarbrücken, Germany

Gilles Barthe IMDEA Software, Madrid, Spain

Peter Baumgartner National ICT Australia, Canberra, Australia

Bruno Dutertre SRI International, USA

Reiner Hähnle Chalmers University, Gothenburg, Sweden Andrew Ireland Heriot-Watt University, Edinburgh, UK

Joseph Kiniry University Dublin, Ireland Heiko Mantel TU Darmstadt, Germany Stephan Merz INRIA Lorraine, France

Carroll Morgan Univ. of New South Wales, Sydney, Australia

Peter Müller Microsoft Research, Redmond, USA

Michael Norrish National ICT Australia, Canberra, Australia Wolfgang Paul Saarland University, Saarbrücken, Germany

Lawrence C. Paulson University of Cambridge, UK

Wolfgang Reif University of Augsburg, Germany

Wolfram Schulte Microsoft Research, Redmond, USA

Johann Schumann NASA Ames Research Center, USA

Luca Viganò University of Verona, Italy

Toby Walsh National ICT Australia, Sydney, Australia

Christoph Walther TU Darmstadt, Germany

## Steering Committee

Serge Autexier DFKI and University Saarbrücken, Germany

Heiko Mantel TU Darmstadt, Germany

#### **Additional Referees**

Burkhard Wolff Cesare Tinelli Peter H. Schmitt Simon Bäumler

# Table of Contents

| Invited Talks                                                                                                |    |

|--------------------------------------------------------------------------------------------------------------|----|

| Certificate Translation                                                                                      | 1  |

| Operating System Verification for Real Use  Gernot Heiser                                                    | 2  |

| Research Papers                                                                                              |    |

| Model Checking for Stability Analysis in Rely-Guarantee Proofs                                               | 3  |

| Compositional Proofs with Symbolic Execution                                                                 | 12 |

| Specification Predicates with Explicit Dependency Information Richard Bubel, Reiner Hähnle, Peter H. Schmitt | 28 |

| Bitfields and Tagged Unions in C: Verification through Automatic Generation                                  | 44 |

| Model Stack for the Pervasive Verification of a Microkernel-based Operating System                           | 56 |

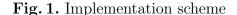

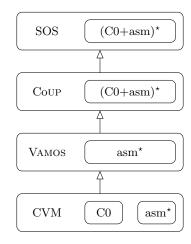

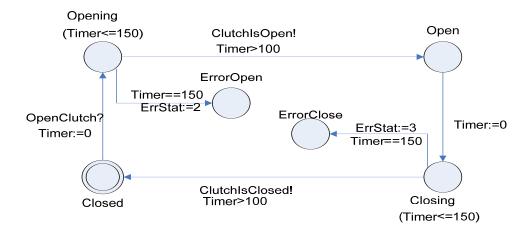

| Exploring Model-Based Development for the Verification of Real-Time Java Code                                | 71 |

| Precise Dynamic Verification of Confidentiality                                                              | 82 |

| Author Index                                                                                                 | 97 |

# Certificate Translation\*

Gilles Barthe

IMDEA Software, Madrid, Spain gilles.barthe@imdea.org

#### Abstract

Program verification techniques based on programming logics and verification condition generators provide a powerful means to reason about programs. Whereas these techniques have very often been employed in the context of high-level languages in order to benefit from their structural nature, it is often required, especially in the context of mobile code, to prove the correctness of compiled programs. Thus it is highly desirable to have a means of bringing the benefits of source code verification to code consumers.

Certificate translation is a general method to transfer to code consumers evidence gained through verification of source code; it relies on the notion of certificate, used in Proof-Carrying Code to convey to the code consumer independently verifiable evidence that programs respect policies. The talk provides sufficient conditions of existence for algorithms that transform certificates of source programs into certificates of compiled programs, and show that many common transformations comply with these conditions.

$<sup>^{\</sup>star}$  Joint work with Benjamin Grégoire, César Kunz, and Tamara Rezk

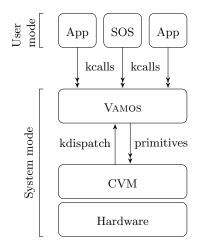

# Operating System Verification for Real Use

#### Gernot Heiser

School of Computer Science and Engineering, University of New South Wales, and Embedded, Real-Time and Operating Systems Program, National ICT Australia Sydney, Australia gernot@nicta.com.au

#### Abstract

Software verification remains an academic exercise as long as it focusses on toy problems, such as systems that are too simplified for practical deployment, or perform too poorly. Furthermore, formal verification of software is of limited benefit if the software is deployed in a system where it executes on top of an unverified operating system.

This talk presents an overview of an effort at NICTA which aims to formally verify a complete operating-system kernel, designed for deployment in main-stream embedded systems. It will explain the approach taken to address the conflicting goals of verifiability, general applicability and high performance. The kernel, called seL4, is designed to replace commercially-deployed high-performance L4 microkernels with no more than 10% performance degradation. The project, which has been running since early 2004, is scheduled to complete by the end of this year.

# Model Checking for Stability Analysis in Rely-Guarantee Proofs

Hasan Amjad and Richard Bornat

Middlesex University School of Computing Science, London NW4 4BT, UK

Hasan.Amjad@cl.cam.ac.uk R.Bornat@mdx.ac.uk

**Abstract.** Rely-guarantee (RG) reasoning is useful for modular Hoare-style proofs of concurrent programs. However, RG requires that assertions be proved stable under the actions of the environment. We cast stability analysis as a model checking problem and show how this may be of use in interactive and automatic verification.

## 1 Introduction

Multi-core and multi-processor computing systems are now mainstream. Consequently, concurrent programs are the focus of much recent research on automatically proving safety, correctness and liveness properties. Often, the assertions we would like to prove are not amenable to existing automatic analyses. This paper studies one such scenario, and shows how existing automatic techniques can nonetheless help the proof process. The demonstration is expected to be the first step towards a fully automatic method.

Shared-memory concurrency, where multiple threads have read/write access to the same memory addresses, is commonplace. The main challenge in proving properties of such programs, and indeed in their design, is dealing with interference, i.e., the possibility that threads may concurrently make changes to the same memory address.

The concurrent programming community has evolved several synchronisation schemes to avoid interference. Most rely on some form of access denial, such as locks. Whereas locks make it easy to reason about the correctness, they may also cause loss of efficiency as threads wait to acquire locks on needed resources. Locking schemes have thus become increasingly fine-grained, attempting to deny access to the smallest possible size of resource, to minimise waiting and maximise concurrency. The ultimate form of such fine-grained concurrency are programs that manage without any synchronisation at all [14].

The finer the concurrency, the more involved the logic for avoiding interference. This logic must implicitly or explicitly take the actions of other threads into account. This is a problem for program proofs where we strive for modularity, i.e., we wish to be able to reason about a piece of code in isolation from the various environments it could execute in.

Rely-guarantee reasoning [11] offers a solution to this problem within the framework of Hoare-style program proofs [10], by encoding the environment into

#### 4 Hasan Amjad, Richard Bornat

the proof: all assertions must be shown to be unaffected under the actions of the environment. Automatically checking for and ensuring such non-interference can be problematic in many cases. In this paper, we describe preliminary progress on a possible solution.

The next section gives brief relevant background. We then describe our method, and comment on shortcomings and possible developments. We assume some familiarity with program proofs using Hoare logic [10], and with model checking [2].

## 2 Preliminaries

## 2.1 Rely-guarantee Reasoning

Rely-guarantee (RG) is a compositional verification method for shared memory concurrency introduced by Jones [11]. Interference between threads is described using binary relations. In that treatment, post-conditions were relational, so assertions could talk about the state before and after an action. Here, in line with traditional Hoare logic, we shall use post-conditions of a single state, as this usually makes for simpler proofs. In either case, the essence of RG is unaffected by this choice.

Our command language will be the one used by Jones [11], i.e., with assignment, looping, branching, sequential composition and parallel composition, using C-like syntax. For parallel composition we assume standard interleaved execution semantics, i.e., threads are programs with access to some shared state, and atomic instructions occur interleaved.

Program variables will range over  $\mathbb{B}$  and  $\mathbb{N}$ . It may seem odd to have program variables range over infinite types. In practice however, reasoning about numbers with the aid of abstraction, has been found to be more tractable than reasoning about finite but huge state spaces over words or bit-vectors, which are harder to abstract due to fiddly problems with overflow and underflow.

RG can be seen as a compositional version of the Owicki-Gries method [15]. The specification for a command C is a four-tuple (P, R, G, Q), where P and Q are the usual Hoare logic pre- and post-condition assertions on a single state. C satisfies this specification if from a state satisfying P, and under environmental interference R (the rely), C causes interference at most G (the guarantee), and if it terminates, it does so in a state satisfying Q.

R and G summarise the properties of the individual atomic actions invoked by the environment and the thread respectively. An action is given as a binary relation on the shared state, and is written  $P \rightsquigarrow Q$ . This notation indicates that the action updates the part of shared state that satisfies P (at the moment the action executes), so that it satisfies Q.

For example, the action corresponding to the command x := x + 1, that increments a shared integer x, might be written as

$$x = N \leadsto x = N + 1$$

where the implicitly existentially quantified N serves to relate the state before and after the execution. Such logical variables are required for describing actions using single-state assertions. We shall denote them using  $N, M, \ldots$  and assume they are existentially quantified with scope limited to the action.

G is the relation given by the reflexive and transitive closure of all actions of the thread being specified. The actions are given by manual annotation, as in general, automatic action discovery is non-trivial. R is calculated in an identical manner from the actions of the environment. Typically, the actions comprising R are just the G actions of all the other threads.

An assertion P on a single state is considered *stable* under interference from a binary relation R if  $(P;R) \Rightarrow P$ , i.e., if P(s) and  $(s,s') \in R$ , then P(s'). More specifically, if P is the pre-condition for some command C, then it must continue to hold after any environment action, before the execution of C. For our purpose, we do not need to pin down the level of atomicity of execution.

Jones gives a full proof system for the satisfaction relation, but we will not need it for this work. However, we reproduce the two critical rules here, to make our assumptions about RG concrete. The first rule is parallel composition, where || is the interleaving parallel composition operator.

$$\frac{(P_1, R \vee G_2, G_1, Q_1) \vDash C_1 \qquad (P_2, R \vee G_1, G_2, Q_2) \vDash C_2}{(P_1 \wedge P_2, R, G_1 \vee G_2, Q_1 \wedge Q_2) \vDash C_1 ||C_2|}$$

The second rule tells us what it means for a command to be atomic.

$$\frac{(P,id,\mathbf{true},Q\wedge G)\vDash C \qquad P \text{ stable under } R}{(P,R,G,Q)\vDash atomic(C)}$$

Note one departure from standard RG: the post-condition of the very last line of code is not checked for stability. It is instantaneously true immediately after execution of that line. At this point, either the thread terminates, so that we do not care whether the environment interferes with the post-condition, or, the thread resumes execution from some command the pre-condition of which will be the same as this post-condition, and thus will be checked for stability.

#### 2.2 Temporal Logic Model Checking

Let V be the set of program variables (or *state variables*) used in a program (with appropriate scope management, which we ignore without loss of generality).

Each  $v \in V$  ranges over a non-empty set of values  $D_v$ . The state space S of the program is given by  $\prod_{v \in V} D_v$ . A single state of the program is then a value assignment to each  $v \in V$ .

Suppose AP is the set of all those atomic propositions over V that we might use in the specification of a program. Then we can turn the program into a state machine (technically, a Kripke structure) M represented as a tuple (S, S0, T, L) where S is the set of states,  $S0 \subseteq S$  is the set of initial states,  $T \subseteq S \times S$  is the transition relation, and  $L: S \to 2^{AP}$  labels each state with the subset of AP that is true in that state.

A temporal logic augments propositional logic with modal and fix-point operators. The semantics of a temporal logic formula in which the atomic propositions range over AP can be expressed in terms of sets of states and/or sequences of states of M. If we turn a program into a state machine, we can use temporal logics to express time-dependent properties of the program.

The most common such property is the global invariant, i.e., a property that holds in all states of a state machine, or equivalently, always holds during the execution of a program.

Global invariants can be checked automatically using proof procedures known as model checkers, subject only to time and space constraints. More importantly, if the proof attempt fails, the model checker can return a counterexample, which is an execution path (sequence of states) leading from an initial state to a state in which the invariant is not satisfied.

The problem of model checking global invariants is in general undecidable when the state space is infinite. However, the ability to produce counterexamples has led to the development of counterexample guided abstraction refinement (CEGAR) [3,16], where the state space is first abstracted to a simpler one, and if the constructed abstraction is too general it can often be automatically iteratively refined until the desired property is verified. For our purposes we will assume a simple abstraction scheme consisting of a single total abstraction function  $\alpha: S \to A$ , where A is the abstract state space (the exact structure of which depends on the  $\alpha$  under consideration). Typically,  $\alpha$  is not injective and need not be surjective.

We do not need to describe model checking or CEGAR in more depth, particularly as there are many different abstraction schemes and CEGAR techniques. Further details may be found in [2, 3, 7, 16].

# 3 Stability Analysis as Model Checking

If the assertion permits, stability can be checked syntactically and unstable assertions can be automatically stabilised by a fix-point computation that disjunctively adds state until stability is achieved. More precisely, given an assertion

satisfying a set of states s, we compute the fix-point by

$$s_0 = s \qquad s_{n+1} = s_n \cup R(s_n)$$

until  $s_{n+1} = s_n$ , i.e, performing n environment transitions. If the domain of any program variable is infinite, this fix-point computation might not terminate. In such cases, automatic stabilisation techniques rely on abstract interpretation to simplify the domain.

As a simple example, consider the assertion x=10 that is clearly unstable under the environment action  $x=N \rightsquigarrow x=N+1$ . To stabilise, we would proceed

```

s_0 = (x = 10)

s_1 = (x = 10 \lor x = 11)

s_2 = (x = 10 \lor x = 11 \lor x = 12)

:

```

so automatic stabilisation will not terminate. To fix it, we could use the boolean abstraction  $\alpha(x) \iff x \geq 10$ . Under this abstraction the action above becomes the identity action in all cases except when x = 9, but in that case x = 10 does not hold anyway, so we have stability immediately, and the assertion is stabilised to  $x \geq 10$ .

In general, if the abstraction is too weak, it may throw away so much information that the proof becomes impossible (e.g., we can trivially stabilise any assertion by replacing it with **true**). But if the abstraction is too strong, the fix-point computation may not terminate, or may run out of time or space resources.

Current techniques therefore use hand-crafted abstraction heuristics that are found to work in practice, for the underlying variable domains [5, 17].

We have seen in §2.2 that this problem of finding exactly the right level of abstraction also occurs in model checking. It is our hope that the model checking solution can be applied to stability analysis as well. If so, the vast amount of model checking research on this topic can be brought to bear on the problem. We now present the first step towards this goal, by representing stability analysis as a model checking problem.

Rather than representing R and G as the reflexive transitive closures of their constituent actions, we consider them as state machines over the shared state. In addition, the state machine also has state variables for the program counters of the constituent threads. Tracking program counters allows us to easily encode the flow control of actions in the state machine.

The state machine for the guarantee condition  $G_t$  for a thread t, is  $M_t = (S_t, S_t, t, L_t)$  and is constructed as follows. Let  $V_t$  be the set of all shared program variables used in t as well as the t program counter  $p_{c_t} : \mathbb{N}$ . Then  $S_t$  is

constructed like S in §2.2.  $S0_t$  is those states of  $S_t$  in which  $pc_t = 0$  and in which any other  $v \in V_t$  are assigned their initial values if any. Let  $a_l$  be the (possibly empty) set of actions associated with the primitive command on line l of the thread code (this is for easy specification: in reality a single atomic statement can only have a single associated action, so the analysis simply conjoins them). Then

$$t((s, pc_t), (s', pc'_t)) = \bigvee_{l} \left( pc_t = l \land pc'_t = next(s, l) \land \bigwedge_{a \in a_t} a(s, s') \right)$$

where the *next* function encodes the control flow of thread t. Finally,  $L_t(s) = \{p \in AP \mid p(s) = \mathbf{true}\}$ . The state machine for R,  $M_R = (S_R, S0_R, T_R, L_R)$  over variables  $V_R$ , is constructed analogously, though of course it is more complicated since it encompasses the actions of all the other threads.

Now suppose that we wish to stabilise an assertion P that is the pre-condition of a command at program line l in a thread t. The first step is to check whether the assertion is already stable. To do this we augment  $M_R$  with fresh<sup>1</sup> variables corresponding to any thread-local variables that occur in P, and also add identity actions over these variables to  $T_R$  so that their values never change. This represents our intuition that when checking the stability under the environment of an assertion in thread t, t itself is not executing.

We can now model check the augmented state machine  $M'_R$  for the global invariant P. Note that here we can use standard model checking abstraction construction techniques [7] to try and avoid non-termination. If the invariant holds, then since it is a global invariant and  $\alpha$  is total, it holds in the concrete state space as well. Otherwise, we will obtain a counter-example giving a sequence of actions of the abstract state machine that violates the invariant. At this point, standard CEGAR techniques can be employed to check whether the counterexample has a corresponding concrete trace, in which case the stability check has failed. If not, the abstract trace is spurious (caused by too weak an abstraction), so we refine the abstraction using standard CEGAR methods and call the model checker again, until we have success or failure.

At this point we have already improved on existing stabilisation methods by not being reliant on having a syntactic check for stability. However, we still have to handle the case where the stability check fails.

In this situation, we have at hand a counterexample trace  $\pi$  showing a sequence of environment actions that falsified P, and also the particular abstraction function  $\alpha$  being used by the model checker when the stability check failed. These two pieces of information can be used to weaken P and then repeat the stability check, and iterate until P is stable.

So that there is no name clash with any  $v \in V_R$ .

For example, if we are using predicate abstraction techniques, then for our running example where we are checking stability of  $P \equiv x = 10$ , we may have

$$\alpha(x) \iff x = 10 \quad \text{and} \quad \pi \equiv x = 10 \rightsquigarrow_k x = 11$$

where k uniquely identifies the action responsible. This information suggests generalising P to  $x \ge 10$ , and then the stability check succeeds.

This is as far as we have come. The new weakened assertion must be found manually for now, using the point-of-failure  $\alpha$  and  $\pi$  as guides, as in the example above. Of course, we could simply use the existing method of repeated disjunctive addition of the resultant state of the involved actions (which in this cherry-picked example fails to terminate). However, the model checking approach gives us extra information (point-of-failure  $\pi$  and  $\alpha$ ) which should hopefully allow us to do better. We plan to develop an automatic method that uses symbolic simulation driven by the counterexample traces, perhaps in combination with heuristics, to weaken P in a useful manner. Here, we expect to use existing model checking research on automatic abstraction construction [8].

In fact, at the moment our in-development tool (effectively a translation layer on top of the NuSMV model checker [1]) does not even perform abstraction, as all our test assertions are over finite domains. This is because while it would be simple to switch to a tool supporting automatic abstraction (e.g., BLAST [9]), we are more interested in finding out how to use  $\pi$  to weaken P, which is the real challenge.

#### 3.1 Comment: Refining Stability

In standard RG, the rely is represented as the reflexive transitive closure of all actions that the environment can execute. This can also be thought of as a state machine, albeit a not very informative one in which any transition (action) can execute from any state. Thus, our representation of R and G as state machines of actions can be seen as a refinement of the standard RG representation. The latter can be thought of as the state machine consisting of all states reachable from any state via all possible interleavings of the underlying actions, regardless of whether these interleavings will ever actually occur. Our refinement proceeds by adding control flow information, thus ruling out certain interleavings.

Thus it is possible for us to prove the stability of stronger assertions than is possible in standard RG. Since the stability check is orthogonal to the RG proof system, this means that we automatically obtain a stronger proof system.

Indeed, we can parameterise the RG proof system by the level of refinement of R and G. We have experimented along these lines by adding some G actions to R, or by selectively exposing the thread-local state of the environment, both of which rule out some class of impossible action sequences. In each case we

have been able to prove properties that are stronger, and often more intuitive to specify.

There is a trade-off here, since adding more information to R and G will almost certainly make the underlying model checking problem harder, affecting scalability. Nonetheless, increasing the refinement level is attractive not only because it permits stronger properties to be proved, but also because the stabilised assertion may be syntactically smaller and thus more readable. This latter consideration is important if these methods are used as part of a larger interactive proof framework, such as a theorem prover.

# 4 Remarks

We do not know of any other work that uses model checking for stability analysis in Hoare-style RG proofs. There is work underway at MSR Cambridge [6] that also represents R and G as state machines, but their aim is to deal with questions of liveness. Other than that we know only of the automatic stabilisation work that inspired our own effort [17].

It is well known [4] that the standard RG proof rule for parallel composition can become unsound if the satisfaction relation is strengthened (e.g., to include liveness). We are safe since stability is a safety property, for which the standard RG proof system is sound.

Apart from the unfinished aspect, this approach has other shortcomings. An important one is that refining R and G quickly makes the underlying model checking problem more resource intensive. The same refinement (specifically, the need to track program counters) also prevents the results from scaling up to arbitrary numbers of threads for free, unlike in standard RG. We expect that model checking techniques like parametric verification [13] and assume-guarantee reasoning [12] (not to be confused with rely-guarantee) may help with this. More generally, our ability to change the refinement level of R and G should also help ameliorate the situation.

We are also considering the use of separation logic in this framework, to frame out irrelevant state and thus alleviate our model checking woes. RG and separation logic have already been combined [18]. Extending that framework to our method will be another thread of future work.

Acknowledgement The first author would like to thank Viktor Vafeiades for permission to copy from the description of RG in his Ph.D. thesis.

# References

1. Alessandro Cimatti, Edmund M. Clarke, Enrico Giunchiglia, Fausto Giunchiglia, Marco Pistore, Marco Roveriand, Roberto Sebastiani, and Armando Tacchella. NuSMV 2: An OpenSource tool for symbolic model checking. In Ed Brinksma and Kim Guldstrand Larsen, editors, *Computer Aided Verification*, volume 2404 of *LNCS*. Springer, March 2002.

- 2. E. M. Clarke, O. Grumberg, and D. Peled. *Model Checking*. The MIT Press, 1999.

- 3. E. M. Clarke, Orna Grumberg, Somesh Jha, Yuan Lu, and Helmut Veith. Counterexample-guided abstraction refinement. In Allen Emerson and A. Prasad Sistla, editors, *Computer Aided Verification (CAV'00)*, volume 1855 of *LNCS*, pages 154–169. Springer, 2000.

- Willem-Paul de Roever, Frank de Boer, Ulrich Hannemann, Jozef Hooman, Yassine Lakhnech, Mannes Poel, and Job Zwiers. Concurrency Verification: Introduction to Compositional and Noncompositional Methods. CUP, 2001.

- Dino Distefano, Peter O'Hearn, and Hongseok Yang. A local shape analysis based on separation logic. In Holger Hermanns and Jens Palsberg, editors, TACAS, volume 3920 of LNCS, pages 287–302. Springer, 2006.

- Alexey Gotsman, Byron Cook, Matthew Parkinson, and Viktor Vafeiadis. Proving liveness properties of non-blocking data structures. Submitted to POPL 2008.

- S. Graf and H. Saidi. Construction of abstract state graphs with PVS. In Orna Grumberg, editor, Proceedings of Computer Aided Verification (CAV '97), volume 1254 of LNCS, pages 72–83. Springer-Verlag, June 1997.

- Arie Gurfinkel, Ou Wei, and Marsha Chechik. Systematic construction of abstractions for modelchecking. In E. Allen Emerson and Kedar S. Namjoshi, editors, VMCAI, volume 3855 of LNCS, pages 381–397. Springer, 2006.

- 9. Thomas A. Henzinger, Ranjit Jhala, Rupak Majumdar, and Shaz Qadeer. Thread-modular abstraction refinement. In Warren A. Hunt Jr. and Fabio Somenzi, editors, *Computer-Aided Verification (CAV)*, volume 2725 of *LNCS*, pages 262–274. Springer, 2003.

- C. A. R. Hoare. An axiomatic basis for programming. Communications of the ACM, 12(10):576–580, 1969.

- 11. Cliff B. Jones. Specification and design of (parallel) programs. In *IFIP Congress*, pages 321–332, 1983

- K. L. McMillan. Verification of infinite state systems by compositional model checking. In Laurence Pierre and Thomas Kropf, editors, Correct Hardware Design and Verification Methods, volume 1703 of LNCS, pages 219–234. Springer, 1999.

- 13. K. L. McMillan. Parameterized verification of the FLASH cache coherence protocol by compositional model checking. In Tiziana Margaria and Thomas F. Melham, editors, *Proceedings of the 11th International Conference on Correct Hardware Design and Verification Methods*, volume 2144 of *LNCS*, pages 179–195. Springer, 2001.

- 14. Maged M. Michael and Michael L. Scott. Simple, fast, and practical non-blocking and blocking concurrent queue algorithms. In *PODC '96: Proceedings of the fifteenth annual ACM symposium on Principles of distributed computing*, pages 267–275. ACM Press, 1996.

- S. Owicki and D. Gries. Verifying properties of parallel programs: an axiomatic approach. Commun. ACM, 19(5):279–285, 1976.

- H. Saïdi. Model checking guided abstraction and analysis. In Jens Palsberg, editor, Proceedings of the 7th International Static Analysis Symposium, volume 1824 of LNCS, pages 377–396. Springer, July 2000.

- 17. Viktor Vafeiadis. Modular fine-grained concurrency verification. PhD thesis, University of Cambridge, 2007.

- Viktor Vafeiadis and Matthew J. Parkinson. A Marriage of Rely/Guarantee and Separation Logic. In CONCUR, volume 4037 of LNCS, pages 256–271, 2007.

# Compositional Proofs with Symbolic Execution

Simon Bäumler, Florian Nafz, Michael Balser, and Wolfgang Reif

Institut für Informatik – University of Augsburg Augsburg, Germany

**Abstract.** A proof method is described which combines compositional proofs of interleaved parallel programs with the intuitive and highly automatic strategy of symbolic execution. As logic we use an extended variant of Interval Temporal Logic that allows to formulate programs directly in the Simple Programming Language (SPL). The notation includes a complex interleaving operator. The interactive proof method we use for temporal properties is symbolic execution with induction. Here, we show how to combine this proof method with an assumption-guarantee approach to decompose proofs for safety properties. We demonstrate the application of this technique with a producer-channel-consumer case study. <sup>1</sup>

## 1 Introduction

Verification of concurrent systems is an important topic, as, in comparison to sequential programs, the system execution is much more complex. Validation of concurrent systems by testing is very difficult and often not feasible, as there are many more test cases and it is hard to reproduce tests. But also formal verification of concurrent systems is complicated, because reasoning over all possible execution traces tends to result in a huge state space which makes automatic and interactive verification very difficult.

To avoid reasoning over the complete concurrent system, a common technique is compositional reasoning. The basic idea of this technique is, to split the system into several subcomponents. Then, the overall property is proved only with corresponding properties of the subcomponents. This idea was first formulated by Dijkstra [1]. In compositional reasoning the proof is often done with a compositional theorem. Such a theorem provides a number of proof obligations, which have to be fulfilled, so that the overall property is valid. Ideally, these proof obligations contain only single subcomponents and properties of these subcomponents, but not the complete system itself. This results in several proofs of feasible size.

A common compositional proof technique is the assumption-guarantee paradigm, which was introduced by Jones [2] and by Misra & Chandy [3]. The basic idea of this paradigm is, that each component can make specific assumptions to its environment in order to guarantee a specific behavior. An overview of recent works on compositionality in general can be found e.g. in de Roever et. al. [4] or Furia [5].

This work has been funded by the DFG program INOPSYS II, under contract number Re 828/6-3.

Symbolic execution, on the other hand, is a successful technique for interactive verification of sequential programs (e.g. Dynamic Logic [6, 7]). It is a very intuitive strategy for programs as the proof advances step by step similar as most humans do it when trying to understand a program [8, 9]. Furthermore, it can be automated to a large extend. Balser [10] presented an ITL<sup>2</sup>-based logic with calculus that allows the symbolic execution of concurrent systems. This calculus was integrated into the interactive theorem prover KIV [12]. Arbitrary specification languages can be nested into this logic and thus making it unnecessary to translate a system specification into a special specification language for formal verification. Even more important is that the interleaving in this logic is compositional. That means, it is possible to replace a subcomponent with an abstraction of the component in a concurrent proof. While this feature simplifies concurrent proofs, it is still necessary to use symbolic execution on the whole parallel system in order to prove a property. A compositional theorem for this method would make it possible to prove properties of concurrent systems by reasoning only over single subcomponents at a time.

The goal of this paper is to present an assumption-guarantee rule for the logic presented in [10]. This would enable us to fully use the advantages of both techniques, compositional reasoning and symbolic execution, as well as the tool support, which is available for this logic.

We assume that the reader has at least basic knowledge in temporal logic and sequent calculus. The remainder of the paper is structured as follows: A short overview of our logic is given in Section 2. The compositional theorem we use is presented in Section 3, its application is shown in Section 4 on a producer-channel-consumer case study. Section 5 concludes the paper with related work and an outlook.

# 2 Temporal Logic Framework

In the following an informal overview over the used temporal logic calculus is given. The formal semantic is described in [13] and [10]. The calculus is integrated into the interactive theorem prover KIV. The temporal logic framework is a variant of ITL [11, 14] that is extended by explicitly including the behavior of the environment into each step. The basis for ITL are finite or infinite sequences  $\pi$  of valuations, which are called *intervals*. Valuations in  $\pi$  are called *states*. Each state is described by a first-order predicate logic formula over dynamic variables v, which also can be *primed* v' or *double primed* v''. The relation between v and v' is called *system transition*, whereas the relation between v' and v'' *environment transition*. The value of v'' in a state must be equal to the value of v in the next successive state. Thereby the system and the environment transition alternate. A selection of the supported temporal operators are:

<sup>&</sup>lt;sup>2</sup> Interval Temporal Logic, introduced by Moszkowski [11]

Further, programs are written in a SPL (Simple Programming Language) [15] like program syntax. The selection of the used SPL-operators are:

| x := t                    | assignment             | $\mathbf{await}\psi$                   | synchronization |

|---------------------------|------------------------|----------------------------------------|-----------------|

| $\varphi_1 \varphi_2$     | parallel assignment    | $\mathbf{while}\psi\mathbf{do}\varphi$ | loop            |

| $\varphi_1$ ; $\varphi_2$ | sequential composition |                                        |                 |

Semantically, a program describes a set of traces. Therefore, it is possible to embed programs into temporal formulas. This can be used for the parallel composition of programs with the tl-interleaving operator.

## 2.1 Symbolic Execution

A typical sequent in proofs about interleaved programs has the form  $P, \Gamma \vdash \Delta$ . Here, P is the interleaved program,  $\Gamma$  contains a temporal formula that describes the environment behavior and a first order formula for the current variable assignment, while  $\Delta$  contains the temporal property which has to be shown.

Symbolic execution on the following example sequent is done in two steps:

$$m:=m+1; <\operatorname{prog}>, \ \Box m'=m'', m=2\ \vdash\ \varDelta$$

First, all temporal and program formulas are rewritten to a so called first-next form, which encodes the transition to the next state in a predicate logic formula. For this, the following rule<sup>3</sup> is used:

$$\frac{m' = m + 1, \circ < \text{prog} >, \ m' = m'', \circ \Box m' = m'', \ m = 2 \vdash \Delta}{m := m + 1; < \text{prog} >, \ \Box m' = m'', \ m = 2 \vdash \Delta}$$

(prenex)

This rule separates propositions about the current state from propositions about all following states. So after application of *prenex* each formula is either a first-order formula, describing the first state in the trace or a temporal formula with a leading *next*-Operator, that describes the remaining trace.

Now it is possible to advance one step in the trace. In all first-order formulas, unprimed and primed variables are replaced by new static variables, while the double primed variables are replaced by their unprimed version. Further, all

<sup>&</sup>lt;sup>3</sup> Note that rules in the sequent calculus are read bottom-up, with the conclusion at the bottom and the corresponding proof obligations on the top part.

next-operators of temporal formulas are eliminated. In the example, this is done by the following rule-application:

$$\frac{M_1 = M_0 + 1, < \text{prog} >, M_1 = m', \square m' = m'', M_0 = 2 \vdash \Delta}{m' = m + 1, \circ < \text{prog} >, m' = m'', \circ \square m' = m'', m = 2 \vdash \Delta}$$

(tl-step)

This results in the following sequent after simplification:

$$< \text{prog} >$$

,  $\Box m' = m''$ ,  $m = 3 \vdash \Delta$

The rules for symbolic execution of formulas in the succedent are very similar. In KIV these rules, *prenex*, *tl-step* and simplification, are combined to a single complex rule called *step*.

## 2.2 Executing Interleaved Programs

To execute two interleaved formulas a first transition from one or the other formula is executed. After this, execution continues with interleaving the remaining formulas. For example, if there are two interleaved programs in the antecedent  $m := 1; \ldots || n := 2; \ldots, \Gamma \vdash \Delta$  this formula is executed by symbolically executing either program first. For this, the following rule is used:

$$m := 1; (\dots \parallel n := 2; \dots), \ \Gamma \vdash \Delta$$

$$n := 2; (m := 1; \dots \parallel \dots), \ \Gamma \vdash \Delta$$

$$m := 1; \dots \parallel n := 2; \dots, \ \Gamma \vdash \Delta$$

(interleaved left)

Furthermore the following equation holds for the interleaving operator

last

$$\parallel \phi \quad \leftrightarrow \quad \phi$$

which can be used to eliminate terminated programs. In the case that one of the programs is blocked, only the other program is executed.

One important feature of our interleaving operator is that it is compositional. This means, that the following rule can be applied:

$$\frac{\vdash \varphi_1 \to \varphi_2 \qquad \varphi_2 \parallel \psi, \ \Gamma \vdash \Delta}{\varphi_1 \parallel \psi, \ \Gamma \vdash \Delta} \tag{comp}$$

This feature is very important for the proofs of the theorems in chapter 3 and for abstraction in general.

Note, that our interleaving operator also supports features like fairness and blocking. These features and the general case, where the interleaving operator contains arbitrary temporal formulas, are also described in detail in [16] or [10].

## 2.3 Induction and Sequencing

The basic idea to proof safety properties is to advance in the interval until a valuation is reached that was considered earlier in the interval, so that a loop was executed. If it can be proven that the property is true before and during the loop so it is invariant, then the proof can be finished with an inductive argument. A special rule *start induction* is used to generate a suitable induction hypothesis.

Symbolic execution can lead to many paths, that have to be explored. Often two different paths lead to same configurations (two sequent have the same configuration if all temporal logic formulas are the same). To minimize the proof effort a rule called sequencing is used, that allows to close a open premise when there exists another premise with the same configuration, but with more general predicate logic formulas.

# 3 Compositional Theorem

Most assumption/guarantee based compositional proof techniques use a special operator similar to the "while-plus" operator  $\stackrel{+}{\Rightarrow}$  presented in [17]. Informally, the term  $A\stackrel{+}{\Rightarrow} G$  means, that if A holds up to step i, then G must hold up to step i+1. This operator enables the formulation that a component violates its guarantee G only after its assumption A is violated. It is needed to break the circularity of the used compositional rule.

Assumptions and guarantees can be formulated with propositional predicates over unprimed and primed variables (e.g. Cau and Collette [18]). We use the same approach, but for the assumptions we use predicates over primed and doubly primed variables. In this way it can be formalized which steps are allowed for the components and which steps are allowed for the environment. This also allows to use a standard TL operator **unless** as  $\stackrel{+}{\rightarrow}$  operator, i.e.:

$$A \stackrel{+}{\Rightarrow} G := G \text{ unless } (G \land \neg A)$$

With these preliminaries we are able to construct a compositional theorem:

## Theorem 1. If:

i. for all

$$i = 1, ..., n$$

:  $M_i \vdash A_i(v', v'') \xrightarrow{+} G_i(v, v')$

ii. for all  $i = 1, ..., n$ :  $G_i(v_1, v_2) \vdash G(v_1, v_2) \land \bigwedge_{j \in \{1...n\} \land j \neq i} A_j(v_1, v_2)$

iii. for all  $i = 1, ..., n$ :  $A_i(v_1, v_2) \land A_i(v_2, v_3) \vdash A_i(v_1, v_3)$

iv.  $A(v_1, v_2) \vdash \bigwedge_{i \in \{1...n\}} A_i(v_1, v_2)$

then:

$M_1 \parallel ... \parallel M_n \vdash A(v', v'') \xrightarrow{+} G(v, v')$

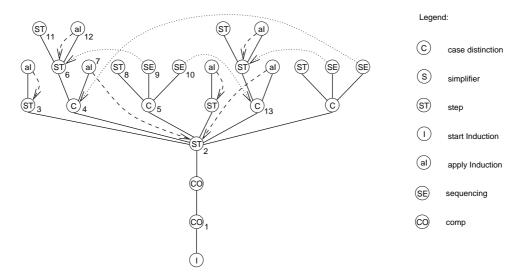

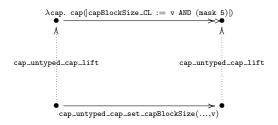

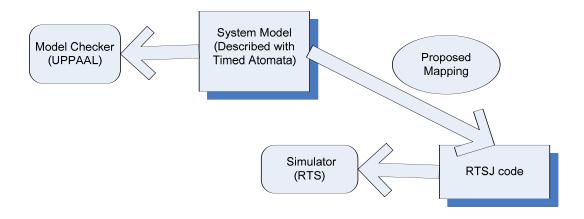

Fig. 1. Proof Graph for Theorem 1

Premise i is a temporal logic sequent while premise ii - iv contain only predicate logic formulas. These four proof obligations have the following informal meaning:

- i. All components must sustain their guarantee as long as the assumption holds. These are the only proof obligations which require a temporal logic proof.

- ii. The guarantee of each component preserves the global guarantee and does not violate the assumptions of all other components.

- iii. The assumptions of all components are transitive. With this property, the components assumption is preserved even if other components make several steps.

- iv. All component assumptions hold if the global assumption holds. Therefore, no component assumption is violated in the environment-step.

#### Proof (Outline).

The theorem was formally proven with the theorem prover KIV by using the ITL calculus described in section 2. As first step the proof for two components was done by symbolic execution of two abstract and interleaved components. The simplified proof graph<sup>4</sup> for this first step is depicted in figure 1. The premises *i-iv* of theorem 1 are used as lemmas for this proof. Premises *ii-iv* are applied by the KIV simplifier on predicate logic premises, which are all closed automatically by KIV. These simplifier steps are omitted in figure 1 for the sake of brevity.

The proof starts with the sequent  $M_1 \parallel M_2 \vdash A(v', v'') \xrightarrow{+} G(v, v')$  (node 1).  $M_1$  and  $M_2$  are abstract programs that have arbitrary behavior. At first both

<sup>&</sup>lt;sup>4</sup> The rules *apply Induction* and *Sequencing* refer both to another node in the proof tree, as explained in section 2. Therefore we depict proofs as graphs. The nodes that are referred by the rules *apply Induction* and *Sequencing* are represented by dashed arrows and pointed arrows respectively.

programs are replaced with their assumption-guarantee formulas of premise i of the theorem via the rule comp, so node 2 has the following sequent:  $A_1(v', v'') \stackrel{+}{\rightarrow} G_1(v, v') \parallel A_2(v', v'') \stackrel{+}{\rightarrow} G_2(v, v') \vdash A(v', v'') \stackrel{+}{\rightarrow} G(v, v')$  Here, the step rule is applied for symbolic execution. In the following, only the nodes 3-5 are described, as the other three premises of node 2 are symmetrical to these nodes.

In node 3 the first parallel component has terminated, so it must be shown that  $A_2(v',v'') \stackrel{+}{\to} G_2(v,v') \vdash A(v',v'') \stackrel{+}{\to} G(v,v')$  holds. This can by done using step and apply induction.

In node 4 the first component has made a normal step (i.e. it is neither terminated nor blocked). The case distinction discerns if  $A_1(v', v'')$  holds (node 7) in this step or not (node 6). Node 6 has the sequent  $\neg A_1(v', v'') \parallel A_2(v', v'') \stackrel{+}{\rightarrow} G_2(v, v') \vdash A(v', v'') \stackrel{+}{\rightarrow} G(v, v')$ . Here, in the next step there are three possibilities:

- The left component makes a step (not depicted in the graph, as it can be closed automatically by the simplifier).

- The right component makes a step and  $A_2(v', v'')$  is violated too (node 11). This can be closed automatically by another step.

- The right component makes a step and  $A_2(v', v'')$  holds (node 12). This premise can be closed by induction.

Node 7 contains exactly the same sequence as node 2, therefore induction can be applied.

Node 5 treats the case if the left component is blocked. Here, three cases are possible:

- Both assumptions  $A_1(v', v'')$  and  $A_2(v', v'')$  are violated (node 8). This can be closed automatically via step rule.

- Only the assumption  $A_1(v', v'')$  is violated (node 9). This is the same case as in node 6, therefore sequencing can be applied.

- $A_1(v', v'')$  holds and the right component has made a step (node 10). This case is covered in node 13, therefore sequencing can be applied.

This proof can be extended to n components by induction over the number of components. The initial induction case for one component can be shown by another temporal induction (similar to node 3 in the proof above). The inductive step can be proved by using the proof for two components as lemma to reduce n components to n-1 components. Then the induction hypotheses can be applied.

Usually the construction of a modularization rule is very difficult because of mutual dependencies. One interesting thing in our framework is that symbolic execution and tool support can not only be used to prove the modularization theorem, it actually helps to find the correct premises for the rule. To do so, the proof is as above, but without using the premises ii-iv as lemmas (as we

want to find them at this point). Then we try to close all open premises that contain temporal logic formulas, which results in a similar proof graph as shown in figure 1, but with several additional open premises that contain only predicate logic sequents. So to find the correct premises for the modularization theorem are a minimal set of generic predicate logic formulas from which all open sequents can be shown. By this technique a semantic analysis of the parallel operator is not necessary.

Extended Modularization Rule While this first rule may be useful for very simple systems it must be improved to be usable for more complex cases. First, a variable initialization in the temporal logic proofs (obligations i) is needed. Second, applications of this first rule show, that the guarantees are often redundant. Especially it is often necessary to have an invariance property. This invariant can be used to express the relation between the initial state and all succeeding states. Similar techniques for these additions are used e.g. in [18].

So, using the additional predicates I(v) for the invariant, Init(v) for the initial values of the global system and a family of predicates  $Init_i(v)$  for the initial values for every system component leads to an extended version of the compositional rule:

# Theorem 2. If:

```

i. for all i = 1, ..., n:

M_i, I(v), Init_i(v) \vdash A_i(v', v'') \xrightarrow{+} G_i(v, v')

ii. for all i = 1, ..., n:

G_i(v_1, v_2) \land I(v_1) \vdash G(v_1, v_2) \land \bigwedge_{j \in \{1...n\} \land j \neq i} A_j(v_1, v_2) \land I(v_2)

iii. for all i = 1, ..., n:

A_i(v_1, v_2) \land A_i(v_2, v_3) \land I(v_1)) \vdash A_i(v_1, v_3)

iv. A(v_1, v_2) \land I(v_1) \vdash \bigwedge_{i \in \{1...n\}} A_i(v_1, v_2) \land I(v_2)

v. for all i = 1, ..., n:

A_i(v_1, v_2) \land I(v_1) \land Init_i(v_1) \vdash Init_i(v_2)

vi. Init(v_1) \vdash \bigwedge_{i \in \{1...n\}} Init_i(v_1) \land I(v_1)

then:

M_1 \parallel ... \parallel M_n, Init(v) \vdash A(v', v'') \xrightarrow{+} G(v, v')

```

The informal meaning of the proof obligation of this theorem are as follows:

- i. These obligations are mostly the same, except that we can now assume the invariant and the initial condition for the respective component in the antecedent.

- ii. iv. These obligations are mostly the same as in the previous rule, except that the predicate I can now be assumed in the antecedent. Also, we have to show in obligations ii. and iv., that the invariant is preserved by the guarantee of each component and the global assumption.

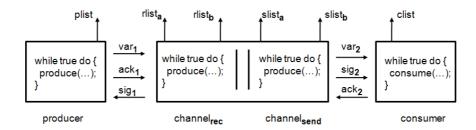

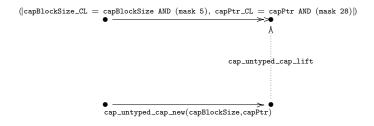

Fig. 2. Producer-Channel-Consumer (ProChaCon)

- v. Here it is shown, that the initial condition of a component is preserved by its assumption.

- vi. This obligation establishes the invariant and the initial conditions of the components.

Proof (Sketch). This theorem was also formally proven with KIV. The proof for theorem 2 and 1 are very similar. However, it must be shown for theorem 2 that  $Init_1(v)$ ,  $Init_2(v)$  and I(v) holds in the first state. To do that, a case distinction is used before the first step (node 2 in figure 1). The cases where one of the formulas  $Init_1(v)$ ,  $Init_2(v)$  and I(v) does not hold can be proved via step and induction, similar to node 8 in figure 1.

# 4 Case Study

In this section an example for applying the introduced theorem is presented. After an introduction of the producer-channel-consumer case study (short "ProChaCon") and its specification the formulation of the assumption-guarantee (short "AG") properties is described. The section closes with a description of the proofs of some of the proof obligations.

ProChaCon consists, as the name implies, of three interleaved components, depicted in Figure 2. Usually the values of the *producer* component are derived from an application or another component. For our task it is sufficient to generate them randomly. These values are sent using a classical two-way-handshake protocol [19] to the *channel* component. The *channel* is again divided into a receiver and a sender component. Both are connected through a buffer in which the incoming values are stored. The receiver is responsible to store the incoming values into the buffer and the senders job is to forward the buffered values. Thereto, the receiver attaches the incoming value to the buffer-list and the sender transmit the first value of the list as long as the buffer is not empty. The buffered values are transmitted to the *consumer* component, which processes the received values in an arbitrary way. The history of sent and received values is modeled by inserting history lists on certain points, e.g plist, also depicted in Figure 2. They

```

producer:

consumer:

begin

begin

while true do

while true do

await \operatorname{ch}_a.sig = \operatorname{ch}_a.ack;

await \operatorname{ch}_b.sig \neq \operatorname{ch}_b.ack;

a := [?];

b := ch_b.data;

ch_a := mkch(a, ch_a.sig, ch_a.ack);

ch_b := mkch(ch_b.data,

ch_a := mkch(ch_a.data,

\cosh_b.sig, \cosh_b.ack)

\neg \operatorname{ch}_a.\operatorname{sig}, \operatorname{ch}_a.\operatorname{ack})

clist := clist + b

plist := plist + a

end:

end:

channel:

begin

begin

1 while true do

while true do

await \operatorname{ch}_a.sig \neq \operatorname{ch}_a.ack;

await chbuf≠ [];

c := ch_a.data;

d := \text{chbuf.} first

\operatorname{ch}_a := mkch(\operatorname{ch}_a.data,

chbuf := chbuf.rest|

slist_a := slist_a + chbuf. first;

\operatorname{ch}_a.sig, \neg \operatorname{ch}_a.ack)

elist_a := elist_a + c;

await ch_b.sig = ch_b.ack;

chbuf := chbuf + c

\mathrm{ch}_b := mkch(\mathrm{d}, \, \mathrm{ch}_b.sig, \mathrm{ch}_b.ack);

\mathrm{ch}_b := mkch(\mathrm{ch}_b.data,

elist_b := elist_b + c

\neg \operatorname{ch}_b.sig, \operatorname{ch}_b.ack),

end;

```

Fig. 3. SPL Representation of ProdChaCon

are implemented as atomic assignments attached to the accordant program step. A specification of the components with SPL is shown below in Figure 4.

First some abbreviatory notations are described that will be used in the following. The sets of all used unprimed, primed and doubleprimed variables are denoted with V, V' and V''. As mentioned in the introduction a step consists of a system step and an environment step. In the following it is often necessary to express that a component only change a set of variables L. This is formulated by a frame assumption, which corresponds to the formula

$$\lceil L \rceil : \Leftrightarrow \bigwedge_{w \in V \setminus L} w' = w$$

which states that all program variables except L are unchanged. Here, L is a subset of V. Further, during the environment step some variables are unchanged. This is formulated with the following predicate

$$Unchanged_{env}(L) :\Leftrightarrow \bigwedge_{w \in L} w' = w''.$$

The verified property is "The list of received values is always a prefix of the list of the sent values". In other words, only values that have been sent are received and the order is unchanged. So for the overall guarantee the formula  $clist \sqsubseteq plist \rightarrow clist' \sqsubseteq plist'$  is used, where  $\sqsubseteq$  is the prefix operator. The global assumption states that all variables are unchanged by the environment. This leads to the following proof obligation for the complete system.

$$Unchanged_{env}(V) \xrightarrow{+} (clist \sqsubseteq plist \rightarrow clist' \sqsubseteq plist')$$

The system uses, as mentioned, a classical handshake to transmit values. Therefore, the involved components have to guarantee at least that they fulfill their part accurate. Sending components must guarantee that they transmit a value only if it is their turn and that the history-lists are updated in a correct way, formally expressed in  $Handshake_{send}$ .

```

Handshake_{send}(\operatorname{ch}, \operatorname{hlist}) :\Leftrightarrow

(\operatorname{ch}.sig \neq \operatorname{ch}.ack \rightarrow (\operatorname{ch} = \operatorname{ch}' \wedge \operatorname{hlist} = \operatorname{hlist}'))

\wedge (\operatorname{ch}.sig = \operatorname{ch}.ack \wedge \operatorname{ch}'.sig = \operatorname{ch}'.ack) \rightarrow \operatorname{hlist} = \operatorname{hlist}')

\wedge (\operatorname{ch}.sig = \operatorname{ch}.ack \wedge \operatorname{ch}'.sig \neq \operatorname{ch}'.ack) \rightarrow \operatorname{hlist} + \operatorname{ch}.data = \operatorname{hlist}'

```

Analogously  $Handshake_{receive}$  express that the receiver has to guarantee that values are only received if the handshake variables are unequal. The history list is updated if the handshake variables signalizing that a value was received successfully and the next value can be transmitted.

The producer component has to guarantee two things. First, that only internal variables and the handshake channel are changed. Second, that the handshake protocol is implemented correctly. The producers environment assumption  $A_1$  states that the environment does not change the internal variables as long as the producer could transmit a value. This is captured in  $G_1$  and  $A_1$ .

```

G_1(V, V') :\Leftrightarrow [ a, \operatorname{ch}_a, \operatorname{plist}] \wedge \operatorname{Handshake}_{send}(\operatorname{ch}_a, \operatorname{plist})

A_1(V', V'') :\Leftrightarrow \operatorname{Unchanged}_{env}(a, \operatorname{plist}) \wedge (\operatorname{ch}'_a.\operatorname{sig} = \operatorname{ch}'_a.\operatorname{ack} \to \operatorname{ch}'_a = \operatorname{ch}''_a))

```

The AG of the consumer can be formalized analogously:

$$G_4(V, V')$$

: $\Leftrightarrow$  [ b,  $\operatorname{ch}_b, \operatorname{clist}$ ]  $\wedge$  Handshake<sub>receive</sub>( $\operatorname{ch}_b, \operatorname{clist}$ )

$$A_4(V', V'') :\Leftrightarrow \operatorname{Unchanged}_{env}(\operatorname{b,clist}) \wedge (\operatorname{ch}'_b, \operatorname{sig} \neq \operatorname{ch}'_b, \operatorname{ack} \rightarrow \operatorname{ch}'_b = \operatorname{ch}''_b))$$

In a similar way the AGs for both channel components (channel<sub>rec</sub>, channel<sub>send</sub>) can be formalized. They need additional guarantees, because they pass the values via a buffer. That this is done correctly is formalized by the two guarantees  $Buffer_{in}$  and  $Buffer_{out}$ .

```

Buffer_{in}(buffer, hlist_{in}, value_{in}) :\Leftrightarrow

(hlist_{in} = hlist'_{in} \land buffer = buffer')

\lor ( hlist_{in} + value_{in} = hlist'_{in}

\land buffer + value_{in} = buffer')

```

$$Buffer_{out}(buffer, hlist_{out}) :\Leftrightarrow$$

$hlist_{out} + buffer = hlist'_{out} + buffer'$

The complete guarantee for channel<sub>rec</sub> consists of the statements that channel<sub>rec</sub> only changes its internal variables, that the receiver part of the handshake protocol is implemented in a correct way and that the component writes into the buffer correctly. Additionally, the component needs to guarantee that the prefix property also holds between both internal history lists. As assumption it can be presumed that the environment does not change the internal variables and the channel is not changed as long as channel<sub>rec</sub> can receive a value. That leads to the following AG.

The AG of the other channel component (channel<sub>send</sub>) can be formalized analogously with  $Buffer_{out}$  and  $Handshake_{send}$ .

The system always has to be in a correct state. In other words the buffers have to be empty or at least have to be filled in a non-conflicting way. This is expressed as an invariant. Theoretically, it is also possible to put all these into the AGs of the components, but it is more concise to have only local properties there. Therefore statements consisting of variables of more than one component are separated within an invariant, which expresses the connection of the components. First it states that depending on the handshake variables the two neighbor history lists are either equal or they differ in the value that is set in the data field.

```

I_1(V) :\Leftrightarrow (\operatorname{ch}_a.\operatorname{sig} = \operatorname{ch}_a.\operatorname{ack} \to \operatorname{elist}_a = \operatorname{plist})

\wedge (\operatorname{ch}_a.\operatorname{sig} \neq \operatorname{ch}_a.\operatorname{ack} \to \operatorname{elist}_a + \operatorname{ch}_a.\operatorname{data} = \operatorname{plist})

\wedge (\operatorname{ch}_b.\operatorname{sig} = \operatorname{ch}_b.\operatorname{ack} \to \operatorname{clist} = \operatorname{slist}_b)

\wedge (\operatorname{ch}_b.\operatorname{sig} \neq \operatorname{ch}_b.\operatorname{ack} \to \operatorname{clist} + \operatorname{ch}_b.\operatorname{data} = \operatorname{slist}_b)

```

For the channel it is stated that all values that were written into the buffer are either still in the buffer or were already send to the consumer component. This is formalised with  $slist + chbuf = elist_b$ . Additionally, some prefix properties are needed to show the overall property:

$$I_2(V) :\Leftrightarrow \operatorname{clist} \sqsubseteq \operatorname{slist}_b \wedge \operatorname{slist}_b \sqsubseteq \operatorname{slist}_a \wedge \operatorname{slist}_a \sqsubseteq \operatorname{elist}_b \wedge \operatorname{elist}_a \sqsubseteq \operatorname{elist}_a \wedge \operatorname{elist}_a \sqsubseteq \operatorname{plist}$$

The overall invariant I(V) is  $I_1(V) \wedge I_2(V)$ . The only needed initial information is, that the history-lists of both channel components are equal. This is formulated with init<sub>2</sub>  $\equiv$  (rlist<sub>a</sub> = rlist<sub>b</sub>) and init<sub>3</sub> $\equiv$ (slist<sub>a</sub> = slist<sub>b</sub>).

All proof obligations were formally proven with KIV. To give an impression of the proof effort for the components, we describe as example proof of the temporal logic proof obligation i for channel<sub>rec</sub>, which is as follows:

$$M_2, I(V), Init_2(V) \vdash A_2(V', V'') \xrightarrow{+} G_2(V, V')$$

The proof graph for this obligation is shown on the right side. In the beginning we start induction, explained in section 2.3. Initially the program is in position 1 (the numbers refer to the program of page 21). The *while*-loop could be evaluated, so that the program is in position 2. Executing the first step leads to a case distinction. Either the *await*-statement could be evaluated to *true* and the program is on position 3 or to *false* and the program remains

at position 2. In the second branch induction is applied, as the sequent has not changed. In the first branch further steps are executed till the program is again at position 1, which has been encountered before. In this case induction is applied and the proof is finished. The other three temporal logic proof obligations can be verified analogously without additional effort.

The proofs for the predicate logic proof obligations are straight forward. They start with a case distinction of the conjunctions on the right side of the sequence. All premises can then be closed by the simplifier of KIV automatically.

All in all the reuse of the AGs is very high, for example every component that uses a handshake protocol has to fulfill the handshake guarantees. Only the invariant depends on the property we want to verify. All proofs are simple and can be automated to a large extend. One reason for this is, that the components are no longer interleaved after modularization and so symbolic execution leads to only few new cases.

# 5 Related Work and Summary

In summary, we have presented a method how to use symbolic execution together with compositional reasoning. As basis for our work we use an ITL variant [10] that supports symbolic execution. Furthermore it provides a compositional interleaving operator, which allows us to formulate an assumption-guarantee theorem and prove it on syntactic level. The logic is fully integrated into the interactive theorem prover KIV and all proofs where done within this tool. A further advantage of our logic is the possibility to directly include multiple system description languages into the logic formalism, e.g. SPL which is used in this work. Other languages that were also successfully integrated into the logic are Statemate

and UML statecharts [20, 21] as well as Asbru, a language used for the verification of medical protocols [22]. The tool support and the syntactic nature of the theorem simplifies adaption of the theorem to particularities of these languages (e.g. to have better support for events in statecharts). The ability of symbolic execution of programs and statecharts supports intuitive and understandable proofs. To our knowledge this is the first work combining symbolic execution with compositional reasoning.

Our compositional theorem is inspired by the work of Abadi and Lamport [17]. They introduced the  $\stackrel{+}{\rightarrow}$  operator and a theorem which is suitable for safety and liveness properties. In comparison to our work they use conjunction for the composition of components. While conjunction is a more elementary operator than our interleaved operator, all components must be specified as stutter equivalent components. To achieve this, their components must be specified in a special formula in normal form, while we are able to specify the components directly in various description languages. Due to the inclusion of the double primed variables we have a stuttering mechanism directly in our semantics.

We use a similar technique for defining assumptions and guarantees as Cau and Collette [18]. Their theoretical work is more general as the described theorem can be adapted to state based as well as message based systems. Compared to this our focus was to provide a calculus and tool support for our technique.

Solanki et. al. [23] use compositional reasoning together with ITL. They use an AG variant that allows guarantees to be formulated in ITL. As tool they use (ana)Tempura [14, 11]. This technique is applied to a semantic web service description.

In a paper by Zwiers et. al. [24] invariants and preconditions are integrated in a compositional framework for concurrency. Joseph and Pandya [25] integrate invariants in a framework for total correctness. They use CSP-like distributed programs. Moszkowski [26] uses ITL for a compositional specification and proof technique. Further work about compositionality are e.g. Pnueli [27], Stirling [28] or Woodcock and Dickinson [29].

The producer-channel-consumer case study is a standard example for compositional reasoning. Pnueli [30] described a producer-channel-consumer example already 1986 formally with temporal logic. Abadi and Lamport [17] also used this example to illustrate how to specify components of concurrent systems. In their example they show that two N-element queues can be composed to an (2N+1)-element queue. Jonsson and Tsay [31] use the same example and property. The producer-channel-consumer example is also verified by Breitling et. al. [32], where streams for modelling the communicationare are used and Rock et. al. [33] in combination with TLA for specification.

Next steps are to apply our approach on liveness properties. First experiments in this direction were very promising. Another interesting topic would be to integrate an objectlevel  $\stackrel{+}{\rightarrow}$  operator similar to [17]. This would allow us

to use more complex assumption guarantee properties without abandoning the advantages of our approach: symbolic execution and tool support with various system description languages.

# References

- Dijkstra, E.W.: Solution of a problem in concurrent programming control. Commun. ACM 8(9) (1965) 569

- Jones, C.B.: Tentative steps toward a development method for interfering programs. ACM Trans. Program. Lang. Syst. 5(4) (1983) 596–619

- 3. Misra, J., Chandi, K.: Proofs of networks of processes. IEEE Transactions of Software Engineering (1981)

- 4. de Roever, W.P., et al.: Concurrency Verification: Introduction to Compositional and Noncompositional Methods. Cambridge University Press (2001)

- Furia, C.A.: A compositional world: a survey of recent works on compositionality in formal methods. Technical Report 2005.22, Dipartimento di Elettronica e Informazione, Politecnico di Milano (March 2005)

- 6. Harel, D.: Dynamic logic. In Gabbay, D., Guenther, F., eds.: Handbook of Philosophical Logic. Volume 2. Reidel (1984) 496–604

- 7. Heisel, M., Reif, W., Stephan, W.: A Dynamic Logic for Program Verification. In Meyer, A., Taitslin, M., eds.: Logical Foundations of Computer Science. LNCS 363, Berlin, Logic at Botik, Pereslavl-Zalessky, Russia, Springer (1989) 134–145

- 8. Burstall, R.M.: Program proving as hand simulation with a little induction. Information processing 74 (1974) 309–312

- 9. King, J.C.: Symbolic execution and program testing. Commun. ACM 19(7) (1976) 385–394

- Balser, M.: Verifying Concurrent Systems with Symbolic Execution. Shaker Verlag, Germany (2006)

- 11. Moszkowski, B.: Executing Temporal Logic Programs. Cambridge University Press, Cambridge (1986)

- Balser, M., Reif, W., Schellhorn, G., Stenzel, K.: KIV 3.0 for Provably Correct Systems. In Hutter,

D., Stephan, W., Traverso, P., Ullmann, M., eds.: Proc. Int. Wsh. Applied Formal Methods.

Volume 1641 of LNCS., Springer (1999) 330–337

- 13. Balser, M., Reif, W.: Interactive verification of concurrent systems using symbolic execution. Technical Report 2008-12, Universität Augsburg (2008)

- 14. Cau, A., Moszkowski, B., Zedan, H.: ITL Interval Temporal Logic. Software Technology Research Laboratory, SERCentre, De Montfort University, The Gateway, Leicester LE1 9BH, UK. (2002) http://www.cse.dmu.ac.uk/STRL/ITL/.

- 15. Manna, Z., Pnueli, A.: Temporal verification diagrams. LNCS 789 (1994) 726–765 Springer-Verlag.

- Balser, M., Reif, W.: An interval temporal logic with compositional interleaving. Technical Report 2008-11, Universität Augsburg (2008)

- 17. Abadi, M., Lamport, L.: Conjoining specifications. ACM Transactions on Programming Languages and Systems (1995)

- 18. Cau, A., Collette, P.: Parallel composition of assumption-commitment specifications: A unifying approach for shared variable and distributed message passing concurrency. Acta Inf. **33**(2) (1996) 153–176

- 19. Mead, C., Conway, L.: Introduction to VLSI systems. Addison-Wesley (1980)

- 20. Balser, M., Bäumler, S., Knapp, A., Reif, W., Thums, A.: Interactive verification of uml state machines. In Davies, J., Schulte, W., Barnett, M., eds.: Proc. 6th Int. Conf. of Formal Engineering Methods. Volume 3308 of LNCS., Springer (2004)

- 21. Thums, A.: Formale Fehlerbaumanalyse. PhD thesis, Universität Augsburg, Augsburg, Germany (2004) (in German).

- 22. Schmitt, J., Balser, M., Reif, W.: Asbru in KIV v2.1 a tutorial. Technical Report 2006-03, University of Augsburg (2006)

- 23. Solanki, M., Cau, A., Zedan, H.: Augmenting semantic web service descriptions with compositional specification. In Feldman, S.I., Uretsky, M., Najork, M., Wills, C.E., eds.: Proc. of 13th int. conference on World Wide Web, ACM (2004) 544–552

- 24. Zwiers, J., de Roever, W.P., van Emde Boas, P.: Compositionality and concurrent networks: Soundness and completeness of a proofsystem. In: Proc. of 12th Colloquium on Automata, Languages and Programming, Springer (1985) 509–519

- 25. Pandya, P.K., Joseph, M.: P-A logic: a compositional proof system for distributed programs. Distributed Computing 5(1) (1991) 37–54

- Moszkowski, B.: Compositional reasoning using interval temporal logic and tempura. LNCS 1536 (1996) 439–464 Springer-Verlag.

- 27. Pnueli, A.: In transition from global to modular temporal reasoning about programs. (1985) 123–144

- 28. Stirling, C.: A generalization of Owicki-Gries's Hoare logic for a concurrent while language. Theor. Comput. Sci. **58**(1-3) (1988) 347–359

- Woodcock, J.C.P., Dickinson, B.: Using VDM with rely and guarantee-conditions. Experiences from real projects. In: Proceedings of the 2nd VDM-Europe Symposium on VDM—The Way Ahead, New York, NY, USA, Springer-Verlag New York, Inc. (1988) 434–458

- 30. Pnueli, A.: Applications of temporal logic to the specification and verification of concurrent systems: A survey of current trends. LNCS 224, Berlin, Springer (1986)

- 31. Jonsson, B., Tsay, Y.K.: Assumption/guarantee specifications in linear-time temporal logic. Theoretical Computer Science, Vol. 167 (1996)

- 32. Breitling, M., Philipps, J.: Black box views of state machines. Technical Report TUM-I9916, Technische Univerität München (1999)

- 33. Rock, G., Stephan, W., Wolpers, A.: Modular reasoning about structured tla specifications. In Berghammer, R., Lakhnech, Y., eds.: Tool Support for System Specification, Development and Verification, Springer (1999)

# Specification Predicates with Explicit Dependency Information

Richard Bubel<sup>1</sup>, Reiner Hähnle<sup>1</sup>, and Peter H. Schmitt<sup>2</sup>

Dept. of Computer Science and Engg., Chalmers Univ. of Technology bubel|reiner@chalmers.se

Dept. of Computer Science, Univ. of Karlsruhe pschmitt@ira.uka.de

**Abstract.** Specifications of programs use auxiliary symbols to encapsulate concepts for a variety of reasons: readability, reusability, structuring and, in particular, for writing recursive definitions. The definition of these symbols often depends implicitly on the value of other locations such as fields that are not stated explicitly as arguments. These hidden dependencies make the verification process substantially more difficult. In this paper we develop a framework that makes dependency on locations explicit. This allows to define general simplification rules that avoid unfolding of predicate definitions in many cases. A number of non-trivial case studies show the usefulness of the concept.

## 1 Introduction

In program logics, especially in logics that target object-oriented languages, state-dependent predicates or functions are a convenient and often necessary concept used in specifications. They allow one to keep specifications concise and easy to read for humans. They are indispensable for the specification of inherently recursive properties such as reachability. Especially in first-order program logics there is no other alternative to specify properties recursively.

Such state-dependent predicate or function symbols, which are sometimes called *non-rigid symbols*, are not straightforward to use in verification practice, because they require special inference techniques. To unpack and transform their definition after every single state change would be extremely inefficient and must be avoided. As a first example, we consider the frequent specification task that stipulates an object array a to contain only non-null references. It is convenient to define a non-rigid unary predicate symbol on arrays:

$$\text{nonNullArray}(a) : \Leftrightarrow \forall i.a[i] \neq \text{null}$$

A typical desirable property in this context is that a simple assignment to a program variable j does not change the validity of nonNullArray. The formulation in Hoare logic [11] is in the first line below, the second line is the same in Dijkstra's weakest precondition calculus [9], and the third line reformulates it in Dynamic Logic [10]: