# The Clustered Multikernel: An Approach to Formal Verification of Multiprocessor Operating-System Kernels

Michael von Tessin

Ph.D.

March 2013

School of Computer Science and Engineering Faculty of Engineering

#### **PLEASE TYPE**

### THE UNIVERSITY OF NEW SOUTH WALES Thesis/Dissertation Sheet

Surname or Family name: von Tessin

First name: Michael

Other name/s:

Abbreviation for degree as given in the University calendar: PhD

School: Computer Science and Engineering

Faculty: Engineering

Title

The Clustered Multikernel: An Approach to Formal Verification of Multiprocessor Operating-System Kernels

#### Abstract 350 words maximum: (PLEASE TYPE)

The key software component of a computer system is the operating-system kernel. It always needs to be trusted because it runs in the CPU's privileged mode and therefore has access to all system components. Consequently, kernel correctness is crucial for secure, safe and reliable computer systems. Correctness can be improved by careful design, development and testing. However, this is not enough for kernels of high-assurance computer systems used in defence, aviation and the like.

Much stronger correctness guarantees can be obtained by formal verification of a kernel's implementation. In order to keep verification complexity at a manageable level, prior kernel verification research only targeted uniprocessor kernels. In other words, the current state of research restricts computer systems that require a verified kernel to running on one CPU/core. This is a problem because manufacturers are increasing computing power of their systems by adding more CPUs and cores.

In this thesis, we demonstrate that it is possible to extend a verified uniprocessor kernel to utilise multiple CPUs/cores and leverage the existing proofs to obtain a verified multiprocessor version of that kernel (under certain assumptions).

To this end, we introduce the *clustered multikernel*, a point in the design space of multiprocessor kernels. The main feature of this design is that it reduces concurrent data access to a minimum while offering a configurable trade-off between scalability and flexibility. Furthermore, we present a *conversion scheme* to convert a uniprocessor kernel into a clustered multikernel.

Based on this design, we contribute a *refinement lifting framework*, which lifts the converted kernel's functional-correctness proof such that it applies to the clustered-multikernel version. The support for handling the introduced concurrency is added to the existing verification framework in a non-intrusive way and accounts for TSO weak memory ordering.

We demonstrate the practicability of our approach by successfully applying it to seL4, a formally verified general-purpose microkernel. We show that this requires relatively low effort, compared to the kernel's initial verification.

All formal specifications and proofs are machine-checked in the theorem prover Isabelle/HOL.

#### Declaration relating to disposition of project thesis/dissertation

I hereby grant to the University of New South Wales or its agents the right to archive and to make available my thesis or dissertation in whole or in part in the University libraries in all forms of media, now or here after known, subject to the provisions of the Copyright Act 1968. I retain all property rights, such as patent rights. I also retain the right to use in future works (such as articles or books) all or part of this thesis or dissertation.

I also authorise University Microfilms to use the 350 word abstract of my thesis in Dissertation Abstracts International (this is applicable to doctoral theses only).

Signature

Witness

Date

The University recognises that there may be exceptional circumstances requiring restrictions on copying or conditions on use. Requests for restriction for a period of up to 2 years must be made in writing. Requests for a longer period of restriction may be considered in exceptional circumstances and require the approval of the Dean of Graduate Research.

FOR OFFICE USE ONLY

Date of completion of requirements for Award:

THIS SHEET IS TO BE GLUED TO THE INSIDE FRONT COVER OF THE THESIS

#### **Originality Statement**

'I hereby declare that this submission is my own work and to the best of my knowledge it contains no materials previously published or written by another person, or substantial proportions of material which have been accepted for the award of any other degree or diploma at UNSW or any other educational institution, except where due acknowledgement is made in the thesis. Any contribution made to the research by others, with whom I have worked at UNSW or elsewhere, is explicitly acknowledged in the thesis. I also declare that the intellectual content of this thesis is the product of my own work, except to the extent that assistance from others in the project's design and conception or in style, presentation and linguistic expression is acknowledged.'

Signature:

Date:

11.00 FEOT 28/03/2013

#### **Copyright Statement**

'I hereby grant the University of New South Wales or its agents the right to archive and to make available my thesis or dissertation in whole or part in the University libraries in all forms of media, now or here after known, subject to the provisions of the Copyright Act 1968. I retain all proprietary rights, such as patent rights. I also retain the right to use in future works (such as articles or books) all or part of this thesis or dissertation. I also authorise University Microfilms to use the 350 word abstract of my thesis in Dissertation Abstract International (this is applicable to doctoral theses only). I have either used no substantial portions of copyright material in my thesis or I have obtained permission to use copyright material; where permission has not been granted I have applied/will apply for a partial restriction of the digital copy of my thesis or dissertation.'

Signature: Muss Tools

Date: 28/03/2013

#### **Authenticity Statement**

'I certify that the Library deposit digital copy is a direct equivalent of the final officially approved version of my thesis. No emendation of content has occurred and if there are any minor variations in formatting, they are the result of the conversion to digital format.'

Signature: Moentos

Date: 28/03/2013

## **Abstract**

The key software component of a computer system is the operating-system kernel. It always needs to be trusted because it runs in the CPU's privileged mode and therefore has access to all system components. Consequently, kernel correctness is crucial for secure, safe and reliable computer systems. Correctness can be improved by careful design, development and testing. However, this is not enough for kernels of high-assurance computer systems used in defence, aviation and the like.

Much stronger correctness guarantees can be obtained by formal verification of a kernel's implementation. In order to keep verification complexity at a manageable level, prior kernel verification research only targeted uniprocessor kernels. In other words, the current state of research restricts computer systems that require a verified kernel to running on one CPU/core. This is a problem because manufacturers are increasing computing power of their systems by adding more CPUs and cores.

In this thesis, we demonstrate that it is possible to extend a verified uniprocessor kernel to utilise multiple CPUs/cores and leverage the existing proofs to obtain a verified multiprocessor version of that kernel (under certain assumptions).

To this end, we introduce the *clustered multikernel*, a point in the design space of multiprocessor kernels. The main feature of this design is that it reduces concurrent data access to a minimum while offering a configurable trade-off between scalability and flexibility. Furthermore, we present a *conversion scheme* to convert a uniprocessor kernel into a clustered multikernel.

Based on this design, we contribute a *refinement lifting framework*, which lifts the converted kernel's functional-correctness proof such that it applies to the clustered-multikernel version. The support for handling the introduced concurrency is added to the existing verification framework in a non-intrusive way and accounts for TSO weak memory ordering.

We demonstrate the practicability of our approach by successfully applying it to seL4, a formally verified general-purpose microkernel. We show that this requires relatively low effort, compared to the kernel's initial verification.

All formal specifications and proofs are machine-checked in the theorem prover Isabelle/HOL.

# Acknowledgements

I first want to thank my supervisor, Kevin Elphinstone, for giving me the opportunity to work on this PhD project and introducing me to the world of research. He taught me how to think scientifically and how to break down, analyse and present my work. His thorough feedback on my drafts helped me improve my writing greatly. He gave me a lot of freedom with regards to the focus and planning of my PhD and was always there when I asked him for feedback, advice and support.

I would also like to thank my professor, Gernot Heiser, for accepting me as a PhD student in such a prestigious research group. I enjoyed a highly inspiring and motivating yet relaxed work atmosphere. However, I would never have known the existence of this research group without Felix Rauch, who encouraged me to apply and helped me settle once I was there, and whom I want to thank for that.

Numerous people in our group have helped me over the past years and I want to take this opportunity to thank all of them. In particular, I am grateful to Gerwin Klein whom I could always ask for advice and feedback on the formal aspects of my work. I would also like to thank Thomas Sewell for helping me grapple with Isabelle/HOL proofs, and Rafal Kolanski for showing me all the necessary tricks to get my thesis typeset the way I wanted. Furthermore, I want to thank Leonid Ryzhyk and Nicholas FitzRoy-Dale for their valuable feedback on my thesis draft.

Finally, and most importantly, I want to thank my family. My utmost gratitude goes to my wife Gabi for her love and constant support throughout these years. Without it, and without her agreeing to move to Sydney, this thesis would not have been possible. I am also grateful to my daughters, Lena and Neva, whose joyful and lively nature always helped me switch off at the end of a working day.

# **Contents**

| 1 | Intr | oductio | on                                       | 1  |

|---|------|---------|------------------------------------------|----|

|   | 1.1  | Funct   | ional Correctness                        | 2  |

|   | 1.2  | Verific | cation Complexity                        | 2  |

|   | 1.3  | Proble  | em                                       | 3  |

|   | 1.4  | Appro   | oach                                     | 4  |

|   | 1.5  | Contr   | ibutions                                 | 4  |

|   | 1.6  | Overv   | riew                                     | 5  |

| 2 | Bacl | kgroun  | ad.                                      | 7  |

|   | 2.1  | _       | al Notation                              | 7  |

|   | 2.2  |         | ement Calculus                           | 10 |

|   | 2.3  |         | e Logic on State Monads                  | 12 |

|   |      | 2.3.1   | Non-Deterministic State Monads           | 12 |

|   |      | 2.3.2   | Hoare Logic                              | 14 |

|   | 2.4  | OS Ke   | ernel Architectures                      | 16 |

|   |      | 2.4.1   | Microkernels                             | 16 |

|   |      | 2.4.2   | Monolithic Kernels                       | 17 |

|   |      | 2.4.3   | Hybrid Kernels                           | 17 |

|   | 2.5  | The se  | eL4 Microkernel                          | 18 |

|   |      | 2.5.1   | Kernel Objects                           | 18 |

|   |      | 2.5.2   | Capabilities                             | 18 |

|   |      | 2.5.3   | Virtual Address Spaces                   | 19 |

|   |      | 2.5.4   | Threads                                  | 19 |

|   |      | 2.5.5   | Inter-Process Communication (IPC)        | 19 |

|   |      | 2.5.6   | Device Drivers and IRQs                  | 20 |

|   |      | 2.5.7   | Preemption                               | 20 |

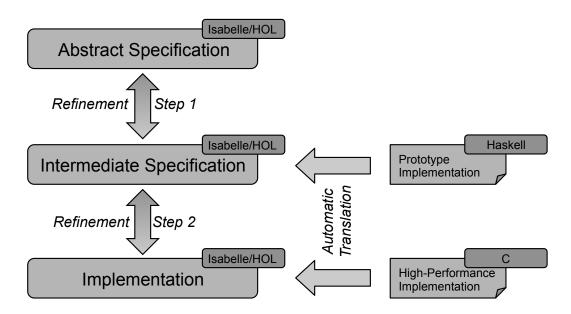

|   | 2.6  | Forma   | al Verification of seL4                  | 20 |

|   |      | 2.6.1   | Assumptions                              | 20 |

|   |      | 2.6.2   | Refinement Steps                         | 21 |

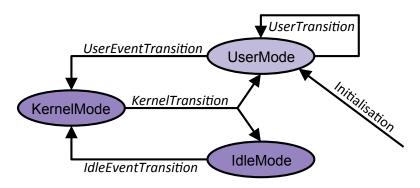

|   |      | 2.6.3   | Global Automaton                         | 22 |

|   |      | 2.6.4   | Refinement Theorem                       | 24 |

|   | 2.7  | Weak    | Memory Ordering                          | 25 |

|   |      | 2.7.1   | Total Store Order (TSO)                  | 25 |

|   |      | 2.7.2   | Abstracting Away Weak Memory Ordering    | 26 |

|   | 2.8  | Multi   | processor Kernel Designs                 | 26 |

|   |      | 2.8.1   | Challenges of Multiprocessor Programming | 26 |

|   |      | 2.8.2   | Synchronisation Mechanisms               | 27 |

|   |      | 2.8.3   | Design Choices                           | 27 |

|   |      | 2.8.4   | Design Requirements                      | 28 |

xii CONTENTS

| 3 | Rela | ited Wo                  | ork 29                           |  |  |  |  |  |

|---|------|--------------------------|----------------------------------|--|--|--|--|--|

|   | 3.1  | Multip                   | processor OSes                   |  |  |  |  |  |

|   |      | 3.1.1                    | Mach                             |  |  |  |  |  |

|   |      | 3.1.2                    | Raven 30                         |  |  |  |  |  |

|   |      | 3.1.3                    | QNX                              |  |  |  |  |  |

|   |      | 3.1.4                    | L4-based Kernels                 |  |  |  |  |  |

|   |      | 3.1.5                    | Corey                            |  |  |  |  |  |

|   |      | 3.1.6                    | Barrelfish                       |  |  |  |  |  |

|   |      | 3.1.7                    | Clustered OSes                   |  |  |  |  |  |

|   |      | 3.1.8                    | Analysis                         |  |  |  |  |  |

|   | 3.2  | OS Ve                    | rification                       |  |  |  |  |  |

|   |      | 3.2.1                    | Early Work                       |  |  |  |  |  |

|   |      | 3.2.2                    | VFiasco                          |  |  |  |  |  |

|   |      | 3.2.3                    | Coyotos                          |  |  |  |  |  |

|   |      | 3.2.4                    | Verisoft                         |  |  |  |  |  |

|   |      | 3.2.5                    | OLOS                             |  |  |  |  |  |

|   |      | 3.2.6                    | seL4/L4.verified                 |  |  |  |  |  |

|   |      | 3.2.7                    | Verve                            |  |  |  |  |  |

|   |      | 3.2.8                    | Analysis                         |  |  |  |  |  |

|   | 3.3  | Verific                  | cation of Multiprocessor Systems |  |  |  |  |  |

|   |      | 3.3.1                    | VCC                              |  |  |  |  |  |

|   |      | 3.3.2                    | Verisoft XT                      |  |  |  |  |  |

|   |      | 3.3.3                    | x86-TSO                          |  |  |  |  |  |

|   |      | 3.3.4                    | TSO Reduction Theorem            |  |  |  |  |  |

|   |      | 3.3.5                    | Analysis                         |  |  |  |  |  |

|   | 3.4  | Summ                     | nary                             |  |  |  |  |  |

| 4 |      |                          |                                  |  |  |  |  |  |

| 4 |      | he Clustered Multikernel |                                  |  |  |  |  |  |

|   | 4.1  |                          | n Requirements                   |  |  |  |  |  |

|   | 4.2  |                          | kernel Design                    |  |  |  |  |  |

|   |      | 4.2.1                    | 1                                |  |  |  |  |  |

|   | 4.0  | 4.2.2                    | Practical Application            |  |  |  |  |  |

|   | 4.3  | _                        | ock Design                       |  |  |  |  |  |

|   |      | 4.3.1                    | Implications                     |  |  |  |  |  |

|   |      | 4.3.2                    | Practical Application            |  |  |  |  |  |

|   | 4.4  |                          | ered-Multikernel Design          |  |  |  |  |  |

|   |      | 4.4.1                    | Implications                     |  |  |  |  |  |

|   | 4 =  | 4.4.2                    | Practical Application            |  |  |  |  |  |

|   | 4.5  |                          | ersion Scheme and seL4::CMK      |  |  |  |  |  |

|   |      | 4.5.1                    | CPU Architecture                 |  |  |  |  |  |

|   |      | 4.5.2                    | Bootstrapping                    |  |  |  |  |  |

|   |      | 4.5.3                    | Conversion Scheme                |  |  |  |  |  |

|   |      | 4.5.4                    | Static Node-Local Kernel Data    |  |  |  |  |  |

|   |      | 4.5.5                    | Lazy FPU Switching 61            |  |  |  |  |  |

|   |      | 4.5.6                    | Inter-Node Signalling            |  |  |  |  |  |

CONTENTS xiii

| 5 | Refi | nement | t Lifting Framework: Bootstrapping Phase | 63  |

|---|------|--------|------------------------------------------|-----|

|   | 5.1  | Chapte | er Overview                              | 64  |

|   | 5.2  | Multip | processor Execution Model                | 66  |

|   |      | 5.2.1  | Challenges                               | 66  |

|   |      | 5.2.2  | Formal TSO Model                         | 66  |

|   |      | 5.2.3  | Specifying Abstract Parallel Programs    | 71  |

|   |      | 5.2.4  | Memory/IPI Reordering                    | 73  |

|   |      | 5.2.5  | Advantages and Limitations               | 73  |

|   |      | 5.2.6  | Discussion of Extensibility              | 73  |

|   |      | 5.2.7  | Summary                                  | 74  |

|   | 5.3  | Seque  | ntial-Semantics Theorem                  | 74  |

|   |      | 5.3.1  | Definition                               | 75  |

|   |      | 5.3.2  | Summary                                  | 77  |

|   | 5.4  | Bootst | rapping Specification                    | 77  |

|   |      | 5.4.1  | Bootstrapping Part 1                     | 78  |

|   |      | 5.4.2  | Bootstrapping Part 2                     | 85  |

|   |      | 5.4.3  | Discussion                               | 86  |

|   |      | 5.4.4  | Summary                                  | 87  |

|   | 5.5  | Kernel | l-Memory-Sequential-Access Theorem       | 87  |

|   |      | 5.5.1  | Definition                               | 88  |

|   |      | 5.5.2  | Summary                                  | 88  |

|   | 5.6  | Interm | nediate Conclusion                       | 88  |

|   | 5.7  | Kernel | I Isolation Theorem                      | 89  |

|   |      | 5.7.1  | Definition                               | 89  |

|   |      | 5.7.2  | Connection to the Runtime Phase          | 90  |

|   |      | 5.7.3  | Summary                                  | 90  |

|   | 5.8  | User-L | Level Theorems                           | 91  |

|   |      | 5.8.1  | Definition                               | 91  |

|   |      | 5.8.2  | Summary                                  | 92  |

|   | 5.9  | Conne  | ection to L4.verified Proofs             | 92  |

|   |      | 5.9.1  | Node Isolation at Runtime                | 94  |

|   |      | 5.9.2  | Proof                                    | 95  |

|   |      | 5.9.3  | Discussion                               | 95  |

|   |      | 5.9.4  | Summary                                  | 95  |

|   | 5.10 | Multik | kernel Refinement Theorem                | 96  |

|   | 5.11 | Assun  | nptions and Limitations                  | 98  |

|   |      | 5.11.1 | Compiler/Boot Loader                     | 98  |

|   |      | 5.11.2 | Overapproximation                        | 98  |

|   |      | 5.11.3 | Missing Correspondence Proofs            | 99  |

|   | 5.12 | Proofs |                                          | 99  |

|   |      | 5.12.1 | Sequential-Semantics Theorem             | 99  |

|   |      | 5.12.2 | Kernel-Memory-Sequential-Access Theorem  | 103 |

|   |      |        | Kernel Isolation Theorem                 | 106 |

|   |      | 5.12.4 | User-Level Theorems                      | 108 |

|   |      | 5.12.5 | Summary                                  | 108 |

|   | 5.13 | Conclu | usion                                    | 109 |

*xiv* CONTENTS

| 6 | Refi | nemen   | t Lifting Framework: Runtime Phase                                | 111 |

|---|------|---------|-------------------------------------------------------------------|-----|

|   | 6.1  | Chapt   | rer Overview                                                      | 112 |

|   | 6.2  | Lifting | g Operation/Theorems                                              | 112 |

|   |      | 6.2.1   | Lifting Operation                                                 | 113 |

|   |      | 6.2.2   | Refinement Lifting Theorem                                        | 115 |

|   |      | 6.2.3   | Invariant Lifting Theorem                                         | 116 |

|   |      | 6.2.4   | Assumptions                                                       | 117 |

|   |      | 6.2.5   | Summary                                                           | 117 |

|   | 6.3  | Appli   | cation to seL4                                                    | 118 |

|   |      | 6.3.1   | Instantiation of Type Variables                                   | 118 |

|   |      | 6.3.2   | Parameterisation Functions                                        | 118 |

|   |      | 6.3.3   | ADTs of seL4::CMK                                                 | 119 |

|   |      | 6.3.4   | Proofs                                                            | 120 |

|   |      | 6.3.5   | Summary                                                           | 121 |

|   | 6.4  | Runni   | ing-Thread Problem                                                | 121 |

|   |      | 6.4.1   | Solution                                                          | 122 |

|   |      | 6.4.2   | Formal Implications                                               | 123 |

|   |      | 6.4.3   | Inter-Processor Interrupts (IPIs)                                 | 125 |

|   |      | 6.4.4   | Missing Correspondence Proofs                                     | 125 |

|   |      | 6.4.5   | Summary                                                           | 125 |

|   | 6.5  | Cluste  | ered-Multikernel Refinement Theorem                               | 125 |

|   | 6.6  | Assun   | nptions and Limitations                                           | 126 |

|   |      | 6.6.1   | Interleaving Semantics                                            | 126 |

|   |      | 6.6.2   | Big Lock                                                          | 127 |

|   |      | 6.6.3   | IPC Buffer                                                        | 127 |

|   | 6.7  | Concl   | usion                                                             | 130 |

| 7 | Con  | clusior | 1                                                                 | 131 |

|   | 7.1  | Future  | e Work                                                            | 132 |

|   |      | 7.1.1   | Missing Correspondence Proofs in First Refinement Step            | 132 |

|   |      | 7.1.2   | Second Refinement Step                                            | 132 |

|   |      | 7.1.3   | Enhancements to the TSO Model                                     | 132 |

|   |      | 7.1.4   | Resource Transfer Between Nodes                                   | 133 |

|   |      | 7.1.5   | Performance/Scalability Evaluation of the Clustered Multikernel . | 134 |

# **List of Tables**

| 5.1 | Size of seL4::CMK's Abstract Bootstrapping Specification | 86  |

|-----|----------------------------------------------------------|-----|

| 5.2 | Size of seL4::CMK's Bootstrapping C Code                 | 86  |

| 5.3 | Proof Size for Individual Invariants of Lemma 5.12.3     | 102 |

| 5.4 | The Kernel-Memory-Sequential-Access Theorem's Proof Size | 105 |

| 5.5 | Size of Bootstrapping Hoare-Triple Proofs                | 109 |

xvi LIST OF TABLES

# **List of Figures**

| 2.1 | L4.verified Overview                                         | 22  |

|-----|--------------------------------------------------------------|-----|

| 2.2 | Global Automaton of seL4                                     | 23  |

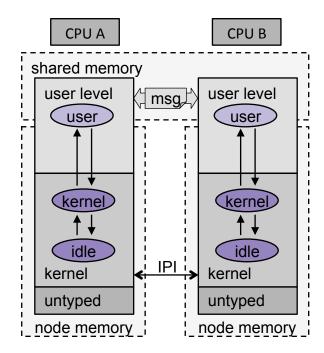

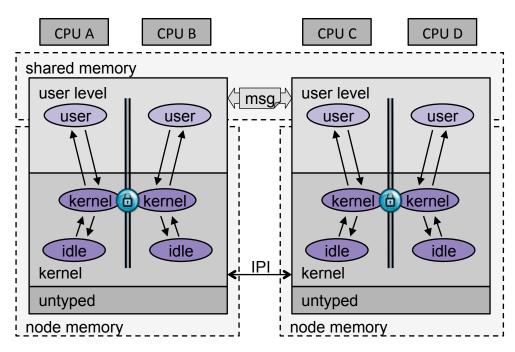

| 4.1 | Multikernel Design                                           | 47  |

| 4.2 | Big-Lock Design                                              | 49  |

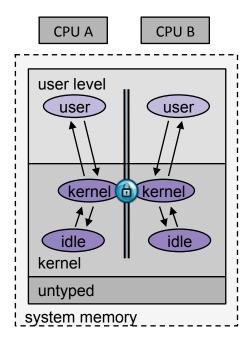

| 4.3 | The Clustered Multikernel                                    | 52  |

| 4.4 | The Multimed Distributed Database Design [SSGA11]            | 54  |

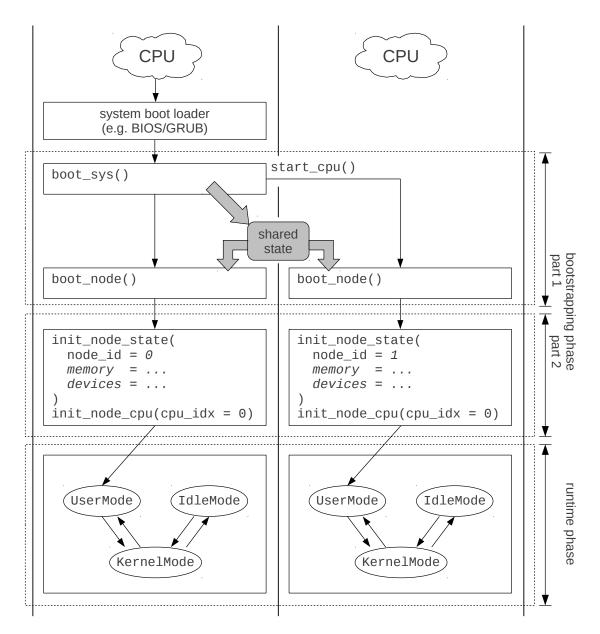

| 4.5 | Bootstrapping and Runtime Phases of seL4::CMK                | 56  |

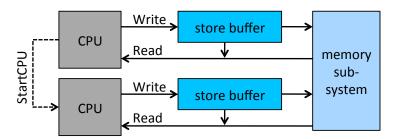

| 5.1 | TSO Model                                                    | 66  |

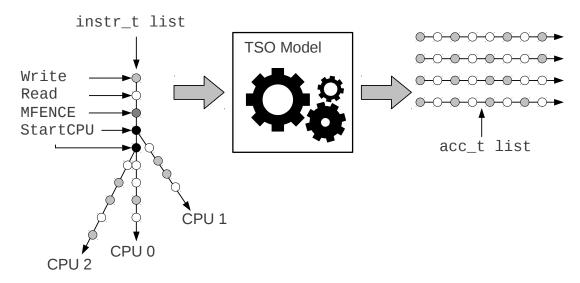

| 5.2 | Input and Output of the TSO Model                            | 68  |

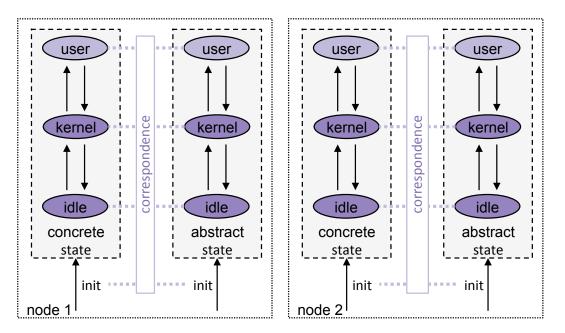

| 5.3 | Required Correspondence Proofs in the Multikernel Refinement | 97  |

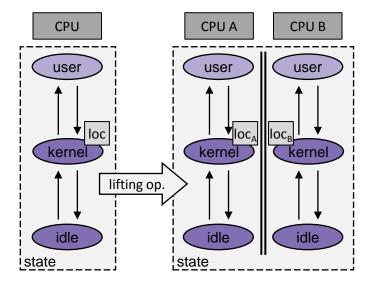

| 6.1 | Lifting into Parallel Composition                            | 112 |

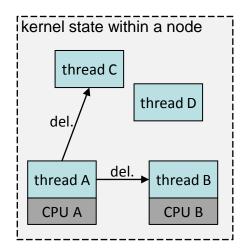

| 6.2 | Running-Thread Problem                                       | 122 |

xviii LIST OF FIGURES

# Chapter 1

# Introduction

The way we live today increasingly depends on computer systems. We routinely employ desktop computers to perform day-to-day tasks, we depend on embedded systems when driving a car or flying in an aircraft, and we indirectly use the servers of companies and governments that we interact with. We rely on these systems to be secure, safe and reliable.

Computer systems are built of hardware and software components. Security, safety and reliability of computer systems depend on the correctness of multiple components and on how these components interact with each other. For a desired security property, the subset of components that have to be trusted for the property to hold is called the *trusted computing base (TCB)*. Components outside the TCB are not critical and the security property still holds even if those components are faulty.

The key software component of a computer system is the operating-system (OS) kernel. It is always in the TCB because it runs in the CPU's privileged mode and therefore has access to all hardware components, which it multiplexes between software components. Therefore, OS-kernel correctness is crucial for secure, safe and reliable computer systems.

According to Hatton [Hat97], "good" software contains 6 bugs<sup>1</sup> per thousand lines of code (kLOC) on average and with "our best techniques" (such as careful design, development and testing) we can achieve 0.5–1 bugs per kLOC. However, this is not enough for kernels of high-assurance computer systems used—for example—in defence, aviation and the like.

Much stronger correctness guarantees can be obtained by formally verifying the correctness of a kernel's implementation. The history of kernel verification starts in the 70s and 80s [NBF+80, WKP80, Bev89], but none of these early attempts "produced a realistic kernel with full implementation proofs" [Kle09]. In the years after 2000, the topic attracted new interest: Verifying a kernel was part of several verification projects [HT05, TWV08, SDN+04, DDW09, DSS09, KEH+09, YH10]. The largest verified kernel is seL4 [KEH+09], an 8700-LOC general-purpose microkernel, which was verified down to the implementation level. "Verified" means there is a *functional-correctness* proof saying that the implementation adheres to a formal specification of the desired functionality.

In order to bring verification complexity down to a manageable level, the kernels mentioned above have two things in common: First, they are relatively small, in the order of a few kLOC. Second, their designs avoid concurrency within the kernel because concurrent software is very hard to reason about, as we will see in Section 1.2.

In-kernel concurrency is typically introduced by (1) switching between multiple threads of execution (kernel threads, interrupt handlers) or (2) running code in parallel

<sup>&</sup>lt;sup>1</sup>A *bug* is a fault in the software as a result of a programming error. A bug can make the software behave in ways that were not intended (e.g. specified).

on multiple CPUs. The former can be overcome by making a kernel non-preemptible or event-based with well-defined preemption points. In order to deal with the latter, the kernels mentioned above are restricted to only support a single CPU (or core<sup>2</sup>).

In summary, the current state of research restricts high-assurance computer systems that require a verified kernel to running on one CPU. This is a problem because manufacturers are increasing the computing power of their systems by adding more CPUs and cores. The problem has existed in the server and desktop space for years and finds its way into the embedded world now.

Consequently, this thesis aims at developing an approach to formal verification of multiprocessor kernels.

#### 1.1 Functional Correctness

There is a plethora of verification properties that can be proved about programs. There are lower-level properties such as termination, correctness of assertions and absence of null-pointer dereferences, overflows or exceptions. On the other side of the spectrum, we have higher-level properties such as isolation, integrity and *functional correctness*.

The latter is a very powerful verification property. It is proved by *refinement*, in which the implementation of a program refines an abstract specification of the desired functionality. In other words, it is proved that the program's behaviour conforms to what is specified.<sup>3</sup>

Abstract specifications are much smaller and easier to understand then actual program code, which reduces the probability of bugs. Moreover, specification bugs can be eliminated by additional proofs on the abstract level. A property proved on the abstract level is transferred by refinement to the implementation level, i.e. we know that it also holds in the implementation. This applies to so called *safety hyperproperties* [CS08], which include higher-level properties such as isolation and integrity. Proving such properties on the abstract level requires an order of magnitude less effort than proving them directly on the implementation level [KMG<sup>+</sup>11].

#### 1.2 Verification Complexity

Formal verification frameworks are usually either based on a *model-checking* approach or a *theorem-proving* approach.

In model checking, the system is captured in a mathematical model with enumerable states and transitions. For a desired verification property, the framework then automatically explores all possible states (via transitions) in order to verify whether the property is satisfied in all of them. As such, the verification process is fully automatic once the model has been created. There are a variety of abstraction techniques in order to reduce the number of states that have to be checked. However, model checking still becomes intractable quickly for large state spaces. This is especially true if concurrency is involved because the number of states grows exponentially with the degree of parallelism. Model checking is often used for verifying correctness of protocols, e.g. cache coherence protocols implemented in hardware [PD97] or synchronisation protocols in software. As

<sup>&</sup>lt;sup>2</sup>Throughout this thesis, we use the term *CPU* to refer to the logical unit of execution, e.g. a unicore processor or a core within a multicore processor. As such, we also use the term *multiprocessor* instead of *multicore*, unless we explicitly need to distinguish between them.

<sup>&</sup>lt;sup>3</sup>Usually there are assumptions such as a correct compiler, correct inline-assembly code, correct verification framework etc. Sometimes, there are also additional intermediate specification levels.

1.3. PROBLEM 3

these protocols have a limited number of states, model checking is tractable even when concurrency is involved. In contrast, model checking of program code results in a much higher number of states to be checked, especially for large programs. If concurrency is added, model checking of such programs becomes intractable.

Theorem proving takes a different approach. First, models and verification properties can be defined in a more general logic, e.g. higher-order logic (HOL). This increases expressiveness and readability. Second, there is no need for modelled program state to be enumerable and the size of the state space is irrelevant. Furthermore, there are a variety of verification properties, such as functional correctness, that are very hard to express and prove with model checking and therefore require a theorem-proving approach. However, there is considerably less automation compared to model checking. Machine-assisted/checked theorem proving requires a proof engineer to provide creative input to guide the verification framework in finding a proof using deductive reasoning, which is a complex and time-consuming task. In case of concurrent-program verification, proof complexity increases sharply with the complexity of the synchronisation mechanisms used because the proof has to cover all conceptual scenarios that can arise from concurrent execution of the program code in question.

Examples of interactive theorem proving frameworks are *Isabelle/HOL* [NPW02] and *HOL4* [HOL]. There are also hybrid approaches such as automated first-order theorem proving. An example of such a verification framework is *VCC*, which we present in Section 3.3.1.

#### 1.3 Problem

In the last section, we explained why formal verification becomes intractable very quickly as soon as concurrency is involved. For this reason, past kernel verification projects avoided having to reason about concurrency. As a result, the current state of research restricts computer systems that require a verified kernel to running on one CPU.

In order to make multiprocessor kernel verification tractable, we need to develop a suitable verification framework and choose the right level of abstraction (machine model) to work with. The choice of the verification property to be proved impacts tractability as well. In the end, however, tractability primarily depends on the verification target itself, i.e. the kernel. In-kernel synchronisation and communication between CPUs have to be designed with utmost care. There is a delicate trade-off: A simple design aids tractability but may adversely affect performance and scalability while elaborate scalable kernel designs most likely make verification intractable.

We aim to solve the problem of intractability by carefully crafting a suitable multiprocessor kernel design. While trying to maximise tractability, we also take into account the design's expected performance and scalability.

Designing the entire verification target (kernel) from scratch seems to be a promising approach. However, verifying a general-purpose kernel down to implementation level requires a large effort, even when no concurrency is involved. The verification effort can also include the development of the verification framework. For example, proving functional correctness of the seL4 microkernel required 20 person years (py) of which 11 py were kernel-specific efforts [KEH<sup>+</sup>09]. The rest went into developing the verification framework, proof libraries etc. Aiming for a verified multiprocessor kernel, it is therefore desirable to leverage as much as possible from an existing kernel, its verification framework and proof.

#### 1.4 Approach

In this thesis, we aim to demonstrate that it is possible to extend a verified uniprocessor kernel to utilise multiple CPUs and leverage the existing proofs to obtain a verified multiprocessor version of that kernel. We want to show that it requires relatively low effort, compared to the kernel's initial verification.

To this end, we introduce the *clustered multikernel*, a point in the design space of multiprocessor kernels. The main feature of this design is that it reduces concurrent data access to a minimum while offering a configurable trade-off between scalability and flexibility. This is possible by confining the required concurrent data accesses such that reasoning about them can be decoupled from reasoning about the kernel's functionality. Furthermore, the design eases conversion of a uniprocessor kernel into a multiprocessor kernel. For this purpose, we present a *conversion scheme* to convert a uniprocessor kernel into a clustered multikernel.

The process of reusing an existing proof in a new context by adapting or extending it is called *lifting*. For example, a theorem about a kernel-internal function can be reused in a multiprocessor context if we prove that no concurrency is introduced for that particular function.

To do this, we contribute a formal *refinement lifting framework*, which exploits the clustered multikernel's design features, specifically the confined concurrent data access. This allows it to lift most of the uniprocessor kernel's refinement proof such that it applies to the clustered-multikernel version (under certain assumptions). The support for handling the confined concurrency is added to the existing verification framework in a non-intrusive way. The refinement lifting framework accounts for weak memory ordering exhibited by total-store-order (TSO) multiprocessor architectures.

To demonstrate the practicability of the conversion scheme and the refinement lifting framework, we report on our experience with applying them to the seL4 microkernel [KEH<sup>+</sup>09].

All formal specifications and proofs presented in this thesis are machine-checked and typeset in the interactive theorem prover Isabelle/HOL [NPW02].

#### 1.5 Contributions

The primary contribution of this thesis is an approach to retaining the formal guarantees of a verified uniprocessor kernel when converting it into a multiprocessor kernel. More specifically:

- We introduce the **clustered multikernel**, a point in the design space of multiprocessor kernels. This design reduces concurrent data access to a minimum while offering a configurable trade-off between scalability and flexibility. Furthermore, the design eases conversion of a uniprocessor kernel into a multiprocessor kernel.

- We present a conversion scheme to convert a uniprocessor kernel into a clustered multikernel.

- Our refinement lifting framework lifts the converted kernel's functional-correctness

proof such that it applies to the clustered-multikernel version, under certain assumptions.

- We identify these assumptions and substantiate them; most of them formally, some

of them informally.

1.6. OVERVIEW 5

• We report on our experience with applying the conversion scheme and the refinement lifting framework to the seL4 microkernel. One result of this process is seL4::CMK, a proof-of-concept clustered-multikernel implementation of seL4.

• We identify the limitations of our approach and elaborate on how they can be overcome in future work.

The work presented in this thesis is solely the author's work. Contributions by others are clearly identified as such.

#### 1.6 Overview

The thesis is organised as follows: Chapter 2 summarises the background necessary to understand the remainder of this thesis. In Chapter 3, we present related work. Chapter 4 introduces the concept of the clustered multikernel, presents the conversion scheme and seL4::CMK. The main contribution of this thesis—the refinement lifting framework—is described in Chapter 5 and Chapter 6. Finally, we conclude and talk about future work in Chapter 7.

# **Chapter 2**

# Background

In this chapter, we summarise the background necessary to understand the remainder of this thesis. First, Section 2.1 introduces terminology and formal notation that will be used in definitions, lemmas and theorems. In Section 2.2, we present the refinement calculus that is the foundation of seL4's functional-correctness proof and of the refinement lifting framework contributed by this thesis. Section 2.3 introduces the concept of state monads, which are used for abstract specifications in seL4 and in this thesis.

In Section 2.4, we elaborate on OS kernel architectures (such as the *microkernel*), after which we present the seL4 microkernel in Section 2.5 and its formal verification in Section 2.6.

The last two sections cover general multiprocessor knowledge: Section 2.7 provides the necessary background about weak memory ordering, while Section 2.8 elaborates on the challenges of multiprocessor kernel programming, on common synchronisation mechanisms and multiprocessor design choices.

#### 2.1 Formal Notation

This section gives an overview of the Isabelle/HOL [NPW02] notation used in this thesis.

**Lemmas/Theorems** In Isabelle, lemmas and theorems consist of a *goal* and zero or more *assumptions*. In the following example, P and Q are assumptions and  $P \land Q$  is the goal. Valid notations are:

$$P \implies Q \implies P \land Q$$

$\llbracket P; Q \rrbracket \implies P \land Q$   $\frac{P \qquad Q}{P \land Q}$

**Types** The notation x :: t means that term x is of type t. Definitions of new types are started with the Isabelle keyword types.

Isabelle also supports *type variables*, which are prefixed with an apostrophe (e.g.  $^{\prime}a$ ). Type variables enable the definition of generic types which can later be instantiated with specific types.

**Unit** The type *unit* has a single element (). It is normally used to instantiate type variables in case we do not require the instantiated type to carry any information. For example, we can use *unit* as type for return values of functions that do not return anything.

**Datatypes** Datatypes are types that contain different kinds of content depending on a *constructor*. For example: The type bool is a datatype with constructors True and False;

and natural numbers (nat) are defined as a recursive datatype with a constructor for the number o and a constructor for the *successor* of an existing nat:

```

datatype bool = True / False

datatype nat = 0 / Suc nat

```

**Option Types** An 'a option is a datatype with two constructors:

```

datatype 'a option = | 'a | / None

```

Hence, an 'a option either contains an element of type 'a or None. Note that 'a is a type variable and is normally instantiated with a specific type when using the option type. For example, we can define a variable as nat option, which means that it either holds a natural number or None.

The function the can be used to extract element x from option  $\lfloor x \rfloor$ . Note that the None returns an undefined value.

**Functions** The type  $a \Rightarrow r$  denotes a function with a parameter of type a and returning a value of type r. Function application is written as  $f \times y$ , which is equivalent to  $(f \times y) \cdot y$ .

Functions are usually defined using a single equation. However, it is also possible to use multiple equations, e.g. for defining recursive functions.

In order to instantiate function-parameter variables during function application, Isabelle uses *pattern matching*. This means that for functions that are defined with a single equation, the function parameters on the left hand side of the equation are usually variables that also appear on the right hand side. In this case, pattern matching is trivial. For functions defined with multiple equations, function parameters are normally (partially) instantiated in these equations. In such a case, Isabelle employs pattern matching in order to decide which equation is applicable for a particular function application. The *dummy* notation "\_" can be used to match anything.

Constructing functions within terms is possible by using the lambda notation (e.g.  $\lambda x$ . x + 1).

Isabelle functions are total. Partial functions are defined by using an option type as range. Either of the following syntax defines such a function:

```

'a \Rightarrow 'b option 'a \rightarrow 'b

```

An empty partial function can be written as empty, which is defined as  $\lambda_{-}$ . None. The domain of a partial function can be obtained by dom.

Isabelle supports *function updates*, which are written as f(x := y). In this example, the function f is updated such that for an input of x, it returns y. For other inputs, the result values of f are unchanged. For partial functions,  $f(x \mapsto y)$  can be used as an abbreviation for f(x := Some y).

**Pairs** A pair with members a and b is denoted by (a, b) ::  $a \times b$ . Its members can be accessed with the functions fst and snd, respectively.

**Tuples** Tuples are nested pairs, e.g. (a, b, c, d) ::  $'a \times 'b \times 'c \times 'd$  is internally represented as type  $'a \times ('b \times ('c \times 'd))$ .

**Sets** A set is a function from the element type to bool, i.e. defining an 'a set variable actually defines an 'a  $\Rightarrow bool$  variable. The empty set is written as  $\emptyset$  and the universal set

as UNIV. The image of a set S under function f is denoted by f  $\circ$  S. The Cartesian product of two sets is written as  $S \times T$ . The predicate finite tests whether a set is finite.

The syntax  $\{x...y\}$  can be used to specify a set that contains all members of an ordered type (e.g. nat) between and including x and y. The syntax  $\{x...\langle y\}$  returns the same set, except that y is not included.

**Collections** A collection is written as  $\{x \mid P \mid x\}$  and is a set in which each element satisfies predicate P.

**Lists** Another example of a recursive datatype is the type *list*. It has a constructor for the empty list and a constructor for prepending an element to an existing list:

```

datatype 'a list = [] | 'a · 'a list

```

Note that the constructors above are directly defined with their syntax: [] for the empty list and the dot notation for prepending to a list.

The syntax [a, b, c] creates a list containing the elements a, b and c in this order. The n'th element of a list can be directly obtained form a list xs with  $xs_{[n]}$ . Two lists xs and ys are concatenated by typing  $xs \ @ \ ys$ .

Isabelle provides several functions which facilitate working with lists:

```

hd :: 'a list \Rightarrow 'a

tl :: 'a list \Rightarrow 'a list

length :: 'a list \Rightarrow nat

set :: 'a list \Rightarrow 'a \Rightarrow bool

foldl :: ('a \Rightarrow 'b \Rightarrow 'a) \Rightarrow 'a \Rightarrow 'b list \Rightarrow 'a

map :: ('a \Rightarrow 'b) \Rightarrow 'a list \Rightarrow 'b list

filter :: ('a \Rightarrow bool) \Rightarrow 'a list \Rightarrow 'a list

```

The hd function returns the first element of a list while tl returns the remainder of the list. We can calculate the length of a list with length or use set to construct a set from the list's elements. We can reduce a list to one element by using fold! which repeatedly applies a function, and in each iteration, takes as arguments an element of the list and the result of the last iteration. The map function applies a function to each element of the list, while filter removes elements from a list which do not satisfy the predicate passed as first argument. Isabelle supports following syntax for filter:

```

[x \leftarrow xs. P x] = filter P xs

```

**Records** A record consists of named fields, each having an assigned type. Records can be initialised with the notation  $(|field_A = x, field_B = y, field_C = z|)$  etc. The term  $field_A$  R returns the value of  $field_A$  of record R. Changing the value of an existing record's field is possible with a record field update: The syntax  $R(|field_A| := x|)$  returns a record equal to R, except that  $field_A$  contains the new value x.

**Let Notation** The syntax let x = y in E returns the expression E with every occurrence of x replaced with y.

**Case Notation** For case distinction on datatypes, we can use the following syntax:

```

case x of None \Rightarrow 0 / |v| \Rightarrow v

```

In this example, the type of x is the option type. If x is None, the expression returns o. If x is  $\lfloor v \rfloor$ , the expression returns v. Pattern matching in the conditions is possible. The pattern " $\_$ " can be used to match any datatype constructor.

#### 2.2 Refinement Calculus

Functional correctness of seL4 is proved via *data refinement* [dRE98]. This refinement calculus is formalised in Isabelle as described in Cock et al. [CKS08]. In this section, we introduce the formalisation on the level of detail necessary to understand seL4's formal verification (Section 2.6) and the refinement lifting framework (Chapter 5 and Chapter 6).

On each level of abstraction in a refinement proof, the program in question is modelled as an *abstract data type (ADT)*, which consists of 3 functions operating on 3 basic types.

#### **Definition 2.2.1 (Abstract Data Type)**

```

record ('priv, 'obs, 'j) adt_t = Init :: 'priv \Rightarrow bool

Step :: 'j \Rightarrow 'priv \times 'priv \Rightarrow bool

Fin :: 'priv \Rightarrow 'obs

```

The *observable state* type 'obs needs to be the same on each abstraction level. It is the common representation of the program state that links all abstraction levels. The *private state* type 'priv is supposed to be different on each abstraction level. On lower levels, it tends to be more detailed than on higher levels. The type instantiated for 'j holds all *transitions* of the system, i.e. each member of this type represents one system transition. Thus, 'j is normally instantiated with a datatype, so each constructor represents a named transition.

The *initialisation function* Init returns a set of initial private states 'priv, which allows us to non-deterministically model how the program is bootstrapped. The Step function models the behaviour of the program while running. For each *transition* of type 'j, it returns the set of allowed *steps*, i.e. a relation between old and new private states. Finally, Fin projects the private state space into the observable one.

Execution of a program (represented as an ADT) is defined as follows.

#### **Definition 2.2.2 (Execution)**

```

steps :: ('j \Rightarrow 'priv \times 'priv \Rightarrow bool) \Rightarrow ('priv \Rightarrow bool) \Rightarrow 'j \ list \Rightarrow 'priv \Rightarrow bool

steps \delta \equiv \text{foldl} \ (\lambda S \ j. \ \delta \ j \ `` \ S)

execution :: ('priv, 'obs, 'j) \ adt_t \Rightarrow 'j \ list \Rightarrow 'obs \Rightarrow bool

execution A js \equiv \text{Fin A } \text{ `steps (Step A) (Init A) } js

```

The initialisation function Init A returns a set of private states S. For each transition J in the list J S, the set of states S is transformed by applying the relation returned by Step A J. Finally, Fin A projects the set of resulting private states into observable ones.

Refinement between an *abstract* program (ADT  $\triangle$ ) and a *concrete* program (ADT  $\triangle$ ) is defined as follows.

<sup>&</sup>lt;sup>1</sup>Note that the original formalisation [CKS08] is slightly more general: The Init function takes an observable state as parameter. This would enable an Init function to return different sets of initial private states depending on this parameter. However, as seL4 does not make use of this, it ignores the parameter. Therefore, we modified the formalisation slightly by dropping the parameter. Doing so had no impact on seL4's refinement statement and proof because we only removed a parameter that had been ignored before.

#### **Definition 2.2.3 (Refinement)**

```

op \sqsubseteq :: ('priv\_C, 'obs, 'j) \ adt\_t \Rightarrow ('priv\_A, 'obs, 'j) \ adt\_t \Rightarrow bool C \sqsubseteq A \equiv \forall js. execution C \ js \subseteq  execution A \ js

```

ADT C refines ADT A if, for all transition lists js, the resulting set of observable states of executing ADT C is a subset of executing ADT A.

Note that an important aspect of refinement is that it is transitive.

#### Theorem 2.2.4 (Transitive Refinement)

```

\llbracket C \sqsubset B; B \sqsubset A \rrbracket \implies C \sqsubset A

```

Refinement is commonly proved via *forward simulation* [dRE98], which is defined as follows.

#### **Definition 2.2.5 (Forward Simulation)**

```

fw_sim :: ('priv_A, 'obs, 'j) adt_t \Rightarrow ('priv_C, 'obs, 'j) \ adt_t \Rightarrow ('priv_A \times 'priv_C \Rightarrow bool) \Rightarrow bool fw_sim A C R \equiv Init C \subseteq R \stackrel{\cdot}{\cdot} Init A \wedge (\forall j. R O Step C j \subseteq Step A j O R) \wedge (\forall s s'. (s, s') \in R \longrightarrow Fin C s' = Fin A s) op \sqsubseteq_F :: ('priv_A, 'obs, 'j) \ adt_t \Rightarrow ('priv_C, 'obs, 'j) \ adt_t \Rightarrow bool C \sqsubseteq_F A \equiv \exists R. fw_sim A C R

```

In order to show that ADT c forward simulates ADT a, we have to define a *refinement relation* a which relates their private state spaces to each other. We must prove that the relation is established by Init and preserved by Step for all transitions a, and that Fin projects related private states into equal observable states. We call these proofs *correspondence proofs*.

**Theorem 2.2.6** Forward simulation implies refinement.

```

C \sqsubseteq_F A \Longrightarrow C \sqsubseteq A

```

In correspondence proofs, it is often essential that we can rely on invariants restricting the set of private states we have to cover in those proofs.

#### **Definition 2.2.7 (Invariance)**

```

op \models :: ('priv, 'obs, 'j) \ adt_t \Rightarrow ('priv \Rightarrow bool) \Rightarrow bool

A \models I \equiv Init \ A \subseteq I \land (\forall j. \ Step \ A \ j \ `` \ I \subseteq I)

```

The invariants I hold throughout execution of ADT A if they are established by Init and preserved by Step for all transitions j. We call these proofs *invariant proofs*.

#### **Definition 2.2.8 (Forward Simulation with Invariants)**

```

\begin{array}{lll} \text{fw\_sim\_inv} & :: \ ('priv\_A, \ 'obs, \ 'j) \ adt\_t \\ & \Rightarrow \ ('priv\_C, \ 'obs, \ 'j) \ adt\_t \\ & \Rightarrow \ ('priv\_A \times \ 'priv\_C \Rightarrow bool) \\ & \Rightarrow \ ('priv\_A \times \ 'priv\_C \Rightarrow bool) \Rightarrow bool \\ \text{fw\_sim\_inv} \ A \ C \ R \ I \equiv \text{Init} \ C \subseteq R \ '' \ \text{Init} \ A \wedge \\ & (\forall j. \ (R \cap I) \ O \ \text{Step} \ C \ j \subseteq \ \text{Step} \ A \ j \ O \ R) \ \wedge \\ & (\forall s \ s'. \ (s, \ s') \in R \cap I \longrightarrow \ \text{Fin} \ C \ s' = \ \text{Fin} \ A \ s) \end{array}

```

The definition is identical to Definition 2.2.5 of  $tw_sim$ , except that we restrict the set of private states according to the invariants  $\mathcal{I}$  for the Step and Fin clauses. It states that forward-simulation holds under the assumption that the invariants hold.

**Theorem 2.2.9** *Forward simulation with invariants implies forward simulation if the invariants hold in both ADTs.*

$$[A \models I_a; C \models I_c; \text{ fw\_sim\_inv } A C R (I_a \times I_c)] \implies C \sqsubseteq_F A$$

#### 2.3 Hoare Logic on State Monads

Recall from Section 2.2 that on each abstraction level of a refinement proof, the behaviour of the program in question is defined by the ADT's Init and Step functions. These functions define the program's behaviour by modifying the ADT's private state.

The goal of a specification is to model the behaviour of a program in a way that is more abstract than the implementation and therefore easier for humans to write, read and reason about. As such, it is desirable to have a way of specifying these functions that facilitates classical program reasoning. A very popular way of reasoning about program code is by using Hoare triples. Therefore, we want to be able to use them to reason about how a specific function modifies the ADT's private state. To this end, seL4 uses non-deterministic state monads for its specifications.

In programming, *state monads* provide a way of using an imperative programming style in a functional programming language. A state monad facilitates accessing a global program state from within the program's functions. Such *monadic functions* consist of a sequence of calls to other monadic functions with each of them accessing the monad state sequentially.

State monads are useful for program specifications for multiple reasons: For example, their model of computation is purely functional. As such, they can be formalised in higher-order logic (HOL) (and therefore in Isabelle/HOL) without assumptions or axiomatisations. Furthermore, the notion of a global program state enables reasoning about this state at the beginning and end of a monadic function, e.g. we can define Hoare triples whose pre- and postconditions talk about the program state.

In functional programming, state monads are usually deterministic because the programs are intended to be executed. In specifications, however, non-deterministic state monads have several advantages over deterministic ones (as we will see below).

In this section, we present the formalisation of Hoare logic on non-deterministic state monads, originally described in Cock et al. [CKS08]. This formalisation is used in the specifications and proofs of seL4. We focus on the information necessary to understand seL4's formal verification (Section 2.6) and the refinement lifting framework (Chapter 5 and Chapter 6).

#### 2.3.1 Non-Deterministic State Monads

The type of a non-deterministic state monad is defined as follows.

#### **Definition 2.3.1 (Non-Deterministic State Monad Type)**

types ('s, 'r) nondet\_monad = 's

$$\Rightarrow$$

('r  $\times$  's) set  $\times$  bool

A state monad takes the monad state (type 's) as sole argument and returns a pair. The right side of the pair (snd) is the *failure flag*<sup>2</sup> (type bool). The left side of the pair (fst) is a non-deterministic set of possible *results* of the monadic computation. A result is a pair of

<sup>&</sup>lt;sup>2</sup>The failure flag can be used to signal program failure. For example, the monadic library function fail always fails, while assert fails if a certain condition on the monad state is not met.

the return value of the function (type 'r) and the monad state at the end of the function (type 's).

As an example, a monadic function foo that operates on a monad state of type state and returns a natural number (type nat) is declared as:

```

foo :: (state, nat) nondet_monad

```

The *monadic computation* (or *monadic execution*) is defined by the following two fundamental monad functions, called *constructors*.

The bind constructor defines how two monadic functions f and g are put in sequence.

#### **Definition 2.3.2 (Bind Constructor)**

```

bind :: ('s, 'r1) nondet_monad \Rightarrow ('r1 \Rightarrow ('s, 'r2) nondet_monad) \Rightarrow ('s, 'r2) nondet_monad bind f g \equiv \lambda s. (\bigcup fst ' (\lambda (x, y). g x y) 'fst (f s), True \in snd ' (\lambda (x, y). g x y) 'fst (f s) \vee snd (f s))

```

The overall result is calculated by taking the set of all possible results of f, feeding each of them into g and calculating the union of g's results. The failure flag is set if it was set in either f or g.

The second constructor is the return function.

#### **Definition 2.3.3 (Return Constructor)**

```

return :: 'r \Rightarrow ('s, 'r) \text{ nondet\_monad}

return r \equiv \lambda s. (\{(r, s)\}, \text{ False})

```

It returns the specified value r without changing the monad state and without failing. To facilitate reading and writing of the monad state, the following accessor functions are provided.

#### **Definition 2.3.4 (Accessor Functions)**

```

get :: ('s, 's) nondet_monad

get \equiv \lambda s. ({(s, s)}, False)

gets :: ('s \Rightarrow 'r) \Rightarrow ('s, 'r) nondet_monad

gets f \equiv do \ s \leftarrow get; return (f s) od

put :: 's \Rightarrow ('s, unit) nondet_monad

put s \equiv \lambda_. ({((), s)}, False)

modify :: ('s \Rightarrow 's) \Rightarrow ('s, unit) nondet_monad

modify f \equiv do \ s \leftarrow get; put (f s) od

```

The function get returns the current monad state as a proper return value whereas gets applies a transformation function f before returning. This is useful, for example, if the monad state is a record and we only want to return one specific field. Neither get nor gets modify the monad state itself.

The function put sets the state given as argument as the new monad state, while modify is a combination of get and put. As parameter, it takes a simple state-modifier function f. Note that the return type unit models that a function has no return value.

None of the accessor functions presented above can fail (set the failure flag).

#### Do Notation

The gets and modify functions above are defined using the *do notation*. This notation is primarily a syntax for a recursive application of the bind constructor, which allows putting multiple monadic functions in sequence.

A program block is defined by an opening do and closing od token. In between, we can place calls to multiple monadic functions, separated by semicolons. Each semicolon represents the application of the bind constructor with its parameter f instantiated with the function before the semicolon and g instantiated with the remaining program after the semicolon. Thus, a program block with multiple semicolons represents a nested application of the bind constructor.

In order to handle return values, it is possible to prepend a left arrow to the monadic function call, which results in the return value of the function being available as local bound variable in the remainder of the program block. In the definition of modify, for example, the variable s contains the value returned by get and is available for put later. Internally, this variable is the first parameter of bind's function parameter g.

#### **Non-Deterministic Choice**

All monadic functions presented so far are deterministic. To help specifying a non-deterministic program, the following two monadic functions are provided.

#### **Definition 2.3.5 (Non-Deterministic Alternative Execution)**

```

alternative :: ('s, 'r) nondet_monad \Rightarrow ('s, 'r) nondet_monad \Rightarrow ('s, 'r) nondet_monad alternative f g \equiv \lambda s. (fst (f s) \cup fst (g s), snd (f s) \vee snd (g s))

```

This specifies that either monadic function f or g is executed. The failure flag is set if it is set by either f or g. The syntax  $f \sqcap g$  is an abbreviation for alternative f g.

Non-deterministic return values can be generated with the following non-deterministic variant of return.

#### **Definition 2.3.6 (Non-Deterministic Selection)**

```

select :: 'r \ set \Rightarrow ('s, \ 'r) \ nondet_monad

select A \equiv \lambda s. (A \times \{s\}, \ False)

```

The select function therefore returns any value that is a member of set A. The monad state is not changed and the failure flag is not set. Refer to Definition 5.4.23 for an example how select can be used.

#### 2.3.2 Hoare Logic

A Hoare triple over a monadic function f is defined as follows.

#### **Definition 2.3.7 (Hoare Triple)**

```

\{P\} f \{Q\} \equiv \forall s. P s \longrightarrow (\forall (r, s') \in fst (f s). Q r s')

```

P is a unary predicate over the monad state S while Q is a binary predicate over the return value S of S and the monad state S. The Hoare triple states that if S holds for the monad state before executing S, then S holds for the return value of S and the monad state after having executed S.

To facilitate reasoning about Hoare triples, a collection of basic rules (theorems) are defined for the constructors and accessor functions presented above.

#### Theorem 2.3.8 (Basic Rules)

In order to be able to apply these rules in a Hoare-triple proof, we need a way of weakening preconditions.

#### Theorem 2.3.9 (Weaken Precondition)

$$\frac{\{\!\{Q\}\!\} f \{\!\{R\}\!\} \qquad \forall s. \ P \ s \longrightarrow Q \ s}{\{\!\{P\}\!\} f \{\!\{R\}\!\}}$$

Instead of proving the Hoare triple with the precondition P, we can prove it with precondition Q if we prove that Q is weaker than P, i.e. P implies Q.

We now explain how to use the above rules to prove Hoare triples, with the example of proving the *weakest-precondition* rule for modify (which we presented before):

$$\{\lambda s. P () (f s)\}$$

modify  $f \{P\}$

In order to prove this Hoare triple, we first unfold the definition of modify. This results in the following proof goal:

```

\{\lambda s. P () (f s)\}\ do s \leftarrow \mathbf{get}; \quad \mathbf{put} (f s) \ od \ \{P\}\

```

If the unfolded function contains calls to functions we do not have rules for, we also unfold those functions' definitions. Alternatively, we define rules for those functions first.

Now we weaken the precondition by applying Theorem 2.3.9. This results in the following two subgoals to be proved:

```

\{?Q\}\ do\ s \leftarrow \mathsf{get}; \quad \mathsf{put}\ (f\ s)\ od\ \{P\}

P\ ()\ (f\ s)\ \imp \ ?Q\ s

```

Note that the precondition has been replaced with the schematic variable *2Q*. In Isabelle, schematic variables can be instantiated at any point in the proof. Normally, it is done by pattern matching when applying a rule.

We apply the bind rule to the first subgoal because bind is the outermost function in that Hoare triple (represented by the do notation). Applying this rule results in the first subgoal to be replaced with two new subgoals, one each for get and put. Applying their respective rules removes those subgoals and, at the same time, instantiates ?Q with  $\lambda s$ . P () (f s). This results in the following last subgoal:

$$P$$

() (f s)  $\Longrightarrow$   $P$  () (f s)

This a pure HOL formula without monad or Hoare-logic formalism. In our example, the final goal is trivial because the precondition of the Hoare triple we proved is in fact the weakest precondition. In other examples, this last goal can be more complex to prove.

In order to reduce manual proof work, the verification framework provides a *verification condition generator* (VCG). The VCG automates the steps described above, i.e. it automatically weakens preconditions and applies rules from a predefined rule set. Newly proved rules can be added to this set, which progressively extends the automation to higher levels of abstraction.

#### 2.4 OS Kernel Architectures

The purpose of this section is to give an introduction to common OS kernel architectures for readers not familiar with this topic.

By definition, an OS *kernel* comprises all OS code that runs in the CPU's privileged mode. All other OS code and the application code run at *user level*.

The basic architecture of an OS kernel generally falls into one of the following categories: (1) *microkernel*, or (2) *monolithic kernel*.

#### 2.4.1 Microkernels

In a microkernel-based OS, the kernel only implements OS functionality that *requires* running in the CPU's privileged mode. This usually comprises context switching, memory management and bottom-level interrupt handling. All other OS services are implemented as *servers* at user level. Typically, each server is implemented as a process, which runs in its own virtual address space. Examples of such servers are device drivers, file systems, network stacks, naming services and high-level process management. Hence, a microkernel-based OS is sometimes called *multiserver OS* [GJP<sup>+</sup>00].

All requests for OS services and all coordination between OS services requires *inter-process communication (IPC)*, which is provided by the microkernel. A simple OS service call requires two IPC transfers: one for the request and one for the response. Each IPC transfer requires two *CPU mode switches* (in and out of the kernel), and a *context switch* from the sender's address space to the receiver's address space. These are time-consuming operations on most CPU architectures. As a consequence, IPC is the most critical performance bottleneck in microkernel-based OSes [Lie93].

#### Advantages

In a microkernel-based OS, services run isolated from each other. If they have to communicate with each other, APIs and communication channels have to be explicitly defined. This requires well-defined interfaces between OS services, which reduces bug density and facilitates formal analysis.

The isolation also increases robustness of the OS because faults are contained within an OS service. A misbehaving service cannot crash the kernel or other services, it can only crash itself. It is possible to implement a *monitor* to detect this and restart crashed services [Her10]. For example, if the network device driver crashes, it can be restarted within a few milliseconds. While this might result in the loss of a few network packets, such an event will most likely not be noticed at application level.

A microkernel allows a minimal *trusted computing base (TCB)*. Remember that a system's TCB comprises all code that has to be trusted in order for a given security property to hold. Code outside the TCB cannot violate the security property. The OS kernel is always in the TCB because it runs in the CPU's privileged mode. However, OS services are only in the TCB if they are relevant for the security property in question. Microkernels therefore

facilitate OS designs that provide minimal TCBs for different security properties.

#### **Drawbacks**

The obvious problem with microkernel-based OSes is that they heavily use IPC, which is an inherent performance bottleneck. While it is possible to reduce IPC latency drastically with careful microkernel design and implementation [Lie93], the overhead of the numerous CPU mode switches and context switches will always be there.

#### 2.4.2 Monolithic Kernels

In contrast to microkernels, monolithic kernels run most OS services within the kernel, i.e. in the CPU's privileged mode. Therefore, coordination between OS services does not require any CPU mode switches or context switches. User-level processes are mainly used to run applications, which request OS services from the kernel directly via *system calls*. A system call only requires two CPU mode switches (in and out of the kernel) but no context switch. IPC in monolithic kernels is mainly used for communication between applications and is therefore a lot less critical to overall system performance than for microkernels.

The most widely used kernels nowadays (e.g. Windows, Linux, OS X, Unix) are monolithic.

#### Advantages

Monolithic kernels have a performance advantage over microkernels because they require fewer CPU mode switches and context switches to complete the same tasks. There is also more freedom in how OS services can interact with each other. The possibilities range from synchronous models such as direct function calls or variable accesses across OS services to asynchronous models in which OS services communicate via explicit messages. The latter model is similar to the one used in a microkernel-based OS. However, the communication can be implemented more efficiently because no CPU mode switches or context switches are necessary.

#### **Drawbacks**

Monolithic kernels are generally less robust than microkernels. If an OS service misbehaves, it can crash the entire system because it is not isolated from other OS services. In practice, the most problematic OS services are device drivers. Chou et al. [CYC+01] reports a three to seven times higher bug density in device-driver code than other system components. In a monolithic system, each of these bugs has a high potential of crashing the entire system.

From a security perspective, monolithic kernels have the drawback that the OS services within the kernel are always in the trusted computing base (TCB), even the ones that would not be relevant for the security property in question.

#### 2.4.3 Hybrid Kernels

There are kernels that do not strictly fall into one of the above categories. Such kernels are sometimes called *hybrid kernels*. They are a compromise between microkernels and monolithic kernels with some OS services implemented in the kernel and others implemented at user level. Normally, all performance-critical services are implemented in the kernel

(e.g. device drivers, timers) while the remaining services are implemented at user level (e.g. file systems, naming services).

It is also hard to draw an exact line between microkernels and hybrid kernels, or between hybrid kernels and monolithic kernels; and kernels sometimes cross these lines during their lifetimes. For example, *Mach* [ABB<sup>+</sup>86] started as a microkernel. In order to improve performance, more and more OS services were moved into the kernel. Over time, Mach became a hybrid kernel. Similarly, the Windows NT kernel started as a hybrid kernel. However, more and more OS services were moved into the kernel over time, mostly for performance reasons. Nowadays, the Windows kernel is considered a monolithic kernel.

#### 2.5 The seL4 Microkernel

In Chapter 5 and Chapter 6, we apply the refinement lifting framework to the seL4 microkernel. The current section provides the necessary background to readers not familiar with seL4 and its internals.

seL4 [EDE08] is a third-generation microkernel, loosely based on L4 [Lie95]. It provides virtual address spaces, threads, and inter-process communication (IPC). The access-control mechanism—influenced by EROS [SSF99], KeyKOS [Har85] and CAP [NW77]—is based on capabilities, which grant access to kernel objects. Its performance is comparable to previous high-performance L4 microkernels.

Initially, seL4 was implemented for ARMv6, which is the version that is formally verified. Today, unverified implementations exist for other ARM versions, for x86 and for x64.<sup>3</sup> There are plans to formally verify the x86 version, of which an executable intermediate specification has already been written in Haskell.

The verified version of seL4 comprises 8700 lines of C code and 600 lines of assembly code [KEH<sup>+</sup>09].

#### 2.5.1 Kernel Objects

Every type of dynamic kernel data structure is represented by a *kernel object* type. The kernel does not implicitly allocate memory for kernel objects. Instead, they need to be explicitly created from user level. For such an operation, the user needs to provide *untyped memory*, which the kernel then uses to store the kernel object's state. Untyped memory cannot be accessed directly by the user.

#### 2.5.2 Capabilities

A *capability* is a protected reference to a kernel object. A kernel object can only be used by a thread which possesses a capability to it. Most kernel object types have *methods* which operate on the object's state. They are executed by *invoking* a capability that references the kernel object in question.

For example, the user can invoke the *retype* method of an untyped-memory capability in order to create kernel objects within the untyped memory region covered by the capability.

Capabilities are stored in *CNodes*, which are kernel objects themselves.

Some kernel object types only have methods but no state. Their purpose is to provide methods that provide kernel functionality which is not directly associated with specific

$<sup>^{3}</sup>$ Throughout this thesis, we use the term x86 for the *IA-32* and *AMD32* architectures, and the term x64 for the *Intel 64* and *AMD64* architectures.

kernel state. Capabilities of such object types do not reference object instances (there are none). Instead, they convey the right to call the methods associated with the particular kernel object type.

# 2.5.3 Virtual Address Spaces

The seL4 kernel does not define the structure of virtual address spaces, i.e. virtual-address mappings are managed at user level. For example, a page fault triggers an exception message to be sent to the designated user-level *pager* thread of the address space. The pager implements the policy of how the page fault should be handled, e.g. which physical frame the page should be mapped to.

User-level frames are the only type of memory that can be directly accessed from user level. They are created from untyped memory at the user's request. Before they can be accessed, they need to be mapped into a virtual address space. Address spaces are constructed by creating and linking the necessary page-table objects. An address space is identified by a capability to its top-level page table.

#### 2.5.4 Threads