## vNUMA: Virtual Shared-Memory Multiprocessors

A thesis submitted to the School of Computer Science and Engineering at The University of New South Wales in fulfilment of the requirements for the degree of Doctor of Philosophy.

Matthew Chapman 2008

#### **Originality statement**

I hereby declare that this submission is my own work and to the best of my knowledge it contains no materials previously published or written by another person, or substantial proportions of material which have been accepted for the award of any other degree or diploma at UNSW or any other educational institution, except where due acknowledgement is made in the thesis. Any contribution made to the research by others, with whom I have worked at UNSW or elsewhere, is explicitly acknowledged in the thesis. I also declare that the intellectual content of this thesis is the product of my own work, except to the extent that assistance from others in the project's design and conception or in style, presentation and linguistic expression is acknowledged.

## Copyright statement

I hereby grant the University of New South Wales or its agents the right to archive and to make available my thesis or dissertation in whole or part in the University libraries in all forms of media, now or here after known, subject to the provisions of the Copyright Act 1968. I authorise University Microfilms to use the abstract of my thesis in Dissertation Abstract International. I retain all proprietary rights, such as patent rights. I also retain the right to use in future works (such as articles or books) all parts of this thesis or dissertation. I have used no substantial portions of third-party copyright material in this thesis.

## **Authenticity statement**

I certify that the Library deposit digital copy is a direct equivalent of the final officially approved version of my thesis. No emendation of content has occurred and if there are any minor variations in formatting, they are the result of the conversion to digital format.

## **Abstract**

Shared memory systems, such as SMP and ccNUMA topologies, simplify programming and administration. On the other hand, systems without hardware support for shared memory, such as clusters of commodity workstations, are commonly used due to cost and flexibility considerations.

In this thesis, virtualisation is proposed as a technique that can bridge the gap between these architectures. The resulting system, vNUMA, is a hypervisor with a unique feature: it provides the illusion of shared memory across separate nodes on a fast network. This allows a cluster of workstations to be transformed into a single shared memory multiprocessor, supporting existing operating systems and applications. Such an approach could also have applications for emerging highly-parallel architectures, allowing a shared memory programming model to be retained while reducing hardware complexity.

To build such a system, it is necessary to meld both a high-performance hypervisor and a high-performance distributed shared memory (DSM) system. This thesis addresses the challenges inherent in both of these tasks. First, designing an efficient hypervisor layer is considered; since vNUMA is implemented on the Itanium processor architecture, this is with particular reference to Itanium processor virtualisation. Then, novel DSM protocols are developed that allow SMP consistency models to be reproduced while providing better performance than a simple atomically-consistent DSM system. Finally, the system is evaluated, proving that it can provide good performance and compelling advantages for a variety of applications.

## **Publications**

Portions of this work have been published in the following articles:

## • Implementing transparent shared memory on clusters using virtual machines

Matthew Chapman and Gernot Heiser

Proceedings of the 2005 USENIX Technical Conference, Anaheim, CA, USA, April 2005

Introduces vNUMA concept and presents an early version of the system

#### • vNUMA: A Virtual Shared-Memory Multiprocessor

Matthew Chapman and Gernot Heiser

To appear in Proceedings of the 2009 USENIX Technical Conference Summarises the work in this thesis

#### • Itanium: a system implementor's tale

Charles Gray, Matthew Chapman, Peter Chubb, David Mosberger-Tang and Gernot Heiser

Proceedings of the 2005 USENIX Technical Conference, Anaheim, CA, USA, April 2005 (Best Student Paper Award)

Describes Itanium virtualisation challenges — Chapter 3 in this thesis

#### • Pre-virtualization: soft layering for virtual machines

Joshua LeVasseur, Volkmar Uhlig, Yaowei Yang, Matthew Chapman, Peter Chubb, Ben Leslie and Gernot Heiser

Proceedings of the 13th Asia-Pacific Computer Systems Architecture Conference, August 2008 (Best Paper Award)

Describes pre-virtualisation — Chapter 4 in this thesis

#### • [para]virtualisation without pain

Peter Chubb, Matthew Chapman and Myrto Zehnder Proceedings of the 8th Linux.Conf.Au, January 2007 Describes pre-virtualisation — Chapter 4 in this thesis

#### • Pre-virtualization: slashing the cost of virtualization

Joshua LeVasseur, Volkmar Uhlig, Matthew Chapman, Peter Chubb, Ben Leslie and Gernot Heiser

Technical Report PA005520, National ICT Australia, October 2005 Describes pre-virtualisation — Chapter 4 in this thesis

## **Acknowledgements**

This thesis would not have been completed without the encouragement and assistance of a number of people.

I am indebted to my supervisor, Professor Gernot Heiser, who stood behind me and motivated me to bring this work to fruition, as well as providing feedback on drafts of this thesis and the preceding papers. Similarly, I appreciate the valuable feedback and helpful advice of my co-supervisor, Dr Peter Chubb, as well as Dr Felix Rauch.

I would also like to take the opportunity to thank my fellow research students, particularly Ian Wienand, Charles Gray and Daniel Potts, who were always prepared to listen to my problems and discuss my solutions — despite, or perhaps due to, having theses of their own to worry about.

Finally, the pre-virtualisation idea that is used to minimise virtualisation overheads arose out of collaborative work with colleagues at the University of Karlsruhe, particularly Joshua LeVasseur and Volkmar Uhlig. However, the specific embodiment for the Itanium architecture is unique to this thesis.

## **Contents**

| 1 | Intr | oduction                     | 3  |

|---|------|------------------------------|----|

| Ι | Ita  | nium virtualisation          | 7  |

| 2 | Virt | ualisation                   | 11 |

|   | 2.1  | Full virtualisation          | 13 |

|   | 2.2  | Para-virtualisation          | 15 |

|   | 2.3  | Pre-virtualisation           | 17 |

|   | 2.4  | Type I vs Type II            | 17 |

| 3 | Itan | ium challenges               | 19 |

|   | 3.1  | Sensitive instructions       | 21 |

|   | 3.2  | Ring compression             | 25 |

|   | 3.3  | Hiding the VMM               | 26 |

|   | 3.4  | Register stack engine faults | 26 |

|   | 3.5  | Complex translation modes    | 29 |

| 4 | Pre- | virtualisation               | 31 |

|   | 4.1  | Mechanism                    | 31 |

|   | 4.2  | Challenges                   | 34 |

|   |      | 4.2.1 Scratch registers      | 34 |

|   |      | 4.2.2 Atomicity              | 35 |

|   |      | 4.2.3 IP-inspecting code     | 38 |

|   |      | 4.2.4 Code expansion         | 39 |

vi *CONTENTS*

| 5  | Hyp | ervisor | architecture                                 | 41 |

|----|-----|---------|----------------------------------------------|----|

|    | 5.1 | Usersp  | pace (Linux-on-Linux)                        | 41 |

|    |     | 5.1.1   | Address space conflicts                      | 43 |

|    |     | 5.1.2   | System call redirection                      | 45 |

|    |     | 5.1.3   | Other issues                                 | 46 |

|    | 5.2 | Standa  | alone                                        | 47 |

|    |     | 5.2.1   | Lightweight C environment                    | 47 |

|    |     | 5.2.2   | Memory management                            | 49 |

|    |     | 5.2.3   | Devices                                      | 57 |

| II | Tr  | anspa   | rent distribution                            | 59 |

| 6  | Sha | red mei | nory                                         | 63 |

|    | 6.1 | Early   | software DSM systems                         | 64 |

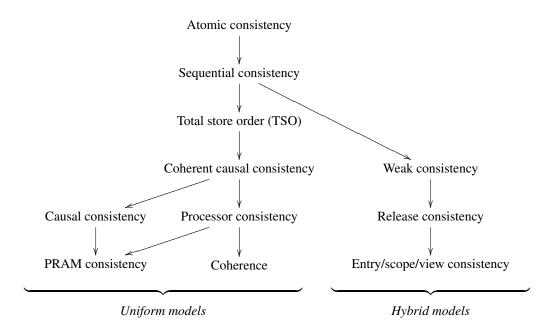

|    | 6.2 | Consis  | stency models                                | 66 |

|    |     | 6.2.1   | Atomic consistency (Linearisability)         | 68 |

|    |     | 6.2.2   | Sequential consistency (Sequentialisability) | 69 |

|    |     | 6.2.3   | Total store order (TSO)                      | 69 |

|    |     | 6.2.4   | PRAM consistency (FIFO consistency)          | 70 |

|    |     | 6.2.5   | Causal consistency                           | 70 |

|    |     | 6.2.6   | Coherence                                    | 70 |

|    |     | 6.2.7   | Weak consistency                             | 71 |

|    |     | 6.2.8   | Release consistency                          | 71 |

|    |     | 6.2.9   | Entry, scope and view-based consistency      | 72 |

|    | 6.3 | Later   | software DSM systems                         | 72 |

|    | 6.4 | Hardw   | ware shared-memory systems                   | 73 |

| 7  | The | vNUM    | A DSM system                                 | 77 |

|    | 7.1 | Integra | ation with hypervisor                        | 77 |

|    | 7.2 | Basic   | protocol                                     | 80 |

|    | 7.3 | Doubl   | e fault optimisation                         | 81 |

|    | 7.4 | Manag   | ger as preferred owner optimisation          | 82 |

|    | 7.5 | Thrasl  | ning avoidance                               | 83 |

| CC | ONTE       | NTS vii                            |

|----|------------|------------------------------------|

|    | 7.6        | Pseudocode                         |

| 8  | Perfo      | ormance challenges 89              |

|    | 8.1        | Addressing sparse accesses         |

|    | 8.2        | Write detection                    |

|    | 8.3        | Write propagation                  |

|    | 8.4        | Adaptive hybrid protocol           |

|    | 8.5        | Interaction with migration         |

|    | 8.6        | Coherence                          |

|    | 8.7        | Atomic operations                  |

|    | 8.8        | Write batching                     |

|    | 8.9        | Memory fences                      |

|    | 8.10       | Pseudocode                         |

| 9  | Othe       | er infrastructure 127              |

|    | 9.1        | Efficient inter-node communication |

|    | 9.2        | Inter-processor interrupts         |

|    | 9.3        | Distributing I/O                   |

|    | 9.4        | Bootstrap process                  |

| II | [ <b>E</b> | valuation 139                      |

| 10 | Meth       | nodology 143                       |

|    | 10.1       | Test environment                   |

|    | 10.2       | Analysis tools                     |

| 11 | Benc       | chmarks 147                        |

|    | 11.1       | HPC benchmarks                     |

|    | 11.2       | Compile benchmark                  |

|    | 11.3       | Database benchmark                 |

| 12 | Anal       | ysis of implementation choices 163 |

|    | 12.1       | Pre-virtualisation                 |

|    | 12.2       | DSM protocol                       |

| CONTENTS   |

|------------|

| 0011121110 |

|            |

| 13 | Conclusion |                        | 185 |

|----|------------|------------------------|-----|

|    | 12.2.7     | Transferring page data | 180 |

|    | 12.2.6     | Latency sensitivity    | 178 |

|    | 12.2.5     | Release detection      | 177 |

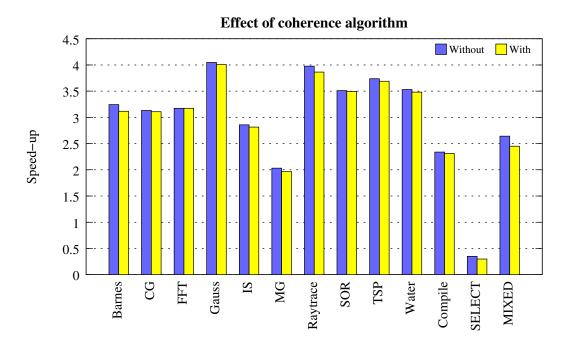

|    | 12.2.4     | Coherence algorithm    | 175 |

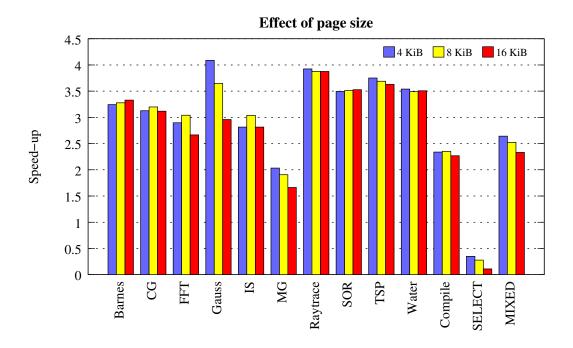

|    | 12.2.3     | Page size              | 174 |

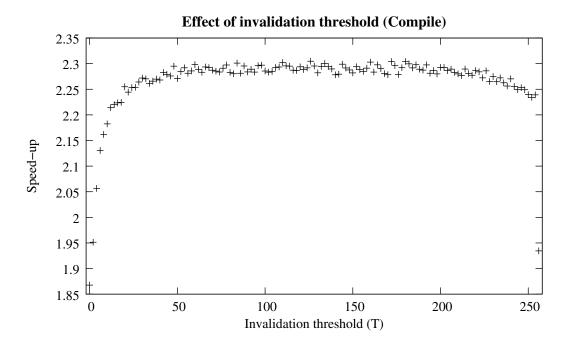

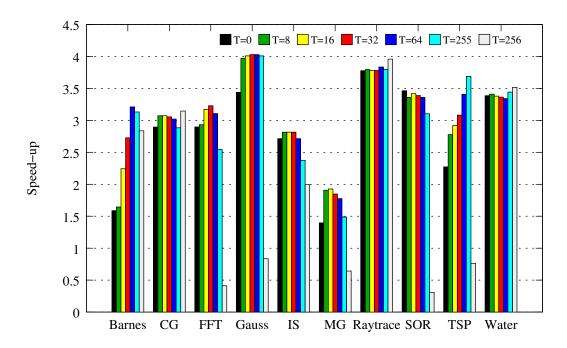

|    | 12.2.2     | Invalidation threshold | 171 |

|    | 12.2.1     | Protocol optimisations | 167 |

|    |            |                        |     |

## **List of Figures**

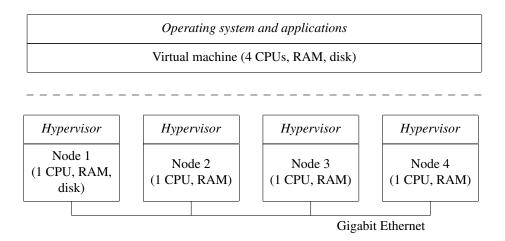

| 1.1 | Example vNUMA system                                                | 5   |

|-----|---------------------------------------------------------------------|-----|

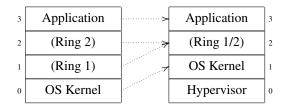

| 3.1 | Ring compression                                                    | 25  |

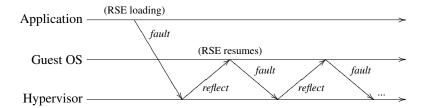

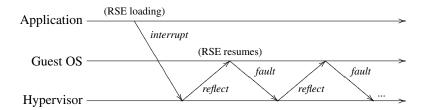

| 3.2 | Register stack engine virtualisation: problem and workaround        | 28  |

| 5.1 | Emulation of a privileged instruction                               | 42  |

| 5.2 | Relocating a guest kernel to avoid conflicting with a host kernel . | 43  |

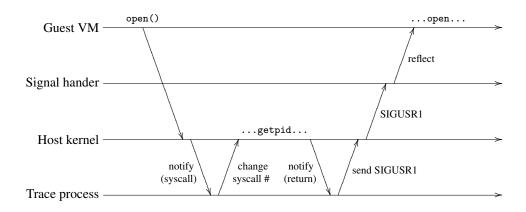

| 5.3 | System call reflection using ptrace facility                        | 46  |

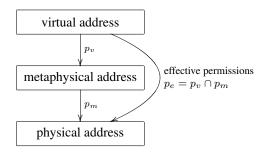

| 5.4 | Address translation layers                                          | 51  |

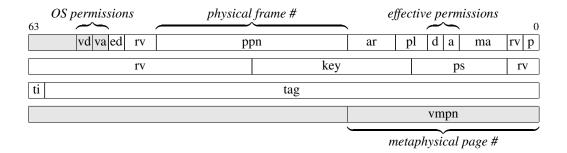

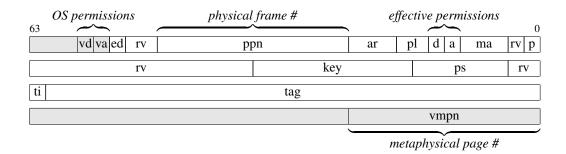

| 5.5 | Anatomy of a long-format page table entry                           | 54  |

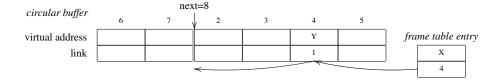

| 5.6 | Tracking inverse mappings                                           | 57  |

| 6.1 | Hierarchy of common consistency models                              | 67  |

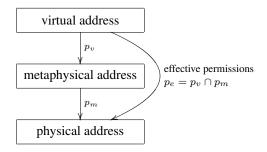

| 7.1 | Address translation layers                                          | 77  |

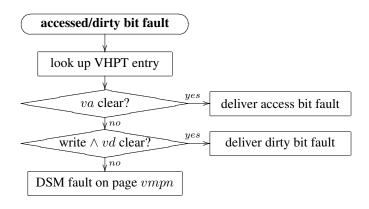

| 7.2 | Flowchart of protection fault handling                              | 79  |

| 7.3 | Anatomy of a VHPT entry                                             | 80  |

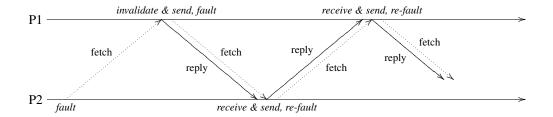

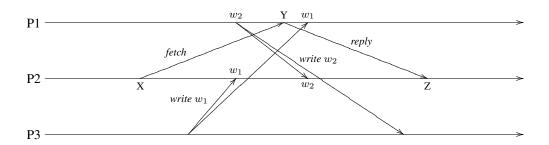

| 7.4 | Timeline demonstrating the page thrashing problem                   | 83  |

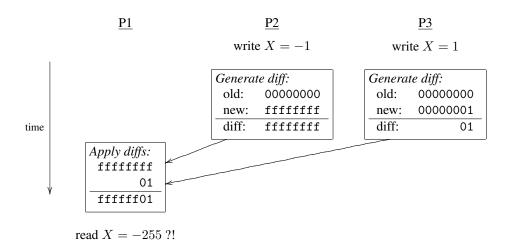

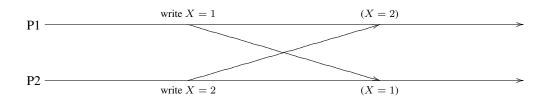

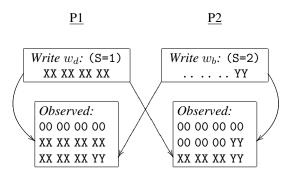

| 8.1 | Problem with write diffing in the presence of conflicting writes    | 96  |

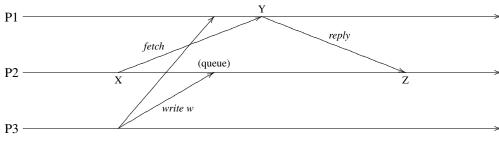

| 8.2 | Timeline showing interaction between migration and write updates 1  | 101 |

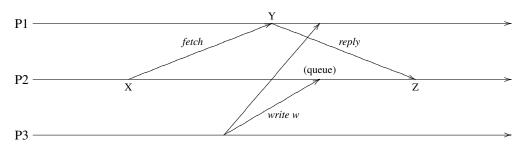

| 8.3 | Timeline showing a possible ordering problem                        | 103 |

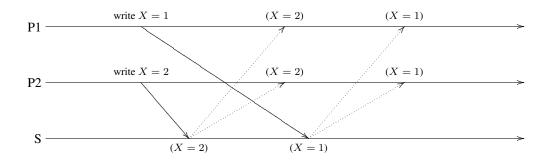

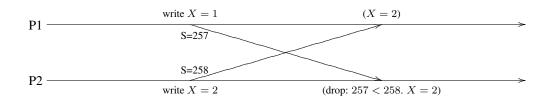

| 8.4 | Coherence problem with write notices                                | 105 |

| 8.5 | Central sequencer approach to coherence                             | 106 |

| 8.6 | Deterministic merging approach to coherence                         | 107 |

| 8.7 | Combining writes of different sizes                                 | 108 |

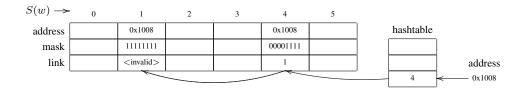

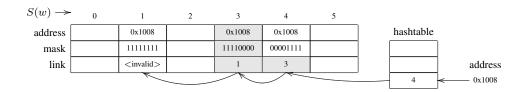

| 8.8 | Data structure used for coherence algorithm                         | 109 |

x LIST OF FIGURES

| 8.9 Adding a new write in the coherence algorithm                         | .09 |

|---------------------------------------------------------------------------|-----|

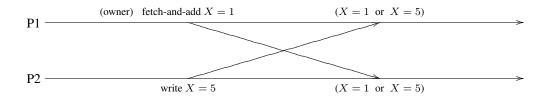

| 8.10 Problem arising from simultaneous writes and atomic operations . $1$ | .13 |

| 8.11 Example execution illustrating one effect of a memory fence 1        | 18  |

| 8.12 Use of memory fences in the Linux wait_on_bit_lock imple-            |     |

| mentation                                                                 | 19  |

| O.1. Anotomy of a vNHJMA modust                                           | 20  |

| 9.1 Anatomy of a vNUMA packet                                             |     |

| 9.2 Causally ordered delivery                                             |     |

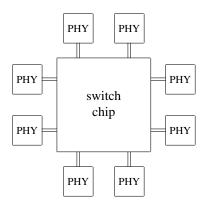

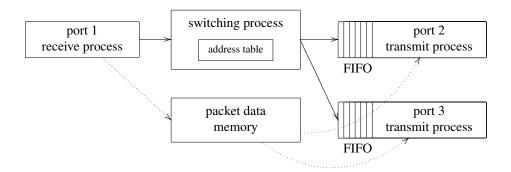

| 9.3 Design of a typical Gigabit Ethernet switch                           |     |

| 9.4 Basic operation of a switch chip                                      |     |

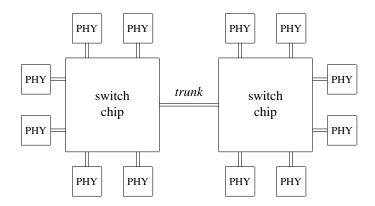

| 9.5 Design of a switch with two switch chips                              | .33 |

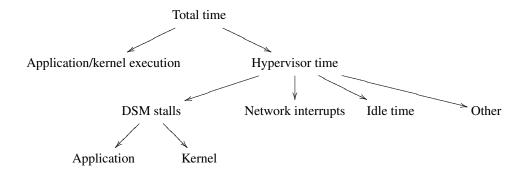

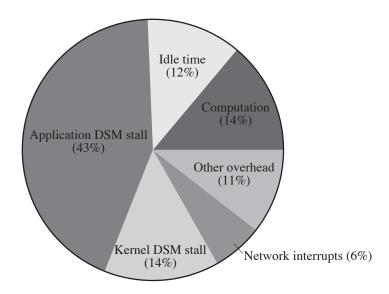

| 10.1 Breaking down execution time in vNUMA                                | 45  |

|                                                                           |     |

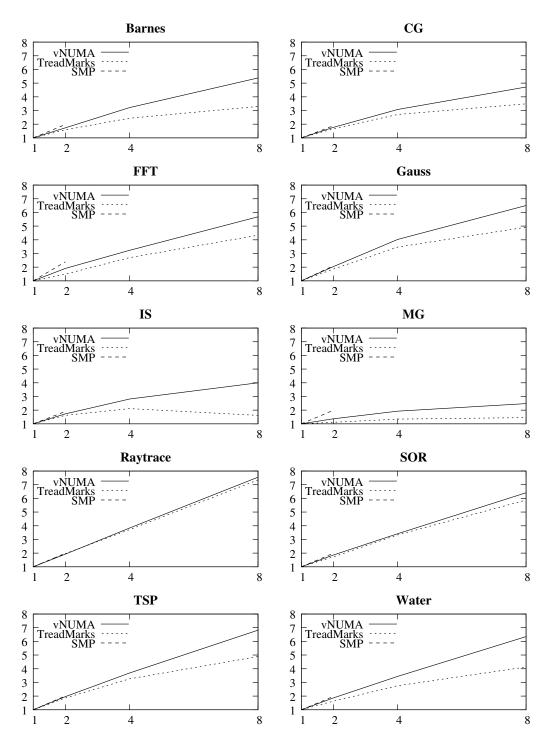

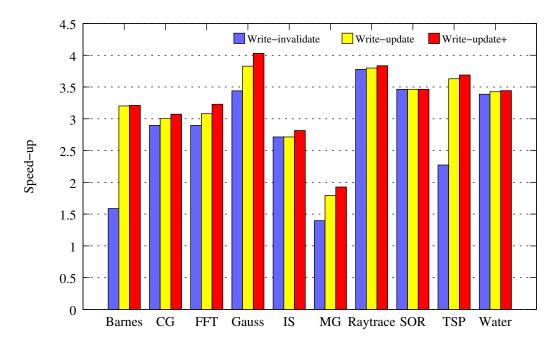

| 11.1 HPC benchmark performance summary                                    |     |

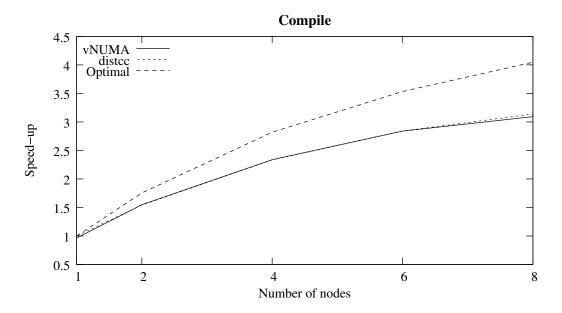

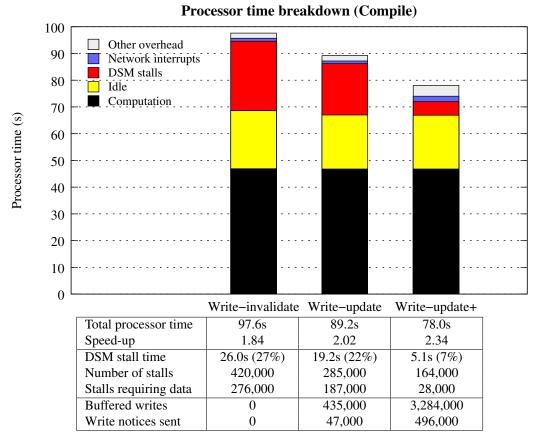

| 11.2 Compile benchmark performance summary                                |     |

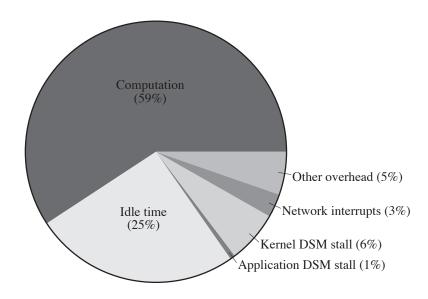

| 11.3 Time breakdown for compile benchmark                                 |     |

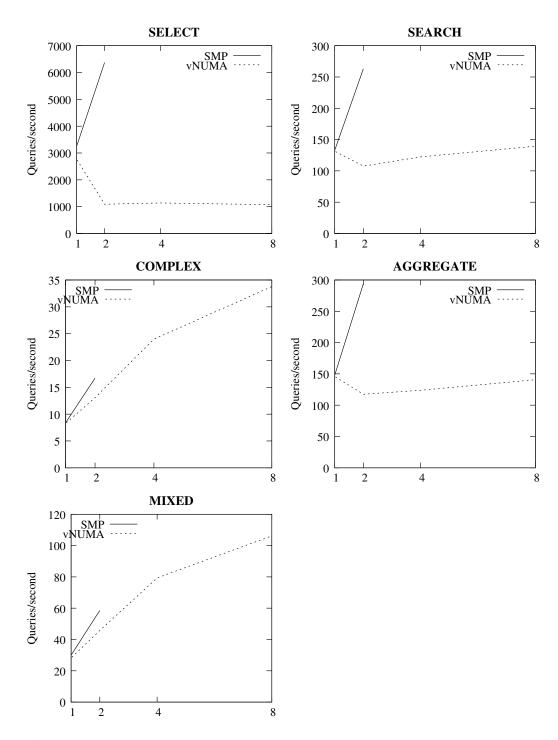

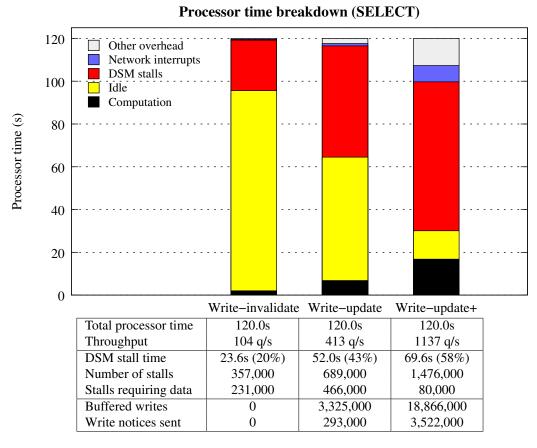

| 11.4 Database benchmark performance summary                               | .59 |

| 11.5 Time breakdown for SELECT workload                                   | 60  |

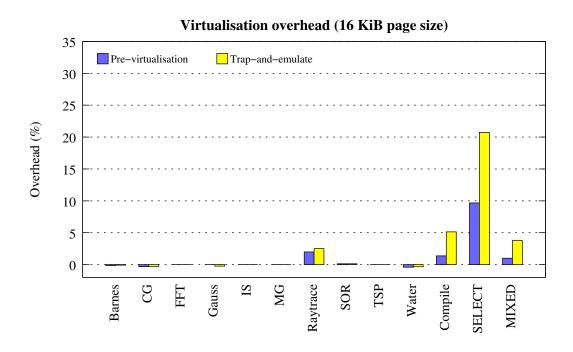

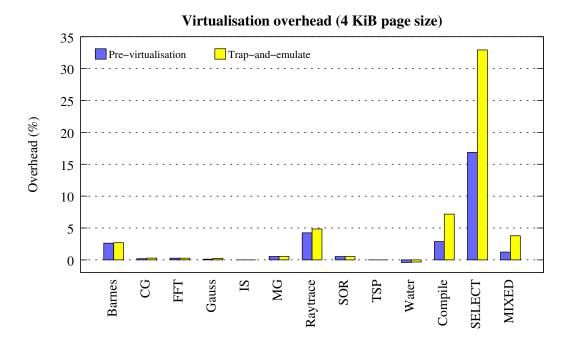

| 12.1 Virtualisation overhead                                              | 65  |

| 12.2 Compile benchmark comparison for different protocols 1               | 68  |

| 12.3 Database benchmark comparison for different protocols 1              | 69  |

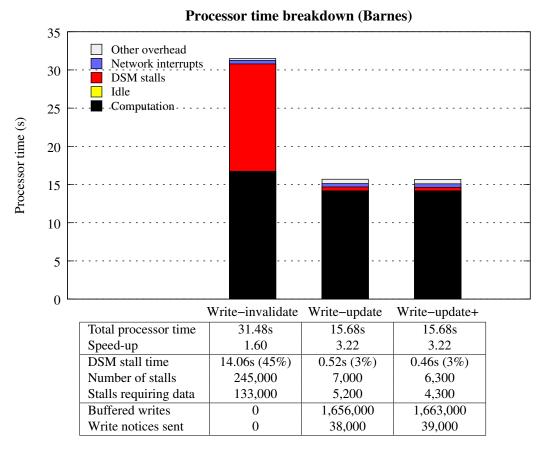

| 12.4 Barnes benchmark comparison for different protocols                  | 70  |

| 12.5 HPC benchmark performance for different protocols                    |     |

| 12.6 Compile performance at different invalidation thresholds 1           | 72  |

| 12.7 HPC benchmark performance at different invalidation thresholds . 1   | 73  |

| 12.8 Benchmark performance at different DSM page sizes                    | 74  |

| 12.9 Performance effects of enabling coherence algorithm                  | 76  |

| 12.10 Compile performance for different simulated latencies 1             | 78  |

| 12.11 Latency for a jumbo frame                                           | 81  |

| 12.12 Latency for four fragments                                          |     |

| 12.13 Stall latency histogram for FFT                                     |     |

| 12.14 Request delayed behind page fragments                               |     |

| 12.15 Using priority queueing to reduce request latency                   |     |

## **List of Tables**

| 3.1  | Sensitive Itanium instructions                                   |

|------|------------------------------------------------------------------|

|      | UNIX signals used by userspace VMM                               |

| 6.1  | Memory consistency models of common processor architectures . 73 |

| 9.1  | vNUMA message types                                              |

| 11.1 | Database stalls by function                                      |

| 12.1 | Latencies for basic operating system operations 164              |

2 LIST OF TABLES

## **Chapter 1**

## Introduction

Architectures for multiprocessor systems can be classified into two groups: those with coherent shared memory, such as SMP and ccNUMA systems, and those without, such as networks of commodity workstations connected by Ethernet.

Shared memory systems provide a simple programming model compatible with a large base of existing applications and operating systems. The majority of existing operating systems support such architectures; it is a relatively easy task to support them, even if not with optimal performance. Further, they naturally lend themselves to *single system image* (SSI) systems, where there is a single instance of the operating system with a single resource namespace. The appearance of a single system makes life simple for users and administrators. The single resource namespace means that computation can transparently migrate between processors to balance load, without fear that references to resources will become invalid.

Despite this, there has been a trend towards utilising networks of commodity workstations. Due to economies of scale, commodity hardware is far more cost-effective than large shared memory systems. It also provides benefits in terms of easy extensibility and reconfigurability of a cluster. However, most existing operating systems were not designed with such a cluster environment in mind, and cannot provide a single system image across multiple nodes in the absence of shared memory. Applications that were previously designed for shared memory systems need to be redesigned to explicitly communicate via the network. Users typically need to be aware of the nodes available and the resources available on those nodes. Administrators need to maintain the configuration of the separate

nodes.

There are many previous attempts to bridge this gap by emulating certain desirable features of a shared memory system on a cluster. For example, distributed shared memory libraries such as Treadmarks [50] can provide a limited illusion of shared memory to the programmer, assuming that the programmer uses the primitives provided by the library. Other projects have attempted to retrofit support for cluster-wide process scheduling and migration into existing operating systems; for Linux such systems include MOSIX [6], openSSI [89] and Kerrighed [71]. However, such efforts require extensive and intrusive operating system changes, which are difficult to keep up to date with the fast pace of operating system development. Of course, it is also possible to build operating systems that are specifically designed to provide transparency in networked environments, but unfortunately such novel operating systems rarely gain traction due to the inertia of legacy code.

Recently virtualisation has re-emerged into the limelight, and is becoming a standard part of the data center. Virtualisation inserts an extra layer into the software stack, decoupling an operating system from the underlying hardware. The most common use of virtualisation is to allow multiple operating system instances to share a single computer. However, it has been recognised that virtualisation also has other interesting applications, such as enabling legacy operating systems to support new hardware architectures [8] or transparently migrating an operating system instance from one computer to another [15].

This thesis explores using virtualisation to bridge the gap between shared memory systems and workstation clusters. In the system described in this thesis — dubbed vNUMA, an acronym for virtual NUMA — a virtual shared memory multiprocessor is built from a cluster of workstations. Users gain all of the advantages of a single-system-image multiprocessor, such as a single view of resources and transparent process scheduling, while being able to use existing operating systems and applications.

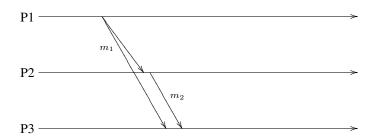

An example of the architecture of a vNUMA system is shown in Figure 1.1. At a physical level, the system consists of a cluster of commodity workstations connected by Gigabit Ethernet. An instance of the vNUMA hypervisor runs on each workstation and is responsible for controlling physical resources such as

Figure 1.1: Example vNUMA system

processors, memory and devices (there is no host operating system). Initially, a virtual machine is started from one of the nodes of the cluster, and boots an operating system such as Linux. The hypervisors then co-operate to extend this virtual machine across all of the cluster's resources: transparently mapping virtual processors to real processors in the cluster, and providing shared memory using software techniques. In this way, a single operating system instance can be scaled 'outside the box', utilising the computing resources of more than one node. In this thesis, feasibility of this approach is investigated for a small cluster of up to eight workstations.

Since this thesis was commenced, two other systems have emerged which apply similar ideas to vNUMA: Virtual Iron's VFe hypervisor [88] and Kenji Kaneda's Virtual Multiprocessor from the University of Tokyo [49]. These should be considered to have been developed independently, although the vNUMA work described here was the first to be published. While these systems both demonstrate combining virtualisation with distributed shared memory, both are limited in scope and performance, and do not address many of the challenges that this thesis addresses. In particular, both use simpler virtualisation schemes and distributed shared memory protocols, resulting in severe performance limitations, especially in the case of Virtual Multiprocessor. Virtual Iron attempted to address some of these performance issues by using high-end hardware, such as InfiniBand rather

than Gigabit Ethernet. However, this greatly increases the cost of such a system, and limits the target market. Virtual Iron has since abandoned the product for commercial reasons, which largely seems to stem from its dependence on such high-end hardware<sup>1</sup>. vNUMA, in contrast, demonstrates how novel techniques can achieve good performance on commodity hardware.

Part I of this thesis analyses the virtualisability of the Itanium processor architecture upon which vNUMA is built, and presents an approach for efficient virtualisation. Part II investigates the challenges involved in implementing a distributed shared memory system within this virtualisation layer, that can satisfy the demands of an operating system and unmodified applications while simultaneously providing good performance. It describes a distributed shared memory protocol that can meet these challenges. Part III evaluates the design of the system, presenting results for a variety of benchmarks.

<sup>&</sup>lt;sup>1</sup>According to Virtual Iron's John Thibault, "Trying to sell InfiniBand into enterprise datacenters was, to say the least, a real challenge. We were spending more time selling InfiniBand than our own product." [83]

# Part I Itanium virtualisation

The vNUMA system is fundamentally a virtual machine which can cross the boundaries of physical computers. The first task, then, is to build the virtual machine infrastructure, and this will lay the groundwork for the second part of the thesis which investigates how it can be distributed across multiple physical computers.

While the ideas behind vNUMA can be applied to most processor architectures, there are significant practical differences between architectures, and it is necessary to choose one as a focus for this thesis and particularly the experimental The Itanium processor architecture was chosen for a number of reasons. Firstly, at the time this thesis was commenced, there was no other Itanium virtualisation solution or analysis of the virtualisability of the Itanium architecture. Intel was poising Itanium to become the next major server architecture, and so this was an important gap that needed to be filled. As of 2008, some would say that Intel's vision did not succeed, and that the 'Itanic' has been relegated to certain niche parts of the market. Nevertheless it is still widely used in scientific clusters and enterprise-class database servers, which are some of the workloads that vNUMA is designed for. The Itanium architecture also has many innovative features, such as its register stack engine and relaxed memory consistency model. These features provide opportunities for innovation, and are representative of a more modern architecture design than the ubiquitous x86 architecture, which is the result of 30 years of haphazard evolution. The virtualisation challenges associated with x86 are complex, widely known, and littered with patents.

This chapter will provide an overview of virtualisation, the issues involved with virtualising the Itanium architecture, and the design of the vNUMA virtualisation layer.

## Chapter 2

## Virtualisation

Software applications rely on an operating system to provide basic services such as input and output. Traditionally the operating system has been part of the lowest layer of software on a computer system, with full control of the system hardware. In such a design it is not possible to have more than one operating system on a single computer. However, the complexity and variety of modern operating systems have led to them being considered almost part of the application layer; developing a given application is intricately connected to the underlying operating system and its configuration. An operating system, its configuration and a set of applications that execute atop it can collectively be referred to as an operating system *instance*.

Virtualisation inserts another thin layer of software, known as a *virtual machine monitor* (VMM) or *hypervisor*, underneath the operating system. Instead of having direct control of the real computer hardware, the operating system now controls the resources of an imaginary computer known as a *virtual machine*; the virtual machine monitor controls how those resources are mapped to real hardware. The virtualisation layer enables a variety of scenarios for managing operating system instances.

One of the most common applications of virtualisation is server consolidation. The pace of progress in computer hardware is such that many servers are increasingly underutilised. Server consolidation allows multiple operating system instances, that might previously have been housed on separate servers, to be consolidated onto a single server. This improves resource utilisation and reduces

the number of physical computers required, resulting in cost, power and manageability advantages. Compared to simply combining applications onto a single operating system instance, virtualisation can provide stronger isolation between the applications, improving security. Virtualisation also allows consolidating workloads which require different operating systems, different versions of an operating system, or incompatible operating system configurations.

Furthermore, virtualisation enables easy migration of operating system instances between physical servers. In fact, a number of modern virtual machine monitors support *live* migration, where virtual machines can be migrated while still running, with minimal downtime [15]. This is useful for load balancing; entire virtual machines can be moved around to optimise resource utilisation.

Virtualisation permits the complete state of a virtual machine to be captured at any point in time. This allows simple cloning of servers, restoring servers to a known-good state, capturing snapshots for post-mortem analysis, making consistent backups of a live system with no downtime, and many other possible scenarios. One particularly novel application is the time-travelling virtual machine [53], which can be rewound to any point in time to aid in debugging. The virtual machine is first rewound to the last snapshot before the desired point, and then run forwards while deterministically replaying external events.

The encapsulation of operating system instances provided by virtualisation has also led to the emergence of *virtual appliances* as a mechanism for software deployment. Virtual appliances are packaged snapshots of virtual machines that have been pre-configured for a particular task. For example, a user may be able to download a web server appliance which contains not only the web server application, but an entire virtual machine which has been appropriately configured for that purpose. This is analogous to purchasing a 'turnkey' web server appliance, but in this case the hardware is virtual and consolidation is possible.

Finally, virtualisation can allow legacy software systems to execute on radically new hardware architectures, without imposing this compatibility burden on the hardware; the transformation between the two architectures is left to the virtual machine monitor. For example, MagiXen [11] allows operating systems designed for the ubiquitous x86 architecture to execute on the newer Itanium architecture. Disco [8] carves a NUMA system into multiple virtual SMP nodes

for the benefit of existing operating systems that may not support a NUMA architecture. vNUMA — the subject of this thesis — combines multiple separate nodes into a single virtual NUMA system, allowing a single operating system instance to span multiple physical servers.

### 2.1 Full virtualisation

Virtual machine monitors can be described in terms of two basic design philosophies: *full virtualisation* and *para-virtualisation*. In a VMM which implements full virtualisation, the interposition between the operating system and hardware is done transparently, such that the operating system does not need to be modified. In other words, the interface between the operating system and virtual machine monitor is the same as the original interface between the operating system and hardware.

This is made possible by the concept of privilege levels, which exist in practically all general-purpose processor architectures. At the least, processors have a privileged mode and an unprivileged mode. The privileged mode confers unfettered control of all aspects of processor operation, while the unprivileged mode is a carefully controlled sandbox; whenever an unprivileged program needs to reach beyond its sandbox, it must invoke the privileged layer. Traditionally the entity that runs at the privileged layer is the operating system. In a virtualised system, the operating system is relegated to the unprivileged mode together with other applications. When the operating system attempts to perform a privileged function, it is at first disallowed; the processor instead notifies the virtual machine monitor running in the privileged layer. The VMM performs any necessary effects, depending on the virtualisation scenario that is desired, and then makes it seem to the operating system that the operating system. This interposition can often be made transparent to the operating system.

One of the earliest applications of this concept was IBM's CP/CMS system [17]. CP/CMS was developed in the 1960s as IBM's answer to the Multics timesharing system. Instead of designing a completely new multi-user operating system, CP (Control Program) was a thin virtual machine monitor which multiplexed the resources of the physical machine. This allowed each user to start their own

instance of the CMS (Conversational Monitor System) operating system. The successors of CP/CMS, VM/370 and z/VM, are still in use today.

The same ideas were leveraged in the 1990s for a somewhat different purpose, in the form of the Disco system [8]. Disco was a virtual machine monitor for the MIPS processor architecture, specifically designed for the Stanford FLASH multiprocessor, a large experimental shared memory system. Upon the FLASH machine, Disco provided the abstraction of a cluster of SMP machines; each of these virtual SMP machines could execute a commodity MIPS operating system such as SGI IRIX. This circumvented the engineering effort that would be required to enhance such an operating system to run efficiently on the large multiprocessor. The subsequent Cellular Disco system [38] extended Disco to provide improved support for partitioning and resource management.

A number of the Disco researchers also went on to found VMware, Inc., which brought virtualisation into the limelight by applying it to the ubiquitous IA-32 processor architecture. IA-32 does not fulfil the necessary requirements for it to be directly virtualised via the trap-and-emulate mechanism described above (also known as *native* or *classic* virtualisation). As elucidated by Popek and Goldberg [79], the key requirement is all *sensitive* instructions — those that affect or depend on the current privilege level or the state of privileged resources in the system are privileged. This is not the case for IA-32, which contains some unprivileged sensitive instructions; these can behave in subtly different ways in a lower privilege level without raising an exception [57]. VMware's breakthrough was to develop a relatively efficient method to translate privileged operating system code, at runtime, into code that has similar semantics but executes correctly in the lower privilege mode [1]. Microsoft Virtual PC and Microsoft Virtual Server, originally acquired from Connectix, also utilise comparable dynamic translation techniques. Making this dynamic translation fast and transparent to the operating system is no easy task, however, and this technology is closely guarded.

Since these products have taken hold in the market, processor designers have taken note. The largest manufacturers of IA-32 processors, Intel and AMD, have recently introduced virtualisation extensions to the IA-32 architecture, adding a new mode in which all of the problematic instructions can be intercepted [48, 2]. These extensions have since been leveraged by both the VMware and

Microsoft solutions, as well as those from other industry players. Intel has also added similar extensions to the Itanium processor architecture, which has similar problems to IA-32, as will be described in this thesis. On the other hand, these virtualisation extensions do not solve all of the challenges associated with virtualisation, particularly when good performance is required [1].

### 2.2 Para-virtualisation

Full virtualisation imposes significant limitations on a virtual machine monitor design, since it must accurately reproduce a hardware interface. If the architecture is not natively virtualisable and dynamic translation is needed, this introduces considerable complexity and runtime overhead. Even if the architecture lends itself to native virtualisation, the nature of such virtualisation is such that each privileged instruction causes an exception to the virtual machine monitor. On modern pipelined processors, these frequent exceptions result in a high overhead (as will be seen in Chapter 12).

For these reasons there has been a trend towards para-virtualisation, which adapts the interface to the virtual machine monitor for greater simplicity, performance and functionality. For instance, a para-virtualised version of an architecture might define that the operating system must not rely on the behaviour of certain instructions. Direct *hypervisor calls* may be introduced to streamline certain operations such as context switching or access to devices, rather than relying on emulation of privileged instructions. The downside of para-virtualisation is that an operating system must be explicitly modified to use the new interface, with the associated engineering overhead of maintaining a separate body of code that is not used on real hardware platforms.

The para-virtualisation technique is not new, in fact it was already applied ante litteram in the CP/CMS system. While CMS was originally designed so that it could execute on real hardware, very soon new functionality was introduced that specifically relied on CP features; for instance, efficiency gains were made by replacing the device accesses in CMS with direct calls to CP. This involved using the DIAGNOSE instruction, normally a reserved instruction that operating systems should not use, as a mechanism for invoking hypervisor calls [87].

More recently, this idea was taken further by the Denali project [90]. Denali sought to build a type of hypervisor (they called it an *isolation kernel*) that could multiplex thousands of lightweight virtual machines. In order to provide such scalability, far beyond the capabilities of conventional hypervisors, the overheads involved in virtualisation had to be reduced. Para-virtualisation was the answer. Rather than attempting to faithfully emulate the complicated privileged architecture of IA-32 processors, Denali exported a simpler set of abstractions. In this way it is also similar to a microkernel; in fact there is little practical difference between a hypervisor and a microkernel, except that the choice of basic primitives for a hypervisor tends to be biased towards the requirements of existing operating systems, whereas the design of microkernels is primarily guided by the desire for a minimal elegant interface. Indeed para-virtualisation methods can also be applied to allow existing operating systems to run on top of a microkernel, where the microkernel acts as a hypervisor. For example, the Wombat system [59] allows Linux to run atop the L4 microkernel.

Para-virtualisation has gained greatest traction in the form of Xen, which has risen to become one of the leading enterprise virtualisation platforms (alongside VMware's and Microsoft's offerings). Xen was originally developed in the context of Linux on the IA-32 architecture; it relies on major operating system changes on that platform, with most privileged functionality being achieved via hypervisor calls rather than privileged instructions. However, the extent of these changes has hampered the adoption of these modifications into the mainstream Linux source code, and a great deal of engineering effort is required to keep them up-to-date in the face of a fast-changing operating system.

The Itanium port of Xen, however, does not require such significant operating system changes. The code is originally derived from the vBlades hypervisor [63] and uses a technique that has been dubbed *optimised para-virtualisation*. The idea behind optimised para-virtualisation is to first implement a hypervisor that is capable of full virtualisation (or close to it), making minimal modifications to the operating system. Having done this, one can do detailed profiling to determine which code paths would benefit most from para-virtualisation, and so achieve a balance between performance and engineering effort.

17

#### 2.3 Pre-virtualisation

To address the performance cost associated with full virtualisation and the engineering cost associated with para-virtualisation, LeVasseur et al (including the present author) recently introduced the idea of pre-virtualisation [60]. Pre-virtualisation is an automated form of para-virtualisation that can be used when the source code for the operating system kernel is available. Instead of requiring a programmer to manually modify the source code, it is transformed during the build process, by using a special toolchain that replaces certain instructions. The simplest option is simply to map each problematic instruction into an implementation tailored for a particular hypervisor (a simple version of such a technique was also used in the LilyVM virtual machine [25]). A more sophisticated possibility is to transform the code into an intermediate form that still executes correctly on real hardware but allows the problematic instructions to be easily identified and replaced at runtime.

The vNUMA hypervisor described in this thesis uses pre-virtualisation. However, pre-virtualisation was originally conceived with reference to the x86 architecture, whereas vNUMA is an Itanium virtual machine monitor; applying these techniques to the Itanium architecture is not trivial. Chapter 3 will describe general challenges associated with Itanium virtualisation, while Chapter 4 will specifically address applying pre-virtualisation to the Itanium architecture.

## 2.4 Type I vs Type II

Para-virtualisation and pre-virtualisation can also be applied to allow an operating system to run directly on top of another operating system. User Mode Linux [22] is a para-virtualised port of Linux to Linux, whereby Linux is considered to be another target architecture; hardware abstractions such as virtual address spaces are implemented in terms of Linux processes and APIs. Clearly this requires significant porting and maintenance effort, even greater than those changes required by Xen. Linux-on-Linux, which will be described in Chapter 5, is a less intrusive approach using pre-virtualisation, requiring minimal changes to the two operating systems.

It is useful to define some terminology in this context. User Mode Linux and Linux-on-Linux are examples of what is known as *Type II* [36] or *userspace* virtual machine monitors, in that they depend on an underlying operating system. That operating system is known as the *host* operating system, whereas the operating system inside the virtual machine is known as the *guest* operating system. In contrast, a *Type I* or *standalone* virtual machine monitor executes on bare hardware and does not utilise a host operating system. It is also possible to construct a *hybrid* virtual machine monitor, such as VMware Workstation and Microsoft Virtual PC, which utilise a host operating system for certain services but steal the processor from the operating system while the VMM is executing.

## **Chapter 3**

## Itanium challenges

This hypervisor described in this thesis has initially been designed for the Itanium processor architecture [47]. Itanium is a modern 64-bit processor architecture that was developed jointly by HP and Intel in the late 1990s. While its instruction set shares many features with HP's earlier PA-RISC architecture, Itanium has a number of novel features that set it apart in its own class.

Unlike most processor architectures, the Itanium architecture explicitly represents instruction-level parallelism in the instruction stream. This is described as *explicitly-parallel instruction-set computing* (EPIC). Instructions are arranged in bundles destined for specific execution units, and delineated into instruction groups that specify which instructions can be executed in parallel. This results in a simpler hardware design — the processor does not need to dynamically re-order instructions — but shifts the burden of complexity to compilers and low-level software.

Similarly, other processor architectures provide relatively small register sets; high-performance processor implementations then dynamically remap these onto a larger number of physical registers. Itanium instead provides a large architectural register set, eliminating the need for dynamic remapping. To aid software in the management of this large number of registers, the Itanium architecture provides a register windowing feature, similar to but more flexible than that provided by the SPARC architecture [84]. In addition to a set of 32 fixed registers, each procedure can allocate a variable-sized window of up to 96 registers. This window is divided into input, local and output portions; upon a procedure call,

the window is shifted so that the output portion becomes the input portion for the callee, and the caller's local registers are safely hidden. Even though the physical number of processor registers is limited, the Itanium architecture provides a *register stack engine* (RSE) which transparently saves and restores registers in the hidden portion, providing the illusion of an infinite continuum of registers.

This chapter will present the challenges involved in virtualisation of the Itanium architecture, and how they can be addressed. When the Itanium architecture was first developed, virtualisation was not seen as a design goal. As a result the Itanium architecture, like IA-32, is not natively virtualisable in the classic way. When an Itanium operating system is demoted to a lower privilege level — the first step towards virtualisation — a number of issues arise that compromise the ability of the hypervisor to provide a faithfully virtualised environment. These issues will be explored in the following sections.

It should be noted that a number of these problems were also encountered by the authors of vBlades [63], another virtual machine monitor for the Itanium architecture that was developed independently from vNUMA. Except where noted, vBlades employs very similar workarounds to vNUMA. The vBlades code also later became the foundation for Xen/ia64, the Itanium port of the Xen virtual machine monitor [29].

Most recently, Intel has added a set of extensions to the Itanium architecture, codenamed Silvervale but officially known as Virtualisation Technology for Itanium (VT-i) [47]. The first implementation of VT-i was released with the Dual-Core Itanium 2 ('Montecito') processor in 2006. VT-i addresses some but not all of Itanium's virtualisability issues. Specifically, it provides a special processor mode that alleviates the problems described in Sections 3.1, 3.2 and 3.3. While this brings Itanium closer to being natively virtualisable, this is not a panacea; as previously mentioned, para-virtualisation and pre-virtualisation approaches have the potential to provide better performance than native virtualisation. For this reason the vNUMA implementation does not utilise VT-i. Even with VT-i, some architectural features, particularly those described in Sections 3.4 and 3.5, remain difficult to virtualise efficiently and demand elaborate workarounds.

| Instruction | Function                                                |

|-------------|---------------------------------------------------------|

| cover       | Allocate new register window, possibly save size of old |

| mov =ar.rsc | Read RSE control register                               |

| thash/ttag  | Calculate page table hash and tag values                |

| fc          | Flush cache line                                        |

| mov =cpuid  | Read CPU type and feature information                   |

| mov =pmd    | Read performance monitoring counter                     |

| mov =ar.k*  | Read kernel register                                    |

**Table 3.1:** Sensitive Itanium instructions

#### 3.1 Sensitive instructions

As mentioned previously, virtualisation involves running an operating system in a less privileged mode. Privileged instructions trap when they are executed in the less privileged mode, and can then be emulated by the virtual machine monitor. Unprivileged instructions generally execute normally. However, many architectures have unprivileged instructions which do not trap but somehow behave differently in the less privileged mode; these are known as *sensitive instructions* [79]. These are problematic because it is difficult for the virtual machine monitor to intercept them in order to correct their behaviour. The problematic instructions in the Itanium architecture are listed in Table 3.1 and described in detail in this section.

For example, Itanium provides an instruction called cover which is used in conjunction with the register windowing feature. The specific function of the cover instruction is to hide the current register window — *covering* it — and to allocate a new empty window.

Since control of register windows is in the hands of applications, the cover instruction is unprivileged. Unfortunately, the designers saw it fit to overload the instruction with another side-effect: in the special case that interruption collection is disabled<sup>1</sup>, it also saves the original size of the register window to a control register. This functionality is used by operating systems in order to save register

<sup>&</sup>lt;sup>1</sup>Interruption collection is not the same as interrupt control, but the two control bits are closely related. Interruption collection determines whether context is saved to control registers when a new exception occurs, or whether the processor attempts to keep control registers intact. With interruption collection off, it is not possible to return to the original context after an exception.

window state during an exception, simultaneously hiding the old window and obtaining its size. In a virtualised environment, it is not safe to allow an operating system to disable interruption collection, so cover always executes using its unprivileged semantics. Namely, it hides the old frame but does not write its size to the control register (and does not trap to allow the hypervisor to save the size). Thus, even though the hypervisor can intercept the later read of the control register, the size of the old frame has been irrecoverably lost.

The register stack engine control register, ar.rsc, is also exposed to userspace. This is problematic for virtualisation because it contains a field that specifies the privilege level with which RSE accesses occur. Normally this cannot be used for privilege escalation, since writing a value that is more privileged than the current privilege level is never allowed; such values are silently clipped to the current privilege level. However, in a virtualised environment, reads expose the actual privilege level rather than the virtualised privilege level, which may or may not affect correct execution. Of most concern, naïve writes by privileged code may establish incorrect values for less privileged code. For example, consider if an operating system kernel attempts to confine code to ring 1, and therefore specifies a value of 1 in the privilege level field. If the ring compression technique (Section 3.2) is used, this will inadvertantly give the code access to the ring where the kernel itself is. Fortunately, existing Itanium operating systems only utilise rings 0 and 3, so this never occurs.

The thash and ttag instructions are used to calculate the address and tag value, respectively, for an entry in the Itanium architectural page table (which is a type of hashed page table [42]). While it would seem that these instructions have little use to application code, they only perform calculations and thus processor designers deemed that they could safely be made unprivileged. However, in order to perform their calculations, these instructions actually utilise privileged state information, namely the page table base address, size and format. When a guest operating system executes these instructions, it expects the calculations to be made in the context of its own page table. However, in actual fact, the instructions will silently return information about the real page table used by hardware, namely the virtual machine monitor's page table!

The fc instruction to flush cache lines also has a curious quirk, albeit

23

somewhat less problematic. When executed at the most privileged level (ring 0), it bypasses TLB protection checks. At lower privilege levels, such as when the kernel is demoted to ring 1 in a virtualised environment, fc performs permission checking as if it was a one-byte read. Attempts to flush execute-only pages now result in memory protection faults. In this case the virtual machine monitor must be very careful to emulate the fc instruction rather than delivering the protection fault to the guest operating system, which may be fatal. To avoid extra checks in the page fault path, it may be desirable to deal with fc by replacing it in the same way as other sensitive instructions.

The cpuid register file is an array of registers providing identification information about the processor, such as the vendor, model, architecture revision and supported features. Access to this register file does not require any special privileges; thus the real processor's identification information is read directly by the guest operating system and applications. In most cases this is not a problem, since the processor features described by the Itanium's cpuid registers primarily describe the availability of user-level instructions. However, a guest operating system may utilise the model information to tune its functionality in undesirable ways; this may cause problems when a virtual machine is migrated to a different type of processor. Additionally, there are situations where the virtual machine monitor may want to avoid advertising certain features (for instance, vNUMA does not currently support 16-byte atomic memory operations), and it would be desirable to be able to reflect this in cpuid values.

The pmd register file provides access to performance monitoring counters. Within a virtual machine, it might be desirable to virtualise these counters, so as to isolate the operating system from the processor that it is executing on. Unfortunately, even if the counters are configured to deny userspace accesses, unauthorised reads do not fault and simply return zero values. This makes it difficult for a hypervisor to intercept and emulate these accesses. If performance monitoring functionality is to be exported to the guest operating system, the counters must directly correspond to those provided by the underlying processor, and their configuration and values must be context-switched as part of the virtual machine state.

Finally, there is a set of kernel registers which can only be written by

privileged code but are readable at any privilege level. This provides a lightweight mechanism to convey certain data from a kernel to applications, although in practice these registers are mainly used by operating systems to store processor-local kernel data. Since reads of these registers never fault, at any privilege level, they cannot be virtualised in the normal way. In Type I virtual machine monitors, the registers can be context-switched between virtual machines, but this proves problematic for Type II VMMs since a host kernel will use the kernel registers for its own internal purposes. The guest kernel then unavoidably observes the values written by the host kernel, instead of the virtual values.

There are a number of approaches for dealing with sensitive instructions. Generally these can be categorised according to whether they detect the sensitive instructions statically within a kernel binary or dynamically at runtime, and whether they attempt to translate them intelligently or simply allow them to fault to the hypervisor for handling.

Early versions of vBlades, Xen/ia64 and vNUMA have all used simple tools which statically pre-process a kernel binary, replacing sensitive instructions such that they fault. The replacement instructions are chosen from the set of privileged or reserved instructions that are not normally used by an operating system, and that fit in the same space as the original instruction. Such substitutions can also be performed dynamically at runtime<sup>2</sup>, or on newer processors the instructions can be intercepted at runtime using the VT-i extensions: VT-i provides a special processor mode in which any attempt to execute a sensitive instructions results in a fault. Such techniques are simple and reliable, but do not provide optimal performance, since each sensitive instruction now causes a fault and is emulated by the hypervisor.

Later versions of Xen/ia64 use manual para-virtualisation, relying on manual modifications to the operating system that replace the sensitive instructions. To avoid the associated engineering effort, the current version of vNUMA instead uses the automated pre-virtualisation technique described in Chapter 4, which substitutes the sensitive instructions as they pass through the assembler. In both

<sup>&</sup>lt;sup>2</sup>A good technique, described by Lawton [57], is to translate a page at the time it is inserted into the instruction TLB, while inserting the original version of the page into the data TLB. This ensures that the operating system can never observe the modified pages, even if the translator inadvertantly misidentifies data as instructions.

Figure 3.1: Ring compression

cases, the changes are made statically; since symbolic information is still present at build time, replacing a single instruction with larger emulation code rarely poses problems. Performing this feat at runtime, on the other hand, would be far more difficult.

## 3.2 Ring compression

The Itanium architecture, like x86, provides four hierarchical privilege levels or *rings*, derived from the model introduced in Multics [18]. These privilege levels are numbered from 0 to 3, with 0 being the most privileged and 3 the least.

Since code executing in ring 0 is generally allowed to execute any privileged instruction, an operating system kernel must be demoted from ring 0 to ring 1 to enforce virtualisation. However, this now only leaves three rings for the operating system to use, instead of four. If the original operating system were to rely on all four of those rings, it would be necessary for the hypervisor to merge two of them together, as shown in Figure 3.1. This results in a loss of protection between those two rings. Fortunately, in practice the majority of operating systems do not use ring 1 and 2 at all, so this does not present a problem.

In processors with Intel VT-i, ring compression is unnecessary. This is because, with VT-i, privileged instructions always fault when the processor is executing in virtual machine mode, *even in ring 0*. Thus it is safe to execute the guest operating system in ring 0, providing it with the full set of rings.

## 3.3 Hiding the VMM

When the Itanium processor encounters an exception, it simply branches to the appropriate exception vector address, without switching off virtual address translation. This means that a hypervisor's exception vectors must be located somewhere in the virtual address space. However, it is not obvious where to put them; the guest operating system believes that it has control of the entire virtual address space, and may attempt to insert mappings in any portion of it.

One approach is to optimistically choose a location where guest operating systems are unlikely to place mappings. If a guest operating system does attempt to place a mapping there, the exception vectors can be remapped to a new location.

An even simpler approach is to leverage the fact that the Itanium architecture defines a variable number of implemented virtual address bits, from a minimum of 51 bits per region to a maximum of 61 bits per region (which, over 8 regions, covers the entire 64 bit address space). At boot time, an operating system must query the number of implemented address bits. When executing on a processor with more than 51 implemented bits (any Itanium processor other than Itanium 1), the hypervisor can report that one less address bit is implemented. The guest operating system must not attempt to place mappings in the part of the address space that is reported as unimplemented, and this can be enforced by the hypervisor. The hypervisor can then be hidden within that space.

In fact, VT-i enforces this one-bit differential. When executing in virtual machine mode, the processor behaves as if one less bit was implemented, and guarantees that the guest operating system cannot access the hidden region. When an exception occurs, the virtual machine mode is exited, revealing this hidden address space where the hypervisor is concealed. This is a necessary part of VT-i because memory protections would not otherwise protect the hypervisor from the operating system, since they both execute in ring 0.

## 3.4 Register stack engine faults

The register stack engine typically operates through virtual memory, and therefore may encounter virtual memory faults while loading or storing registers. When this happens, RSE operation may be halted partway through loading a frame. The exception handler then executes with an *incomplete* register stack frame, some of which may be undefined; this is only possible in ring 0. When the handler has finished, it executes the *return from interruption* (rfi) instruction, which returns to the original context and causes the RSE to resume loading the current frame.

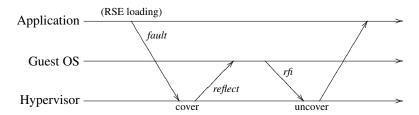

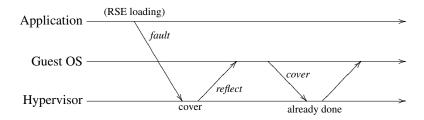

In a virtualised environment, the hypervisor will likely desire to reflect the virtual memory fault to the guest operating system for handling. However, in order to invoke the guest operating system in ring 1, the hypervisor must execute an rfi instruction. Even though it is now returning to a different privilege level and IP address, the rfi instruction nonetheless causes the RSE to resume loading the current frame and the fault is raised again (Figure 3.2(a)).

The workaround used in vNUMA and all known Itanium hypervisors is to emulate a cover instruction in the hypervisor when an incomplete frame is detected. This cover hides the current incomplete frame and instead allocates a new zero-size frame for the operating system exception handler. To the operating system, it is as if the faulting userspace application was executing with a zero-size frame. Typically the operating system handles the fault and executes rfi to return to the application, at which point the hypervisor restores the original frame (Figure 3.2(c)). Alternatively, the operating system may desire to save the userspace state, in order to enter C code or switch processes. In that case it necessarily executes cover, which is required to obtain the size of the userspace frame. Now this latter cover can be ignored since it has already been performed (Figure 3.2(d)).

It should be noted that, in addition to the case where loading of an RSE frame is interrupted by a memory management fault, the frame load can also be interrupted by the arrival of a hardware interrupt (Figure 3.2(b)). After the hypervisor reflects the interrupt to the guest operating system, the RSE resumes attempting to load the frame. If the RSE faults at this point, the fault appears to come from the interrupt vector address; such nested faults are usually fatal. The cover solution must also be applied to this scenario.

(a) Reflecting an RSE fault results in nested RSE faults

(b) Hardware interrupts can also trigger nested RSE faults

(c) cover workaround; guest OS handles exception and returns (rfi)

(d) cover workaround; guest OS then executes cover in order to save state

Figure 3.2: Register stack engine virtualisation: problem and workaround

## 3.5 Complex translation modes

When building a virtual machine monitor, it becomes necessary to virtualise the physical memory of the virtual machine. A virtual machine must never actually run with address translation disabled, or it could subvert all memory protection. Instead, when the operating system disables address translation, a VMM tears down the existing virtual address space and establishes a set of virtual mappings that provide the illusion of a physical memory space.

An obscure feature of the Itanium architecture is the ability to separately enable and disable virtual translation for instruction, data and register-stack-engine accesses. For example, it is possible to arrange for instruction and data accesses to be physically addressed (bypassing the TLB), while RSE accesses are translated virtually, or any other combination. Thus, a data access to address X may access physical address X, while a RSE access to address X may access some other page. This poses complications for virtualisation.

It is theoretically possible to provide separate mappings for instruction and data references, since the architecture provides for separate instruction and data TLBs. This requires disabling hardware-assisted TLB reload, since it is not possible to provide this distinction in either of the architectural page table formats. Another possibility is to restrict permissions on each mapping to only allow either data or instruction accesses, but not both, and emulate any instructions that require incompatible mappings. However, all of these options are complex and do not provide a mechanism to differentiate between data and RSE references, short of emulating all data references. Unfortunately VT-i is of no help in the matter.

This is not purely an academic question; Itanium Linux regularly disables data translation in order to access page tables, while continuing to execute instructions virtually. It also happens to leave register stack translation enabled, although in that particular case it has no effect on the outcome.

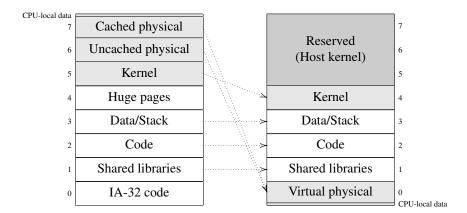

The solution used in current hypervisors is to expose the virtualised physical address space in the bottom region of the address space if *any* of the physical translation modes are enabled, while leaving the virtual address space active in higher regions to satisfy other types of accesses. This works for Linux, but is not a general solution. If an operating system kernel was to place virtual mappings in

the bottom region of the address space, and then use complex translation modes, this approach might be rendered invalid.

# **Chapter 4**

## **Pre-virtualisation**

As previously mentioned, using the trap-and-emulate method for all privileged and sensitive instructions presents considerable performance overhead. This can be addressed by para-virtualisation — modifying the guest operating system — but to do this manually requires significant engineering effort and is errorprone. Pre-virtualisation is a method by which much of this para-virtualisation effort, namely substitution of sensitive instructions with code tailored for a virtual machine, can be performed automatically. This section will first describe the pre-virtualisation technique (which was developed in collaboration with others [60]), and then specifically address the challenges in applying it to the Itanium architecture.

## 4.1 Mechanism

The source code of an operating system kernel is typically a combination of assembly language and a higher-level language such as C. At compile time, the C code is also translated into assembly language. Thus, at some stage all operating system code passes through the assembly language stage. This is the ideal level to perform instruction transformations, because much symbolic information is still present at this level: control flow transfers are performed via named labels rather than fixed addresses. This means that it is generally possible to substitute individual instructions with longer emulation sequences, without affecting control flow.

The pre-virtualisation process involves replacing the assembler with a wrapper that performs certain replacements before invoking the real assembler. The first stage is to translate the privileged and sensitive instructions into macro calls. For example, a privileged instruction (p6) mov r16=cr18 — which reads control register 18 into general register r16, conditional on predicate register p6 — might be replaced by the macro call:

This makes further substitution simpler, since all instructions are now in a common format that can be expanded by the assembler's macro facilities.

Next, the assembler is invoked, together with a macro definition file that provides an implementation of each macro. In the simplest case, these macros target a specific hypervisor. For example the following provides an implementation of emul\_read\_cr for vNUMA, which reads the value of the control register from a shared memory location:

Such substitutions result in more efficient virtualisation than a trap-and-emulate approach. Many instructions can be directly replaced with simple emulation code, avoiding the overhead of a trap and the complexity of reading, decoding and simulating the instruction. Those which cannot be emulated completely in user mode can access hypervisor services via the most efficient interface possible. In particular, the Itanium architecture provides an epc instruction (*enter privileged code*) which allows zero-overhead entry to privileged mode; vNUMA exports a number of services in this way, which can be leveraged by the macro definitions.

However, a binary so compiled will only work on the specific hypervisor targeted. A more sophisticated possibility (not yet implemented for vNUMA) is

4.1. MECHANISM 33

to insert the original instruction back into the binary, but add padding afterwards, as follows:

The resulting binary contains the original instruction and will therefore execute correctly on real hardware. The padding no-ops can generally be executed in parallel with the instruction, so the only impact is a small increase in code size.

When loaded on a hypervisor, however, the hypervisor can easily substitute the replacement instructions, since there is sufficient space to do so. For example, on vNUMA the control register read and the padding might be replaced with the mov and 1d8 sequence in example (2) above. In order to aid the hypervisor in locating and patching these instructions, it is helpful to record the beginning and end of each patch target in a special section, which can be achieved by a macro definition such as the following:

```

.macro emul_read_cr pr,dest,cr

9998:

(\pr) mov \dest=cr\cr

(\pr) nop.m 0x0

9999:

.pushsection .afterburn

.quad 9998b

.quad 9999b

.popsection

.endm

(4)

```

It is important to ensure that all code that originally executes in kernel mode is pre-virtualised so that the sensitive instructions are replaced. In particular, any dynamically loaded modules must also be built using the pre-virtualising assembler.

## 4.2 Challenges

While this idea of substituting instructions with emulation code is conceptually simple, the specifics of various processor architectures present different challenges. Previous work has only addressed the x86 architecture, which has a number of features that make pre-virtualisation particularly simple; for example, it is always possible to save registers on the stack, even in low-level operating system code. In this section the challenges associated with Itanium pre-virtualisation will be described, and some solutions presented. Many of the same issues also apply to other non-x86 architectures.

## 4.2.1 Scratch registers

The emulation code frequently requires spare registers in order to perform intermediate calculations, call an external procedure, or simply access memory<sup>1</sup>. However, it is non-trivial and sometimes impossible to determine which registers are safe to overwrite in a given context; register usage conventions may not apply in handwritten assembly code. It is also not possible to save and restore registers to memory without having at least one scratch register to start with (in order to generate the memory address); it is not safe to rely on the stack pointer since it may be invalid in low-level code.

When substituting instructions that write a destination register, the destination register can be considered scratch until the final result is generated. This is the case in the emul\_read\_cr case in example (2) above, where the destination register has been used to temporarily store the load address. However, many instructions do not have a destination-register operand. It would also be preferable to have more than one scratch register available, to avoid costly saving and restoring of further needed registers.

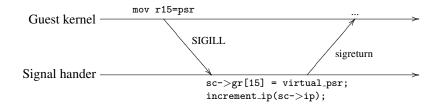

The solution used in vNUMA is to virtualise a subset of the machine registers that are rarely used, specifically r4-r7 and b2, when executing guest kernel code (which should exactly correspond to the body of code that is pre-virtualised). All references to those registers in the guest kernel code are replaced with instruction

<sup>&</sup>lt;sup>1</sup>Itanium memory access instructions require the target address to be in a register.

sequences that read and write shadow copies of those registers in memory, making the real registers available for the emulation code itself. When transitioning from guest user mode to guest kernel mode, the hypervisor saves the real registers to the memory-backed shadow registers; this allows the guest kernel to access the user mode values of the registers. Then, when returning to guest user mode, the shadow register values are restored into the real registers<sup>2</sup>. This provides complete transparency; the guest operating system is never aware of the conceit.

Since one of the most common functions of the emulation code is to access and update the virtual CPU state, it is useful to have a pointer to that state available at all times. One of the scratch registers is reserved for that purpose, and is initialised by the hypervisor upon entry to the pre-virtualised guest kernel.

## 4.2.2 Atomicity

Instruction rewriting replaces a single, non-interruptible instruction with an instruction sequence. If the emulation sequence updates state non-atomically and an interrupt arrives during that sequence, the interrupt handler could execute with the virtual CPU in some undefined state. Worse, the interrupt would clobber the values of scratch registers, since the OS interrupt handler itself contains previrtualised code. This would make the scratch registers useless in practice. There are two possible solutions: deferring interrupts during a block of emulation code, or attempting recovery if an interrupt arrives. Both options involve complications.

Initially the latter option was trialled; an emulation block would set one of the scratch registers to the address of a roll-back point, and clear that register at the end of the block. If an interrupt was delivered, the hypervisor would override the instruction pointer reported to the interrupt handler, such that upon return execution would be restarted from the roll-back point. This works well for emulation sequences that simply perform calculations before committing state, because it is safe to perform the calculations again. However, even in this case

<sup>&</sup>lt;sup>2</sup>The guest kernel may also be entered without hypervisor intervention, using the epc — enter privileged code — instruction; the emulation code for epc is then responsible for saving the registers. It is also necessary to restore the registers on exit; unfortunately exiting the kernel after an epc is done with a normal return instruction, which is difficult to detect and pre-virtualise automatically. The guest kernel was modified to annotate that particular return instruction.

there is the possibility that the state update might be applied twice, if an interrupt is delivered between the state update and the clearing of the roll-back register. Also, more complex emulation code can be difficult or impossible to write in a way that is restartable, making it necessary for these emulation sequences to explicitly disable and enable interrupts.

A better solution may be simply to provide a lightweight mechanism for deferring interrupts during complex emulation code. The r4 register, which is normally used to store a pointer to the virtual CPU state, can simultaneously be used to store an interrupt deferral flag, avoiding the need for extra scratch registers. Consider if the hypervisor initialises r4 to one byte before the virtual CPU structure. A critical section might then be constructed as follows:

add

$$r4=1,r4$$

...

(5)

Within the critical section, r4 points to the virtual CPU structure; outside the critical section, r4 points one byte below it. In either case the members can be accessed using offsets, and the hypervisor can easily determine whether interrupts should be deferred by checking the lowest bit of r4.

However, this is not sufficient; there needs to be a lightweight mechanism by which interrupts are finally delivered when the critical section completes. A number of options are possible:

- The hypervisor could re-attempt delivery of the interrupt after a certain time period. However, this has the usual drawbacks of a timed backoff approach: if the timer is set too short, the critical section may not complete before timer fires; if the timer is set too long, interrupt latency suffers.

- The hypervisor could write to a predicate register to indicate a pending interrupt. This predicate register can then be tested in a single instruction at the close of the critical section:

4.2. CHALLENGES 37

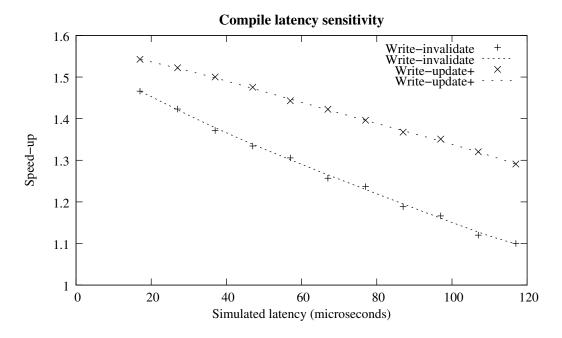

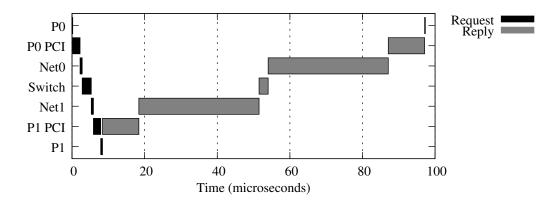

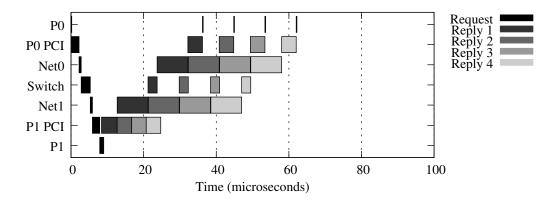

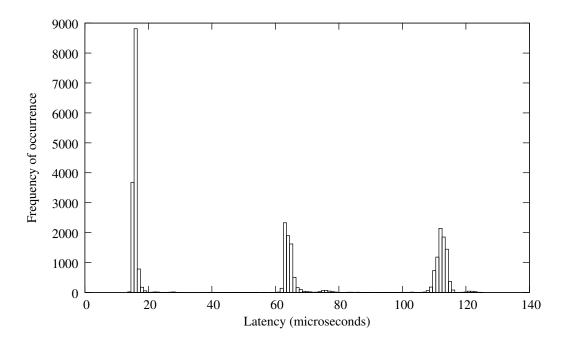

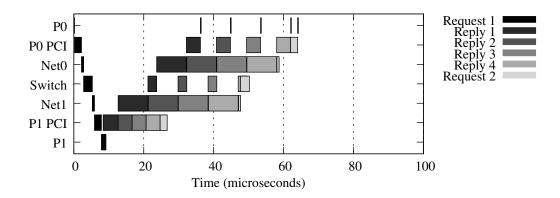

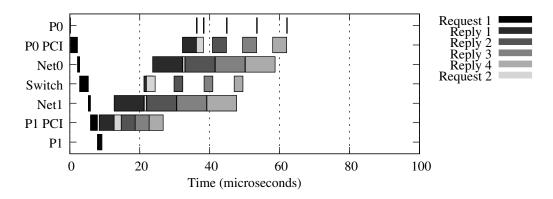

While simple, this solution is less attractive since it necessitates hijacking a predicate register from the operating system, and requires an additional instruction at the end of each critical section.