# L4 Reference Manual

# MIPS R4x00

Version 1.11

Kernel Version 79

Kevin Elphinstone, Gernot Heiser School of Computer Science and Engineering The University of New South Wales Sydney 2052, Australia {kevine,gernot}@cse.unsw.edu.au

Jochen Liedtke IBM T. J. Watson Research Center 30 Saw Mill River Road, Hawthorne, NY 10532, USA jochen@us.ibm.com

May 3, 1999 Change bars indicate modifications relative to UNSW-CSE-TR-9709 (December 1997, Reference Manual Version 1.0, Kernel Version 70)

School of Computer Science and Engineering The University of New South Wales Sydney 2052, Australia

## Note

This document describes release 1.0 of the L4 microkernel for the MIPS R4x00 microprocessor family. It is based on the L4/x86 reference manual Version 2.0 by Jochen Liedtke and has been modified to describe the MIPS implementation. Some material has been added to clarify the L4 message structure. Comments and critiques, as well as proposed additions and alternatives for future versions are most welcome.

The source code for L4/R4x00 is available free of charge under the terms of the GNU General Public License. To obtain the source contact disy@cse.unsw.edu.au. Future versions of this document, as well as related documents and tools, will be available from URL http://www.cse.unsw.edu.au/~disy/.

## How To Read This Manual

This reference manual consists of two parts, (1) a processor-independent description of the principles and mechanisms of L4 and (2) a more detailed processor-specific description. Part 2 refers to the IDT R4x00.

Where L4/MIPS differs from L4/x86 significantly, or something is partially or completely unimplemented, then an implementation note appears as below. There is also a summary of various implementation details in section 2.1.

**MIPS Implementation Note:** This is what an implementation note looks like.

# Acknowledgements

The original L4 reference manual was written by Jochen Liedtke, who would like to thank many people for their helpful contributions for improving the reference manual and the L4 interface. Particular thanks go to Bryan Ford, Hermann Härtig, Michael Hohmuth, Sebastian Schönberg and Jean Wolter. For the MIPS version we would like to thank in particular Jerry Vochteloo for testing the kernel, Alan Au for contributions to the manual, as well as the 1997 class of UNSW COMP9242 "guinea pigs" who built their operating systems on top of the MIPS version of the kernel.

Permission to make digital/hard copy of part or all of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage, the copyright notice, the title of the publication and its date appear, and notice is given that copying is by permission of the authors. To copy otherwise, to republish, to post on servers, or to redistribute to lists requires prior specific permission and/or a fee.

Copyright ©1997, 1998 by Gernot Heiser, The University of New South Wales.

# Contents

| 1 | L4 i | n General 7                         |

|---|------|-------------------------------------|

|   | 1.1  | Basic Concepts                      |

|   |      | 1.1.1 Address Spaces                |

|   |      | 1.1.2 Threads and IPC               |

|   |      | 1.1.3 Clans & Chiefs                |

|   |      | 1.1.4 Unique Identifiers            |

|   |      | 1.1.5 Flexibility                   |

|   | 1.2  | Data Types                          |

|   |      | 1.2.1 Unique Ids                    |

|   |      | 1.2.2 User-Level Operations on Uids |

|   |      | 1.2.3 Fpages                        |

|   |      | 1.2.4 Messages                      |

|   | 1.3  | $\mu$ -Kernel Calls                 |

|   |      |                                     |

| 2 | L4/N | MIPS 21                             |

|   | 2.1  | Implementation Notes         21     |

|   |      | 2.1.1 Cache                         |

|   |      | 2.1.2 IPC                           |

|   |      | 2.1.3 Scheduling 21                 |

|   |      | 2.1.4 $\sigma_0$                    |

|   |      | 2.1.5 Exceptions                    |

|   |      | 2.1.6 Interrupts                    |

|   | 2.2  | Notational conventions              |

|   | 2.3  | Data Types                          |

|   |      | 2.3.1 Unique Ids                    |

|   |      | 2.3.2 Fpages                        |

|   |      | 2.3.3 Messages                      |

|   |      | 2.3.4 Timeouts                      |

|   | 2.4  | $\mu$ -Kernel Calls                 |

|   |      | ipc                                 |

|   |      | id_nearest                          |

|   |      | fpage_unmap                         |

|   |      | thread_switch                       |

|   |      | thread_schedule                     |

|   |      | lthread_ex_regs                     |

|   |      | task_new                            |

|   | 2.5  | Exception Handling                  |

|   | 2.6  | The Kernel-Info Page         49     |

|   | 2.7<br>2.8<br>2.9               | $\sigma_0$ RPC protocol | 50<br>51<br>53                          |

|---|---------------------------------|-------------------------|-----------------------------------------|

| Α | DIT                             |                         | 55                                      |

| B |                                 | Output                  | <b>57</b><br>57<br>57                   |

| C | Kerr<br>C.1                     |                         | <b>59</b><br>60                         |

| D | D.1<br>D.2<br>D.3<br>D.4<br>D.5 | types.h                 | <b>61</b><br>67<br>69<br>74<br>76<br>79 |

# **Chapter 1**

# L4 in General

### **1.1 Basic Concepts**

The following section contains excerpts from [Lie93b, Lie93a, Lie95].

We reason about the minimal concepts or "primitives" that a  $\mu$ -kernel should implement.<sup>1</sup> The determining criterion used is functionality, not performance. More precisely, a concept is tolerated inside the  $\mu$ -kernel only if moving it outside the kernel, i.e. permitting competing implementations, would prevent the implementation of the system's required functionality.

We assume that the target system has to support interactive and/or not completely trustworthy applications, i.e. it has to deal with protection. We further assume that the hardware implements page-based virtual memory.

One inevitable requirement for such a system is that a programmer must be able to implement an arbitrary subsystem S in such a way that it cannot be disturbed or corrupted by other subsystems S'. This is the principle of independence: S can give guarantees independent of S'. The second requirement is that other subsystems must be able to rely on these guarantees. This is the principle of integrity: there must be a way for  $S_1$  to address  $S_2$  and to establish a communication channel which can neither be corrupted nor eavesdropped by S'.

Provided hardware and kernel are trustworthy, further security services, like those described by [GGKL89], can be implemented by servers. Their integrity can be ensured by system administration or by user-level boot servers. For illustration: a key server should deliver public-secret RSA key pairs on demand. It should guarantee that each pair has the desired RSA property and that each pair is delivered only once and only to the demander. The key server can only be realized if there are mechanisms which (a) protect its code and data, (b) ensure that nobody else reads or modifies the key and (c) enable the demander to check whether the key comes from the key server. Finding the key server can be done by means of a name server and checked by public key based authentication.

#### 1.1.1 Address Spaces

At the hardware level, an *address space* is a mapping which associates each virtual page to a physical page frame or marks it 'non-accessible'. For the sake of simplicity, we omit access attributes like read-only and read/write. The mapping is implemented by TLB hardware and page tables.

The  $\mu$ -kernel, the mandatory layer common to all subsystems, has to hide the hardware concept of address spaces, since otherwise, implementing protection would be impossible. The  $\mu$ -kernel concept of address spaces must be tamed, but must permit the implementation of arbitrary protection

<sup>&</sup>lt;sup>1</sup>Proving minimality, necessarity and completeness would be nice but is impossible, since there is no agreed-upon metric and all is Turing-equivalent.

(and non-protection) schemes on top of the  $\mu$ -kernel. It should be simple and similar to the hardware concept.

The basic idea is to support recursive construction of address spaces outside the kernel. By magic, there is one address space  $\sigma_0$  which essentially represents the physical memory and is controlled by the first subsystem  $S_0$ . At system start time, all other address spaces are empty. For constructing and maintaining further address spaces on top of  $\sigma_0$ , the  $\mu$ -kernel provides three operations:

**Grant.** The owner of an address space can *grant* any of its pages to another space, provided the recipient agrees. The granted page is removed from the granter's address space and included into the grantee's address space. The important restriction is that instead of physical page frames, the granter can only grant pages which are already accessible to itself.

**Map.** The owner of an address space can *map* any of its pages into another address space, provided the recipient agrees. Afterwards, the page can be accessed in both address spaces. In contrast to granting, the page is not removed from the mapper's address space. Comparable to the granting case, the mapper can only map pages which itself already can access.

**Flush.** The owner of an address space can *flush* any of its pages. The flushed page remains accessible in the flusher's address space, but is removed from all other address spaces which had received the page directly or indirectly from the flusher. Although explicit consent of the affected address-space owners is not required, the operation is safe, since it is restricted to own pages. The users of these pages already agreed to accept a potential flushing, when they received the pages by mapping or granting.

#### Reasoning

The described address-space concept leaves memory management and paging outside the  $\mu$ -kernel; only the grant, map and flush operations are retained inside the kernel. Mapping and flushing are required to implement memory managers and pagers on top of the  $\mu$ -kernel.

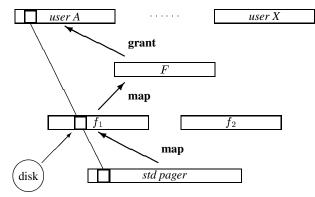

The grant operation is required only in very special situations: consider a pager F which combines two underlying file systems (implemented as pagers  $f_1$  and  $f_2$ , operating on top of the standard pager) into one unified file system (see figure 1.1). In this example,  $f_1$  maps one of its pages to F

Figure 1.1: A Granting Example.

which grants the received page to *user A*. By granting, the page disappears from F so that it is then available only in  $f_1$  and *user A*; the resulting mappings are denoted by the thin line: the page is mapped in *user A*,  $f_1$  and the standard pager. Flushing the page by the standard pager would affect  $f_1$  and *user A*, flushing by  $f_1$  only *user A*. F is not affected by either flush (and cannot flush itself), since it used the page only transiently. If F had used mapping instead of granting, it would have needed to replicate most of the bookkeeping which is already done in  $f_1$  and  $f_2$ . Furthermore, granting avoids a potential address-space overflow of F.

In general, granting is used when page mappings should be passed through a controlling subsystem without burdening the controller's address space by all pages mapped through it.

The model can easily be extended to access rights on pages. Mapping and granting copy the source page's access right or a subset of them, i.e., can restrict the access but not widen it. Special flushing operations may remove only specified access rights.

### I/O

An address space is the natural abstraction for incorporating device ports. This is obvious for memory mapped I/O, but I/O ports can also be included. The granularity of control depends on the given processor. The 386 and its successors permit control per port (one very small page per port) but no mapping of port addresses (it enforces mappings with v=v'); the PowerPC uses pure memory mapped I/O, i.e., device ports can be controlled and mapped with 4K granularity. Controlling I/O rights and device drivers is thus also done by memory managers and pagers on top of the  $\mu$ -kernel.

#### An Abstract Model of Address Spaces

We describe address spaces as mappings.  $\sigma_0: V \to R \cup \{\phi\}$  is the initial address space, where V is the set of virtual pages, R the set of available physical (real) pages and  $\phi$  the nilpage which cannot be accessed. Further address spaces are defined recursively as mappings  $\sigma: V \to (\Sigma \times V) \cup \{\phi\}$ , where  $\Sigma$  is the set of address spaces. It is convenient to regard each mapping as a one column table which contains  $\sigma(v)$  for all  $v \in V$  and can be indexed by v. We denote the elements of this table by  $\sigma_v$ .

All modifications of address spaces are based on the replacement operation: we write  $\sigma_v \leftarrow x$  to describe a change of  $\sigma$  at v, precisely:

flush

$$(\sigma, v)$$

;  $\sigma_v := x$  .

A page potentially mapped at v in  $\sigma$  is flushed, and the new value x is copied into  $\sigma_v$ . This operation is internal to the  $\mu$ -kernel. We use it only for describing the three exported operations.

A subsystem S with address space  $\sigma$  can *grant* any of its pages v to a subsystem S' with address space  $\sigma'$  provided S' agrees:

$$\sigma'_{v'} \leftarrow \sigma_v \quad , \quad \sigma_v \leftarrow \phi \quad .$$

Note that S determines which of its pages should be granted, whereas S' determines at which virtual address the granted page should be mapped in  $\sigma'$ . The granted page is transferred to  $\sigma'$  and removed from  $\sigma$ .

A subsystem S with address space  $\sigma$  can map any of its pages v to a subsystem S' with address space  $\sigma'$  provided S' agrees:

$$\sigma'_{v'} \leftarrow (\sigma, v)$$

In contrast to grant, the mapped page remains in the mapper's space  $\sigma$  and a link to the page in the mapper's address space  $(\sigma, v)$  is stored in the receiving address space  $\sigma'$ , instead of transferring the existing link from  $\sigma_v$  to  $\sigma'_{v'}$ . This operation permits to construct address spaces recursively, i.e. new spaces based on existing ones.

Flushing, the reverse operation, can be executed without explicit agreement of the mappees, since they agreed implicitly when accepting the prior map operation. *S* can *flush* any of its pages:

$$\forall_{\sigma'_{v'}=(\sigma,v)}: \sigma'_{v'} \leftarrow \phi$$

Note that  $\leftarrow$  and *flush* are defined recursively. Flushing recursively affects also all mappings which are indirectly derived from  $\sigma_v$ .

No cycles can be established by these three operations, since  $\leftarrow$  flushes the destination prior to copying.

#### **Implementing the Model**

At a first glance, deriving the physical address of page v in address space  $\sigma$  seems to be rather complicated and expensive:

$$\sigma(v) = \begin{cases} \sigma'(v') & \text{if } \sigma_v = (\sigma', v') \\ r & \text{if } \sigma_v = r \\ \phi & \text{if } \sigma_v = \phi \end{cases}$$

Fortunately, a recursive evaluation of  $\sigma(v)$  is never required. The three basic operations guarantee that the physical address of a virtual page will never change, except by flushing. For implementation, we therefore complement each  $\sigma$  by an additional table P, where  $P_v$  corresponds to  $\sigma_v$  and holds either the physical address of v or  $\phi$ . Mapping and granting then include

$$P'_{v'} := P_v$$

and each replacement  $\sigma_v \leftarrow \phi$  invoked by a flush operation includes

$$P_v := \phi$$

$P_v$  can always be used instead of evaluating  $\sigma(v)$ . In fact, P is equivalent to a hardware page table.  $\mu$ -kernel address spaces can be implemented straightforward by means of the hardware-addresstranslation facilities.

The recommended implementation of  $\sigma$  is to use one mapping tree per physical page frame which describes all actual mappings of the frame. Each node contains (P, v), where v is the according virtual page in the address space which is implemented by the page table P.

Assume that a grant-, map- or flush-operation deals with a page v in address space  $\sigma$  to which the page table P is associated. In a first step, the operation selects the according tree by  $P_v$ , the physical page. In the next step, it selects the node of the tree that contains (P, v). (This selection can be done by parsing the tree or in a single step, if  $P_v$  is extended by a link to the node.) Granting then simply replaces the values stored in the node and map creates a new child node for storing (P', v'). Flush lets the selected node unaffected but parses and erases the complete subtree, where  $P'_v := \phi$  is executed for each node (P', v') in the subtree.

### 1.1.2 Threads and IPC

A *thread* is an activity executing inside an address space. A thread  $\tau$  is characterised by a set of registers, including at least an instruction pointer, a stack pointer and a state information. A thread's state also includes the address space  $\sigma^{(\tau)}$  in which  $\tau$  currently executes. This dynamic or static association to address spaces is the decisive reason for including the thread concept (or something equivalent) in the  $\mu$ -kernel. To prevent corruption of address spaces, all changes to a thread's address space ( $\sigma^{(\tau)} := \sigma'$ ) must be controlled by the kernel. This implies that the  $\mu$ -kernel includes the notion of some  $\tau$  that represents the above mentioned activity. In some operating systems, there may be additional reasons for introducing threads as a basic abstraction, e.g. preemption. Note that choosing a concrete thread concept remains subject to further OS-specific design decisions.

Consequently, cross-address-space communication, also called inter-process communication (IPC), must be supported by the  $\mu$ -kernel. The classical method is transferring messages between threads by the  $\mu$ -kernel.

IPC always enforces a certain agreement between both parties of a communication: the sender decides to send information and determines its contents; the receiver determines whether it is willing to receive information and is free to interpret the received message. Therefore, IPC is not only the basic concept for communication between subsystems but also, together with address spaces, the foundation of independence.

Other forms of communication, remote procedure call (RPC) or controlled thread migration between address spaces, can be constructed from message-transfer based IPC.

Note that the *grant* and *map* operations (section 1.1.1) need IPC, since they require an agreement between granter/mapper and recipient of the mapping.

#### Interrupts

The natural abstraction for hardware interrupts is the IPC message. The hardware is regarded as a set of threads which have special thread ids and send empty messages (only consisting of the sender id) to associated software threads. A receiving thread concludes from the message source id, whether the message comes from a hardware interrupt and from which interrupt:

```

driver thread:

do

wait for (msg, sender) ;

if sender = my hardware interrupt

then read/write io ports ;

reset hardware interrupt

else ...

fi

od .

```

Transforming the interrupts into messages must be done by the kernel, but the  $\mu$ -kernel is not involved in device-specific interrupt handling. In particular, it does not know anything about the interrupt semantics. On some processors, resetting the interrupt is a device specific action which can be handled by drivers at user level. The iret-instruction then is used solely for popping status information from the stack and/or switching back to user mode and can be hidden by the kernel. However, if a processor requires a privileged operation for releasing an interrupt, the kernel executes this action implicitly when the driver issues the next IPC operation.

### 1.1.3 Clans & Chiefs

Within all systems based on direct message transfer, protection is essentially a matter of message control. Using access control lists (acl) this can be done at the server level, but maintenance of large distributed acls becomes hard when access rights change rapidly. So [HKK93] have proposed that object (passive entity) protection be complemented by subject (active entity) restrictions. In this approach the kernel is able to restrict the outgoing messages of a task (the subject) by means of a list of permitted receivers.

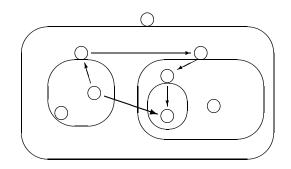

The clan concept [Lie92] is an algorithmic generalisation of this idea:

A *clan* (denoted as an oval) is a set of tasks (denoted as a circle) headed by a *chief* task. Inside the clan all messages are transferred freely and the kernel guarantees message integrity. But whenever a message tries to cross a clan's borderline, regardless of whether it is outgoing or incoming, it is redirected to the clan's chief. This chief may inspect the message (including the sender and receiver ids as well as the contents) and decide whether or not it should be passed to the destination to which it was addressed. As demonstrated in the figure above, these rules apply to nested clans as well. Obviously subject restrictions and local reference monitors can be implemented outside the kernel by means of clans. Since chiefs are tasks at user level, the clan concept allows more sophisticated and user definable checks as well as active control. Typical clan structures are

- **Clan per machine:** In this simple model there is only one clan per machine covering all tasks. Local communication is handled directly by the kernel without incorporating a chief, whereas cross machine communication involves the chief of the sending and the receiving machine. Hence, the clan concept is used for implementing remote ipc by user level tasks.

- **Clan per system version:** Sometimes chiefs are used for adapting different versions. The servers of the old or new versions are encapsulated by a clan so that its chief can translate the messages.

- **Clan per user:** Surrounding the tasks of each user or user group by a clan is a typical method when building security systems. Then the chiefs are used to control and enforce the requested security policy.

- **Clan per task:** In the extreme case there are single tasks each controlled by a specific chief. For example these one-task-clans are used for debugging and supervising suspicious programs.

In the case of intra-clan communication (no chief involved), the additional costs of the clan concept are negligible (below 1% of minimal ipc time). Inter-clan communication however multiplies the ipc operations by the number of chiefs involved. This can be tolerated, since (i) L4 ipc is very fast (see above) and (ii) crossing clan boundaries occurs seldom enough in practice. Note that many security policies can be implemented simply by checking the client id in the server and do not need clans.

### 1.1.4 Unique Identifiers

A  $\mu$ -kernel must supply unique identifiers (uid) for something, either for threads or tasks or communication channels. Uids are required for reliable and efficient local communication. If  $S_1$  wants to send a message to  $S_2$ , it needs to specify the destination  $S_2$  (or some channel leading to  $S_2$ ). Therefore, the  $\mu$ -kernel must know which uid relates to  $S_2$ . On the other hand, the receiver  $S_2$  wants to be sure that the message comes from  $S_1$ . Therefore the identifier must be unique, both in space and time. In theory, cryptography could also be used. In practice, however, enciphering messages for local communication is far too expensive and the kernel must be trusted anyway.  $S_2$  can also not rely on purely user-supplied capabilities, since  $S_1$  or some other instance could duplicate and pass them to untrusted subsystems without control of  $S_2$ .

### 1.1.5 Flexibility

To illustrate the flexibility of the basic concepts, we sketch some applications which typically belong to the basic operating system but can easily be implemented on top of the  $\mu$ -kernel.

**Memory Manager.** A server managing the initial address space  $\sigma_0$  is a classical main memory manager, but outside the  $\mu$ -kernel. Memory managers can easily be stacked:  $M_0$  maps or grants parts of the physical memory ( $\sigma_0$ ) to  $\sigma_1$ , controlled by  $M_1$ , other parts to  $\sigma_2$ , controlled by  $M_2$ . Now we have two coexisting main memory managers.

**Pager.** A Pager may be integrated with a memory manager or use a memory managing server. Pagers use the  $\mu$ -kernel's grant, map and flush primitives. The remaining interfaces, pager – client, pager – memory server and pager – device driver, are completely based on IPC and are user-level defined.

Pagers can be used to implement traditional paged virtual memory and file/database mapping into user address spaces as well as unpaged resident memory for device drivers and/or real time systems. Stacked pagers, i.e. multiple layers of pagers, can be used for combining access control with existing pagers or for combining various pagers (e.g. one per disk) into one composed object. User-supplied paging strategies [LCC94, CFL94] are handled at the user level and are in no way restricted by the  $\mu$ -kernel. Stacked file systems [KN93] can be realized accordingly.

**Multimedia Resource Allocation.** Multimedia and other real-time applications require memory resources to be allocated in a way that allows predictable execution times. The above mentioned user-level memory managers and pagers permit e.g. fixed allocation of physical memory for specific data or locking data in memory for a given time.

Note that resource allocators for multimedia and for timesharing can coexist. Managing allocation conflicts is part of the servers' jobs.

**Device Driver.** A device driver is a process which directly accesses hardware I/O ports mapped into its address space and receives messages from the hardware (interrupts) through the standard IPC mechanism. Device-specific memory, e.g. a screen, is handled by means of appropriate memory managers. Compared to other user-level processes, there is nothing special about a device driver. No device driver has to be integrated into the  $\mu$ -kernel.<sup>2</sup>

**Second Level Cache and TLB.** Improving the hit rates of a secondary cache by means of page allocation or reallocation [KH92, RLBC94] can be implemented by means of a pager which applies some cache-dependent (hopefully conflict reducing) policy when allocating virtual pages in physical memory.

In theory, even a software TLB handler could be implemented like this. In practice, the firstlevel TLB handler will be implemented in the hardware or in the  $\mu$ -kernel. However, a second-level

$<sup>^{2}</sup>$ In general, there is no reason for integrating boot drivers into the kernel. The booter, e.g. located in ROM, simply loads a bit image into memory that contains the micro-kernel and perhaps some set of initial pagers and drivers (running in user mode and *not* linked but simply appended to the kernel). Afterwards, the boot drivers are no longer used.

TLB handler, e.g. handling misses of a hashed page table, might be implemented as a user-level server.

**Remote Communication.** Remote IPC is implemented by communication servers which translate local messages to external communication protocols and vice versa. The communication hardware is accessed by device drivers. If special sharing of communication buffers and user address space is required, the communication server will also act as a special pager for the client. The  $\mu$ -kernel is not involved.

**Unix Server.** Unix<sup>3</sup> system calls are implemented by IPC. The Unix server can act as a pager for its clients and also use memory sharing for communicating with its clients. The Unix server itself can be page-able or resident.

**Conclusion.** A small set of  $\mu$ -kernel concepts lead to abstractions which stress flexibility, provided they perform well enough. The only thing which cannot be implemented on top of these abstractions is the processor architecture, registers, first-level caches and first-level TLBs.

<sup>&</sup>lt;sup>3</sup>Unix is a registered trademark of UNIX System Laboratories.

## 1.2 Data Types

### 1.2.1 Unique Ids

Unique ids identify tasks, threads and hardware interrupts. They are also unique in time. Unique ids are 64-bit values.

### 1.2.2 User-Level Operations on Uids

| a = b:               | a = b                                                                                                   |

|----------------------|---------------------------------------------------------------------------------------------------------|

| task(a) = task(b):   | (a AND NOT lthread mask) = (b AND NOT lthread mask)                                                     |

| chief(a) = chief(b): | (a AND NOT chief mask) = (b AND NOT chief mask)                                                         |

| site(a) = site (b) : | (a AND NOT site mask) = (b AND NOT site mask)                                                           |

| lthread no(a) :      | (a AND lthread mask) SHR lthread shift extract lthread no from thread id a                              |

| thread(a,n) :        | (a AND NOT lthread mask) + (n SHL lthread shift)<br>construct thread id from task id a and lthread no n |

| task no(a) :         | (a AND task mask) SHR task shift                                                                        |

| chief no(a) :        | (a AND chief mask) SHR chief shift                                                                      |

| site no(a) :         | (a AND site mask) SHR site shift                                                                        |

### 1.2.3 Fpages

Fpages (Flexpages) are regions of the virtual address space. An fpage consists of all pages actually mapped in this region. The minimal fpage size is the minimal hardware-page size.

An fpage of size  $2^s$  has a  $2^s$ -aligned base address b, i.e.  $b \mod 2^s = 0$ . An fpage with base address b and size  $2^s$  is denoted by the 64-bit value

b+4s.

On R4x00 processors, the smallest possible value for s is 12, since the hardware page size is 4K.

### 1.2.4 Messages

S :: snd ; EMPTY .

$R::rcv\ ; EMPTY$  .

EMPTY :: .

| S R message:         | rcv fpage option ,<br>size dope ,<br>S R msg dope ,<br>S R mwords ,<br>S R string dopes .                                                  |                                                              |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| rcv fpage option:    | rcv fpage:fpage ;<br>zero:word.                                                                                                            |                                                              |

| size dope:           | reserved:byte ,<br>string dope number:5bits ,<br>mwords number:19bits .                                                                    | $= S \\= W$                                                  |

| snd R msg dope:      | undefined:byte ,<br>string dope number:5bits ,<br>mwords number:19bits .                                                                   | $egin{array}{lll} &=s & s\leq S \ &=w & w\leq W \end{array}$ |

| rcv msg dope:        | undefined:word.                                                                                                                            |                                                              |

| snd R mwords:        | $w \times \text{send}$ receive word ,<br>$(W - w) \times \text{receive word}$ ;                                                            |                                                              |

|                      | $m \times \text{snd}$ fpage receive double word ,<br>$w - 2m \times \text{send}$ receive words ,<br>$(W - w) \times \text{receive}$ word . | $2m \le w$                                                   |

| rcv mwords:          | W 	imes receive word .                                                                                                                     |                                                              |

| snd R string dopes:  | $s \times \text{snd } \mathbf{R}$ string dope ,<br>$(S-s) \times \mathbf{R}$ string dope .                                                 |                                                              |

| rcv string dopes:    | S 	imes rcv string dope .                                                                                                                  |                                                              |

| snd rcv string dope: | snd addr:word ,<br>snd size:word ,<br>rcv addr:word ,<br>rcv size:word .                                                                   | $\leq 4MB$<br>$\leq 4MB$                                     |

| snd string dope:     | snd addr:word ,<br>snd size:word ,<br>undefined:word ,<br>undefined:word .                                                                 | $\leq 4MB$                                                   |

| rcv string dope:     | undefined:word ,<br>undefined:word ,<br>rcv addr:word ,<br>rcv size:word .                                                                 | $= s_r \qquad s_r \leq 4 \mathrm{MB}$                        |

snd map fpage: grant flag:1bit , write flag:1bit , snd base:30bits , snd fpage:fpage .

# **1.3** $\mu$ -Kernel Calls

| ірс          | (dest option, snd descriptor option, rcv descriptor option, timeouts) $\rightarrow$ (source option, result code) |

|--------------|------------------------------------------------------------------------------------------------------------------|

| CALL         | (dest, snd descriptor, closed rcv descriptor, timeouts) $\rightarrow$ (dest option, result code)                 |

| REPLY & WAIT | (dest, snd descriptor, open rcv descriptor, timeouts) $\rightarrow$ (source option, result code)                 |

| SEND         | (dest, snd descriptor, –nil– , timeouts) $\rightarrow$ (~, result code)                                          |

| RECEIVE FROM | (source, $-nil-$ , closed rcv descriptor, timeouts)<br>$\rightarrow$ (source option, result code)                |

| WAIT         | <ul> <li>(~, -nil-, open rcv descriptor, timeouts)</li> <li>→ (source option, result code)</li> </ul>            |

| RECEIVE INTR | (intr, $-nil-$ , closed rcv descriptor, timeouts)<br>$\rightarrow$ (source option, result code)                  |

| SLEEP        | (-nil- , -nil- , closed rcv descriptor, timeouts) $\rightarrow$ (~, result code)                                 |

| id_nearest   | (dest id) $\rightarrow$ (nearest id)                                                                             |

| fpage_unmap                                                                                                                                              | (fpage, map mask) $\rightarrow$ ()                                                                             |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--|--|--|

| thread_switch                                                                                                                                            | $(dest) \rightarrow ()$                                                                                        |  |  |  |

| lthread_ex_regs                                                                                                                                          | (lthread no, SP, IP, excpt, pager)<br>$\rightarrow$ (FLAGS, SP, IP, excpt, pager)                              |  |  |  |

| <b>MIPS Implementation Note:</b> Added exception handler identifier (see section 2.5), and removed preempter which is currently not supported in L4/MIPS |                                                                                                                |  |  |  |

| thread_schedule                                                                                                                                          | (dest, prio, timeslice, ext preempter)<br>$\rightarrow$ (prio, timeslice, state, ext preempter, partner, time) |  |  |  |

| task_new                                                                                                                                                 | (dest task id, mcp/new chief, SP, IP, pager id, excpt id) $\rightarrow$ (new task id)                          |  |  |  |

| MIPS Implementation                                                                                                                                      | Note: Added an exception handler identifier (see section 2.5)                                                  |  |  |  |

# Chapter 2

# L4/MIPS

# L4/R4x00

## 2.1 Implementation Notes

What follows is a list of implementation details of the current L4/MIPS implementation. It is here to serve as a quick reference as to what may or may not be implemented for those that are familiar with L4/x86.

### 2.1.1 Cache

The R4600 has 16KB data cache and 16KB instruction cache. Both are two-way associative, virtually indexed with physical tags. The data cache has either a write-through or write-back policy.

To avoid aliasing problems, shared memory regions must lie at the same offset from a 8KB boundary in the virtual address space.

I envisage adding a MIPS specific system call in the future to perform cache management functions. This will allow write-back caching to once again be re-enabled.

### 2.1.2 IPC

- Granting is not supported.

- Sending multiple fpages is supported in registers only, i.e. up to 3 valid fpages plus the terminating nil fpage. Sending fpages in memory based messages is not supported.

- Dwords sent in memory based messages are 64-bit, not 32-bit as in L4/x86. This allows sending direct messages of up to 4MB in size.

- Indirect strings can be up to 4MB in size.

### 2.1.3 Scheduling

- The current scheduler uses a multi-level round robin scheme with absolute priorities (0-255).

- Internal and external preempters are not supported.

- Constant interrupts will prevent other threads from running.

## **2.1.4** *σ*<sub>0</sub>

- Multiple mappings of the same physical frame is not supported.

- The RPC protocol is slightly different, see section 2.8 for details.

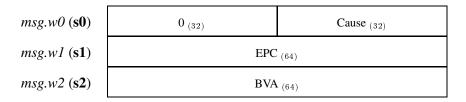

### 2.1.5 Exceptions

Exceptions are handled using IPC. Each thread has it's own exception handling thread, see section 2.5 for details.

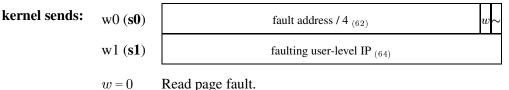

### 2.1.6 Interrupts

Interrupts are handled using IPC. Each level of interrupt may have an associated handler thread, see the ipc part of section 2.4 for how this is done. When an interrupt occurs, the associate handler (if any) is notified via ipc.

## 2.2 Notational conventions

- $\sim$  If this refers to an input parameter, its value is meaningless. If it refers to an output parameter, its value is undefined.

- **a0,a1**... denote the processor's general registers. Note that the SGI 64-bit ABI register names are used.

# 2.3 Data Types

### 2.3.1 Unique Ids

Unique ids identify tasks, threads and hardware interrupts. Each unique id is a 64-bit value which is unique in time. A unique id in R4x00 format consists of a single 64-bit word:

| thread id    | nest (4) | chief (11)     | site (17)           |           |

|--------------|----------|----------------|---------------------|-----------|

|              | ver1 (4) | task $_{(11)}$ | lthread (7)         | ver0 (10) |

|              |          |                |                     |           |

| task id      | nest (4) | chief (11)     | site (17)           |           |

|              | ver1 (4) | task (11)      | 0 (7)               | ver0 (10) |

|              |          |                |                     |           |

| interrupt id |          | 0 (61)         | 0 (61) intr + 1 (3) |           |

| nil id     | 0 (64)                                 |

|------------|----------------------------------------|

|            |                                        |

| invalid id | 0xFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFF |

### 2.3.2 Fpages

Fpages (Flexpages) are regions of the virtual address space. An fpage designates all pages actually mapped in this region. The minimal fpage size is 4 K, the minimal hardware-page size.

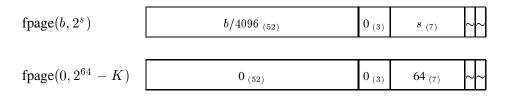

An fpage of size  $2^s$  has a  $2^s$ -aligned base address b, i.e.  $b \mod 2^s = 0$ . On the R4x00 processors, the smallest possible value for s is 12, since hardware pages are at least 4K. The complete user address space (base address 0, size  $2^{64} - K$ , where K is the size of the kernel area) is denoted by b = 0, s = 64. An fpage with base address b and size  $2^s$  is denoted by a 64-bit word:

**MIPS Implementation Note:** The user address space on the R4600 is one terabyte  $(2^{40})$  beginning at 0x0. Values of  $s \ge 40$  are equivalent, however if the intention is to specify the whole address space one should of course use s = 64 for future compatibility.

#### 2.3.3 Messages

A message contains between  $2^6$  and  $2^{22} + 2^6$  bytes of in-line data (**mwords**). The first 64 bytes (eight dwords) are transfered via registers, the (optional) remainder is contained in a dword-aligned memory buffer pointed to by a *message descriptor*. Every successful IPC operation will always copy at least eight dwords to the receiver.

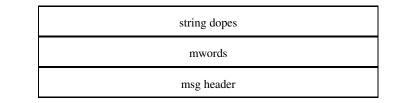

The buffer pointed to by the optional message descriptor contains a 3 dword message header, followed by a number of mwords, followed by a number of *string dopes*. The number of mwords (in 64-bit dwords, excluding those copied in registers) and string dopes is specified in the message header.

message:

The beginning of the message buffer has the following format:

|                       |              | :               |                  |              | _   |

|-----------------------|--------------|-----------------|------------------|--------------|-----|

|                       |              | dword 1 $_{(e}$ | 54)              |              | +32 |

| msg dwords:           | dword 0 (64) |                 |                  | +24          |     |

| msg snd dope:         | 0 (32)       | dwords (19)     | strings (5)      | <b>~</b> (8) | +16 |

| msg size dope:        | 0 (32)       | dwords (19)     | strings $_{(5)}$ | <b>~</b> (8) | +8  |

| msg rcv fpage option: | fpage (64)   |                 |                  | +0           |     |

The *receive fpage* describes the address range in which the caller is willing to accept fpage mappings or grants in the receive part (if any) of the IPC. The *size dope* defines the size (in dwords) of the mword buffer (and hence the offset of the string dopes from the end of the header), and the number of string dopes.

The *send dope* specifies how many dwords and strings are actually to be sent. (Specifying send dope values less than the size dope values makes sense when the caller is willing to receive more data than sending.)

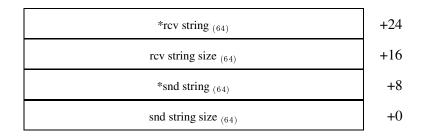

*Strings* are out-of-line by-value data. Their size and location is specified by the corresponding string dopes. The string dope format is:

string dope:

The first part of the string dope specifies the size and location of the string the caller wants sent to the destination, while the second part specifies the size and location of a buffer where the caller is willing to receive a string. **Note** that strings do not have to be aligned, and that their size is specified in *bytes*.

The in-line part of the message consists of the eight dwords passed in registers followed by any dwords specified by the message descriptor. This part consists of optional *fpage descriptors* followed by by-value data. If the receiver of an IPC has specified a valid *receive fpage*, the kernel will interpret each pair of dwords of the in-line part as fpage descriptors, until an invalid descriptor is encountered. This and any further dwords are then passed by value.

MIPS Implementation Note: Presently at most three fpages can be passed on the R4600.

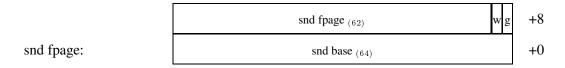

The format of an fpage descriptor is:

The first word contains the address of the *hot spot*, while the second word describes the sender's fpage in the format given in Sect. 2.3.2. The *g*-bit, if set, indicates that the fpage is to be *granted*

to the receiver, otherwise it is just *mapped*. The *w*-bit indicates whether the receiver will be given write or read-only access to the address-space region.

Each fpage specified by the sender is mapped individually into the address-space window specified by the receiver's *receive fpage*. If the sender and receiver specify different fpage sizes, the hot-spot specification is used to determine how the mapping between the two different size fpages occurs: If  $2^s$  is the size of the larger, and  $2^t$  the size of the smaller fpage, then the larger fpage can be thought as being tiled by  $2^{s-t}$  fpages of the smaller size. One of these is uniquely identified as containing the hot spot address (mod  $2^s$ ). This is the fpage which will actually be mapped.

The kernel refuses to map or grant a page over an existing mapping in the receiver's address space; an attempt to perform such a mapping will be treated as a no-op. There is one exception: If the receiver's page is already mapped to the same page as the present IPC attempts to map it (i.e. the mapping operation would not change the association of the receiver's page with physical memory) then the write permission on the receiver's page is set according to the *w*-bit of the sender's fpage descriptor. In other words, such an operation can be used to change a mapping from R/O to writable or vice versa.

If the sender provides several fpage descriptors which attempt to define conflicting mappings for one of the receiver's pages, the result is undefined.

**MIPS Implementation Note:** The current message headers are not as compact as they could be. They will be optimised in a future version.

#### 2.3.4 Timeouts

Timeouts are used to control ipc operations. The *send timeout* determines how long ipc should try to send a message. If the specified period is exhausted without that message transfer could start, ipc fails. The *receive timeout* specifies how long ipc should wait for an incoming message. Both timouts specify the maximum period of time *before message transfer starts*. Once started, message transfer is no longer influenced by send or receive timeout.

Pagefaults occuring during ipc are controlled by *send* and *receive pagefault timeout*. A pagefault is translated to an RPC by the kernel. In the case of a pagefault in the receiver's address space, the corresponding RPC to the pager uses *send pagefault timeout* (specified by the sender) for both send and receive timeout. In the case of a pagefault in the sender's address space, *receive pagefault timeout* specified by the receiver is taken.

Besides the special timeouts 0 (do not wait at all) and  $\infty$  (wait forever), periods from 1  $\mu$ s up to approximately 19 hours can be specified. The complete quadruple is packed into one 32-bit word:

| $m_{r\ (8)}$ $m_{s\ (8)}$ $p_{r\ (4)}$ $p_{s\ (4)}$ $e_{s\ (4)}$ $e_{r\ (4)}$ |

|-------------------------------------------------------------------------------|

|-------------------------------------------------------------------------------|

snd timeout =

$$\begin{cases} \infty & \text{if } e_s = 0 \\ 4^{15 - e_s} m_s \mu s & \text{if } e_s > 0 \\ 0 & \text{if } m_s = 0, e_s \neq 0 \end{cases}$$

rcv timeout =

$$\begin{cases} \infty & \text{if } e_r = 0 \\ 4^{15 - e_r} m_r \mu s & \text{if } e_r > 0 \\ 0 & \text{if } m_r = 0, e_r \neq 0 \end{cases}$$

snd pagefault timeout =

$$\begin{cases} \infty & \text{if } p_s = 0\\ 4^{15-p_s} \mu s & \text{if } 0 < p_s < 15\\ 0 & \text{if } p_s = 15 \end{cases}$$

rcv pagefault timeout =

$$\begin{cases} \infty & \text{if } p_r = 0\\ 4^{15-p_r} \mu s & \text{if } 0 < p_r < 15\\ 0 & \text{if } p_r = 15 \end{cases}$$

| appr                 | oximate timeout rang            | es            |

|----------------------|---------------------------------|---------------|

| $e_s, e_r, p_s, p_r$ | snd/rcv timeout                 | pf timeout    |

| 0                    | $\infty$                        | $\infty$      |

| 1                    | 256 s 19 h                      | 256 s         |

| 2                    | 64 s 55 h                       | 64 s          |

| 3                    | 16 s 71 m                       | 16 s          |

| 4                    | 4 s 17 m                        | 4 s           |

| 5                    | 1 s 4 m                         | 1 s           |

| 6                    | 262 ms 67 s                     | 256 ms        |

| 7                    | 65 ms 17 s                      | 64 ms         |

| 8                    | 16 ms 4 s                       | 16 ms         |

| 9                    | 4 ms 1 s                        | 4 ms          |

| 10                   | 1 ms 261 ms                     | 1 ms          |

| 11                   | 256 μs 65 ms                    | $256 \ \mu s$ |

| 12                   | 64 $\mu$ s 16 ms                | $64 \ \mu s$  |

| 13                   | $16 \ \mu s \ \dots \ 4 \ ms$   | $16 \ \mu s$  |

| 14                   | $4  \mu s  \dots  1  ms$        | $4 \ \mu s$   |

| 15                   | $1 \ \mu s \ \dots 255 \ \mu s$ | 0             |

| m=0, e>0             | 0                               | _             |

**MIPS Implementation Note:** Timeouts presently have millisecond granularity. Specified microsecond timeouts are therefore rounded down (truncated) to the nearest millisecond, say x. Actual timeout will then occur anywhere in the interval [ct + x - 1, ct + x], where ct is the current time in milliseconds.

# **2.4** $\mu$ -Kernel Calls

System calls are implemented using the syscall instruction in conjunction with the **AT** register which is set to the system call number prior to the call. All registers, unless otherwise stated, are returned undefined after the system call except for the stack pointer **sp**.

This section describes the 7 system calls of L4:

| • ipc             | <b>AT</b> 0 |

|-------------------|-------------|

| • id_nearest      | <b>AT</b> 2 |

| • fpage_unmap     | <b>AT</b> 1 |

| • thread_switch   | <b>AT</b> 4 |

| • thread_schedule | <b>AT</b> 5 |

| • lthread_ex_regs | <b>AT</b> 6 |

| • task_new        | <b>AT</b> 7 |

**MIPS Implementation Note:** The system call numbers will be cleaned up some time in the future.

| snd descriptor             | a0        |                          | a0        | $\sim$       |   |        |

|----------------------------|-----------|--------------------------|-----------|--------------|---|--------|

| rcv descriptor             | a1        |                          | a1        | $\sim$       |   |        |

| timeouts                   | a2        |                          | a2        | $\sim$       |   |        |

| dest id                    | a4        | $-$ AT $0x0 \rightarrow$ | a4        | real dest id |   |        |

| waiting for id / 0         | a5        |                          | a5        | $\sim$       |   |        |

| virtual sender id / $\sim$ | a6        |                          | a6        | $\sim$       |   |        |

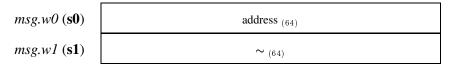

| msg.w0                     | s0        |                          | s0        | msg.w0       | / | $\sim$ |

| msg.w1                     | <b>s1</b> |                          | <b>s1</b> | msg.w1       | / | $\sim$ |

| msg.w2                     | s2        |                          | s2        | msg.w2       | / | $\sim$ |

| msg.w3                     | s3        |                          | s3        | msg.w3       | / | $\sim$ |

| msg.w4                     | s4        |                          | s4        | msg.w4       | / | $\sim$ |

| msg.w5                     | s5        |                          | s5        | msg.w5       | / | $\sim$ |

| msg.w6                     | s6        |                          | s6        | msg.w6       | / | $\sim$ |

| msg.w7                     | s7        |                          | s7        | msg.w7       | / | $\sim$ |

| $\sim$                     | v0        |                          | v0        | msgdope + cc | / | сс     |

| $\sim$                     | v1        |                          | v1        | source id    |   |        |

I

This is the basic system call for inter-process communication and synchronisation. It may be used for intra- as inter-address-space communication. All communication is synchronous and unbuffered: a message is transferred from the sender to the recipient if and only if the recipient has invoked a corresponding ipc operation. The sender blocks until this happens or a period specified by the sender elapsed without that the destination became ready to receive.

Ipc can be used to copy data as well as to *map* or *grant* fpages from the sender to the recipient. For the description of messages see section 2.3.3.

64-byte messages (plus 64-bit sender id) can be transferred solely via the registers and are thus specially optimised. If possible, short messages should therefore be reduced to 64-byte messages.

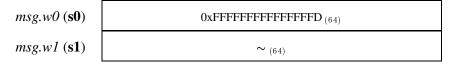

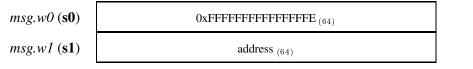

A single ipc call combines an optional send operation with an optional receive operation. Whether it includes a send and/or a receive is determined by the actual parameters. If the send or receive address is specified as *nil* (0xFFFFFFFFFFFFFFFFFF), the corresponding operation is skipped.

No time is required for the transition between send and receive phase of one ipc operation (i.e., the destination can reply with a timeout of zero).

#### **Parameters**

| snd descriptor | "nil" | 0xFFFFFFFFFFFFFFFFFFFF <sub>(64)</sub>                                                                                                         |

|----------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------|

|                |       | Ipc does not include a send operation.                                                                                                         |

|                | "mem" | *snd msg/4 $_{(62)}$ m d                                                                                                                       |

|                |       | Ipc includes sending a message to the destination specified by $d$ <i>id</i> . *snd msg must point to a valid message. The first 8 64-bit work |

dest rds of the message (*msg.w0* to *msg.w7*) are *not* taken from the message data structure but must be contained in registers s0 through s7.

# ipc

snd descriptor "reg"

Ipc includes sending a message to the destination specified by *dest id*. The message consists solely of the 8 64-bit words msg.w0 to msg.w7 in registers **s0** through **s7**.

m=0 Value-copying send operation; the dwords of the message are simply copied to the recipient.

$0_{(62)}$

- m=1 Fpage-mapping send operation. The dwords of the message to be sent are treated as 'send fpages'. The described fpages are mapped or granted (depending on the g bit in the fpage descriptor) /cbend into the recipient's address space. Mapping/granting stops when either the end of the dwords is reached or when an invalid fpage denoter is found, in particular 0. The send fpage descriptors and all potentially following words are also transferred by simple copy to the recipient. Thus a message may contain some fpages and additional value parameters. The recipient can use the received fpage descriptors to determine what has been mapped or granted into its address space, including location and access rights.

- d=0 Normal send operation. The recipient gets the true sender id.

- d=1 Deceiving send operation. A sender can specify the *virtual sender id* which the recipient should get instead of the real sender's id. The *virtual sender id* parameter contained in **a6** is only required if d=1. Recall that deceiving is secure, since only *direction-preserving deceit* is possible, see Section 1.1.3, page 12. (Note that "directionpreserving" relates to the task structure, not to threads within tasks. If a message can be sent to or from a particular thread in a task, it can also be sent to or from any other thread of the same task, and deceiving is always possible if it only changes the thread number while leaving the task ID unchanged.) If the specified *virtualsender id* does not fulfil this constraint, the send operation works like d=0.

I

rcv descriptor "nil"

Ipc does not include a receive operation.

"mem"

"reg"

\*rcv msg/4 (62)

0 0 Ipc includes receiving a message or waiting to receive a message. \*rcv msg must point to a valid message. The 8 64-bit words of the received message (msg.w0 to msg.w7) are not stored in the message

data structure but are returned in registers s0 through s7.

$0_{(62)}$

0 0

l

l

Ipc includes receiving a message or waiting to receive a message. However, only messages up to 8 64-bit words msg.w0 to msg.w7 are accepted. The received message is returned in registers s0 through s7.

| rcv descriptor | "rmap"      | rcv fpage (62) 1 o                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                |             | Ipc includes receiving a message or waiting to receive a message.<br>However, only send-fpage messages or up to 8 64-bit words $msg.w0$ to $msg.w7$ are accepted. The received message is returned in reg-<br>isters <b>s0</b> through <b>s7</b> . If a map message is received, "rcv fpage" de-<br>scribes the receive fpage (instead of "rcv fpage option" in a memory<br>message buffer). Thus fpages can also be received without a mes-<br>sage buffer in memory. |

|                | 0           | <b>MIPS Implementation Note:</b> <i>o</i> is currently not used in L4/MIPS. See <i>waiting for id</i> below.                                                                                                                                                                                                                                                                                                                                                           |

|                | <i>o</i> =0 | Only messages from the thread specified as <i>dest id</i> are accepted ("closed wait"). Any send operation from a different thread (or hardware interrupt) will be handled exactly as if the actual thread would be busy.                                                                                                                                                                                                                                              |

|                | <i>o</i> =1 | Messages from any thread will be accepted ("open wait"). If the actual thread is associated to a hardware interrupt, also messages from this hardware interrupt can arrive.                                                                                                                                                                                                                                                                                            |

| dest id        |             | Sending is directed to the specified thread, if it resides in the sender's clan. If the destination is outside the sender's clan, the message is sent to the sender's chief. If the destination is in an inner clan (a clan whose chief resides in the sender's clan), it is redirected to that chief. (See also 'id nearest' operation, page 38.)                                                                                                                     |

|                |             | This parameter is irrelevant if the ipc does not contain a send part.                                                                                                                                                                                                                                                                                                                                                                                                  |

| waiting for id    | eq 0,  eq nil | Closed receive: receiving from the specified thread (in the case of a hardware interrupt the interrupt id). This parameter is irrelevant if the ipc does not contain a receive part.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   | =0<br>=nil    | Open receive: receiving from any sender.<br>Although specifying <i>nil</i> as the destination for a send operation is illegal (error: 'destination not existent'), it can be legally specified as the source of a receive-only operation. In this case, ipc will not receive any message but will wait the specified <i>rcv timeout</i> and then terminate with error code 'receive timeout'.<br><b>MIPS Implementation Note:</b> "Open" and "closed" waits are not specified in bit zero of <i>rcv descriptor</i> as in L4/x86. This will likely change back to the way L4/x86 does it (using <i>o</i> ) in the future. |

| virtual sender id | 1             | If deceiving ( <i>snd descriptor</i> . $d = 1$ ) this is the <i>source id</i> delivered to the receiver.<br>The parameter is irrelevant if the IPC does not include a deveiving send part.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| real dest id      |               | If a message was received, this is the id of the intended recipient<br>of the message (which is different from the actual recipient if redi-<br>rection took place). The parameter is undefined if no message was<br>received.                                                                                                                                                                                                                                                                                                                                                                                           |

| source id         |               | If a message was received this is the id of its sender (or the <i>virtual sender id</i> if the message received used a deceiving send operation). If a hardware interrupt was received this is the interrupt id. The parameter is undefined if no message was received.                                                                                                                                                                                                                                                                                                                                                  |

| msg.w0 w7         | "snd"         | First 8 64-bit words of message to be sent. These message words are taken directly from registers <b>s0</b> through <b>s7</b> . <i>They are not read from the message data structure.</i>                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                   | "rcv"         | First 8 64-bit words of received message, undefined if no message was received. <i>These message words are available only in registers</i> $s0$ through $s7$ . The $\mu$ -kernel does not store it in the receive message buffer. The user program may store it or use it directly in the registers.                                                                                                                                                                                                                                                                                                                     |

| msg.dope + cc     |               | 0 (32) mwords (19) strings (5) CC (8)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                   |               | Message dope describing received message. If no message was received, only $cc$ is delivered. The dope word of the received message is available only in register $v0$ . The $\mu$ -kernel does not store it in the receive message buffer. The user program may store it or use it directly in the register. (Note that the lowermost 8 bits of msg dope and size dope in the message data structure are undefined. So it is legal to store $v0$ in the msg-dope field, even if $cc \neq 0$ .)                                                                                                                          |

| $ec_{(4)}$ | i | r | m | d |  |

|------------|---|---|---|---|--|

|            |   |   |   |   |  |

- *d*=0 The received message is transferred directly ("undeceived") from *source id.*

- d=1 The received message is "deceived" by a chief. *source id* is the virtual source id which was specified by the sending chief.

- m=0 The received message did not contain fpages.

- m=1 The sender mapped or granted fpages. The sender's fpage descriptors were also (besides mapping/granting) transferred as mwords.

- r=0 The received message was directed to the actual recipient, not redirected to a chief. I.e. sender and receiver a part of the same clan. The *i*-bit has no meaning in this case and is zero.

- r=1 The received message was redirected to the chief which was next on the path to the true destination. Sender and addressed recipient belong to different clans.

- i=0 If r=1: the received message comes from outside the own clan.

- i=1 If r=1: the received message comes from an inner clan.

- = 0 ok: the optional send operation was successful, and if a receive operation was also specified (*rcv descriptor*  $\neq nil$ ) a message was also received correctly.

- $\neq 0$  If ipc fails the completion code is in the range 0x10...0xF0. If the send operation fails, ipc is terminated without attemtping any receive operation. *s* specifies whether the error occurred during the receive (*s* = 0) operation or during the send (*s* = 1) operation:

- 1 *Non-existing* destination or source.

- 2+s Timeout.

- 4 + s Cancelled by another thread (system call lthread\_ex\_regs).

- 6 + s Map failed due to a shortage of page tables.

- 8 + s Send pagefault timeout.

- A + s Receive pagefault timeout.

- C + s Aborted by another thread (system call lthread\_ex\_regs or task\_new).

- E + s Cut message. Potential reasons are (a) the recipient's moord buffer is too small; (b) the recipient does not accept enough strings; (c) at least one of the recipient's string buffers is too small.

- 1...5 The respective operation was terminated before a real message transfer started. No partner was directly involved.

- 6...F The respective operation was terminated while a message transfer was running. The message transfer was aborted. The current partner (sender or receiver) was involved and received the corresponding error code. It is not defined which parts of the message are already transferred and which parts are not yet transferred. The source id returned to the receiver is also undefined.

СС

ес

timeouts

This 32-bit word specifies all 4 timeouts, the quadruple (*snd, rcv, snd pf, rcv pf*). For A detailed description see section 2.3.4. Frequently used values are

|            | snd      | rcv      | snd pf   | rcv pf   |

|------------|----------|----------|----------|----------|

| 0x00000000 | $\infty$ | $\infty$ | $\infty$ | 8        |

| 0x00000001 | 0        | $\infty$ | $\infty$ | $\infty$ |

| 0x0000011  | 0        | 0        | $\infty$ | $\infty$ |

- "snd" If the required send operation cannot start transfer data within the specified time, ipc is terminated and fails with completion code 'send timeout' (0x18). If ipc does not include a send operation, this parameter is meaningless.

- "rcv" If ipc includes a receive operation and no message transfer starts within the specified time, ipc is terminated and fails with completion code 'receive timeout' (0x20). If ipc does not include a receive operation, this parameter is meaningless.

- *"spf"* If during sending data a pagefault *in the receiver's address space* occurs, *snd pf* specified by the sender is used as send and receive timeout for the pagefault RPC.

- *"rpf"* If during receiving data a pagefault *in the sender's address space* occurs, *rcv pf* specified by the receiver is used as send and receive timeout for the pagefault RPC.

### **Basic Ipc Types**

CALL

L

L

|                    |           | I                               | 1  |              |

|--------------------|-----------|---------------------------------|----|--------------|

| *snd msg / 0       | a0        |                                 | a0 | $\sim$       |

| *rcv msg / 0       | a1        |                                 | a1 | $\sim$       |

| timeouts           | a2        |                                 | a2 | $\sim$       |

| dest id            | a4        | $- \text{AT} 0 x 0 \rightarrow$ | a4 | real dest id |

| dest id            | a5        |                                 | a5 | $\sim$       |

| virt sndr / $\sim$ | a6        |                                 | a6 | $\sim$       |

| msg.w0             | <b>s0</b> |                                 | s0 | msg.w0       |

| msg.w1             | <b>s1</b> |                                 | s1 | msg.w1       |

| msg.w2             | s2        |                                 | s2 | msg.w2       |

| msg.w3             | s3        |                                 | s3 | msg.w3       |

| msg.w4             | s4        |                                 | s4 | msg.w4       |

| msg.w5             | s5        |                                 | s5 | msg.w5       |

| msg.w6             | s6        |                                 | s6 | msg.w6       |

| msg.w7             | s7        |                                 | s7 | msg.w7       |

| $\sim$             | v0        |                                 | v0 | msgdope + cc |

| $\sim$             | v1        |                                 | v1 | dest id      |

|                    |           |                                 |    |              |

This is the usual blocking RPC. *snd msg* is sent to *dest id* and the invoker waits for a reply from *dest id*. Messages from other sources are not accepted. Note that since the send/receive transition needs no time, the destination can reply with *snd timeout* = 0.

This operation can also be used for a server with one dedicated client. It sends the reply to the

client and waits for the client's next order.

| T. | REPLY & WAIT |                    |    |                        |    |              |

|----|--------------|--------------------|----|------------------------|----|--------------|

|    |              | *snd msg / 0       | a0 |                        | a0 | $\sim$       |

|    |              | *rcv msg / 0       | a1 |                        | a1 | $\sim$       |

|    |              | timeouts           | a2 |                        | a2 | $\sim$       |

|    |              | dest id            | a4 | $- AT 0x0 \rightarrow$ | a4 | real dest id |

|    |              | 0                  | a5 |                        | a5 | $\sim$       |

|    |              | virt sndr / $\sim$ | a6 |                        | a6 | $\sim$       |

|    |              | msg.w0             | s0 |                        | s0 | msg.w0       |

|    |              | msg.w1             | s1 |                        | s1 | msg.wl       |

|    |              | msg.w2             | s2 |                        | s2 | msg.w2       |

|    |              | msg.w3             | s3 |                        | s3 | msg.w3       |

|    |              | msg.w4             | s4 |                        | s4 | msg.w4       |

|    |              | msg.w5             | s5 |                        | s5 | msg.w5       |

|    |              | msg.w6             | s6 |                        | s6 | msg.w6       |

|    |              | msg.w7             | s7 |                        | s7 | msg.w7       |

|    |              | $\sim$             | v0 |                        | v0 | msgdope + cc |

|    |              | $\sim$             | v1 |                        | v1 | source id    |

*snd msg* is sent to *dest id* and the invoker waits for a reply from any source. This is the standard server operation: it sends a reply to the actual client and waits for the next order which may come from a different client.

| SEND |                                        |           |                        |    |              |

|------|----------------------------------------|-----------|------------------------|----|--------------|

|      | *snd msg / 0                           | a0        |                        | a0 | $\sim$       |

|      | 0xFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFF | a1        |                        | a1 | $\sim$       |

|      | timeouts                               | a2        |                        | a2 | $\sim$       |

|      | dest id                                | a4        | $- AT 0x0 \rightarrow$ | a4 | $\sim$       |

|      | ~                                      | a5        |                        | a5 | $\sim$       |

|      | virt sndr / $\sim$                     | a6        |                        | a6 | $\sim$       |

|      | msg.w0                                 | <b>s0</b> |                        | s0 | $\sim$       |