# Principled Elimination of Microarchitectural Timing Channels through Operating-System Enforced Time Protection

# Qian Ge

Submitted in fulfillment of the requirements for the degree of Doctor of Philosophy

School of Computer Science and Engineering

University of New South Wales

Sydney, Australia

October 2019

# Thesis/Dissertation Sheet

Surname/Family Name

Given Name/s

Faculty

School

Thesis Title

Abbreviation for degree as give in the University calendar

Engineering

Computer Science and Engineering

**Principled Elimination of Microarchitectural Timing Channels through**

Operating-System Enforced Time Protection

### Abstract 350 words maximum: (PLEASE TYPE)

Ge

Qian

PhD

Microarchitectural timing channels exploit resource contentions on a shared hardware platform to cause information leakage through timing variance. These channels threaten system security by providing unauthorised information flow in violation of the system's security policy. Present operating systems lack the means for systematic prevention of such channels. To address this problem, we propose time protection as an operating system (OS) abstraction, which provides mandatory temporal isolation analogous to the spatial isolation provided by the established memory protection abstraction.

In order to fully understand microarchitectural timing channels, we first study all published microarchitectural timing attacks, their countermeasures and analyse the underlying causes. Then we define two application scenarios, a confinement scenario and a cloud scenario, which between them represent a large class of security-critical use cases, and aim to develop a solution that supports both.

Our study identifies competition for limited hardware resources as the underlying cause for microarchitectural timing channels. From this we derive the requirement that proper isolation requires that all shared resources must be partitioned, either spatially or temporally (time-shared). We then analyse a number of recent processors across two instruction-set architectures (ISAs), x86 and Arm, for their support for such partitioning. We discover that all examined processors exhibit hardware state that cannot be partitioned by architected means, meaning that they all have uncloseable channels. We define the requirements hardware must satisfy for timing-channel prevention, and propose an augmented ISA as a new, security-oriented hardware-software contract.

Assuming conforming hardware, we then define the requirements that OS-provided time protection must satisfy. We propose a concrete design of time protection, consisting of a set of policy-free mechanisms, and present an implementation in the seL4 microkernel. We evaluate the efficacy and efficiency of the implementation, and show that it is highly effective at closing timing channels, to the degree supported by the underlying hardware. We also find that the performance overheads are small to negligible. We can conclude that principled prevention of timing channels is possible though mandatory, black-box enforcement by the OS, subject to hardware manufacturers providing mechanisms for scrubbing all shared microarchitectural state.

| Declaration relating to disposition of project thesis/dissertat                                                                                                                             | ion                                              |                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--------------------------------------------------|

| I hereby grant to the University of New South Wales or its a in the University libraries in all forms of media, now or here such as patent rights. I also retain the right to use in future | after known, subject to the provisions of the C  | opyright Act 1968. I retain all property rights, |

| I also authorise University Microfilms to use the 350 word a theses only).                                                                                                                  | bstract of my thesis in Dissertation Abstracts I | nternational (this is applicable to doctoral     |

| Signature                                                                                                                                                                                   | Witness Signature                                | Date                                             |

The University recognises that there may be exceptional circumstances requiring restrictions on copying or conditions on use. Requests for restriction for a period of up to 2 years must be made in writing. Requests for a longer period of restriction may be considered in exceptional circumstances and require the approval of the Dean of Graduate Research.

FOR OFFICE USE

Date of completion of requirements for Award:

### **ORIGINALITY STATEMENT**

'I hereby declare that this submission is my own work and to the best of my knowledge it contains no materials previously published or written by another person, or substantial proportions of material which have been accepted for the award of any other degree or diploma at UNSW or any other educational institution, except where due acknowledgement is made in the thesis. Any contribution made to the research by others, with whom I have worked at UNSW or elsewhere, is explicitly acknowledged in the thesis. I also declare that the intellectual content of this thesis is the product of my own work, except to the extent that assistance from others in the project's design and conception or in style, presentation and linguistic expression is acknowledged.'

| Signed |  |

|--------|--|

| Date   |  |

### **COPYRIGHT STATEMENT**

'I hereby grant the University of New South Wales or its agents the right to archive and to make available my thesis or dissertation in whole or part in the University libraries in all forms of media, now or here after known, subject to the provisions of the Copyright Act 1968. I retain all proprietary rights, such as patent rights. I also retain the right to use in future works (such as articles or books) all or part of this thesis or dissertation.

I also authorise University Microfilms to use the 350 word abstract of my thesis in Dissertation Abstract International (this is applicable to doctoral theses only). I have either used no substantial portions of copyright material in my thesis or I have obtained permission to use copyright material; where permission has not been granted I have applied/will apply for a partial restriction of the digital copy of my thesis or dissertation.'

| Signed                |                                                                                                                                                                                                                                               |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Date                  |                                                                                                                                                                                                                                               |

| AUTHE                 | NTICITY STATEMENT                                                                                                                                                                                                                             |

| officially and if the | that the Library deposit digital copy is a direct equivalent of the final approved version of my thesis. No emendation of content has occurred here are any minor variations in formatting, they are the result of the on to digital format.' |

| Signed                |                                                                                                                                                                                                                                               |

| Date                  |                                                                                                                                                                                                                                               |

# INCLUSION OF PUBLICATIONS STATEMENT

| UNSW is supportive of as detailed in the UNSV                                                                                                                  | candidates publishing their rese<br>V Thesis Examination Procedure                                          | arch results during their candidature                                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>"primary author", ie. to preparation of the wo</li> <li>The student has appropriate their supervisor and F</li> <li>The publication is not</li> </ul> | oval to include the publication in                                                                          | Chapter if: tent in the publication and is the narily for the planning, execution and their thesis in lieu of a Chapter from ntractual agreements with a third |

| Please indicate whether                                                                                                                                        | this thesis contains published m                                                                            | aterial or not                                                                                                                                                 |

| This thesis co                                                                                                                                                 |                                                                                                             | la Parl                                                                                                                                                        |

| Some of the vi                                                                                                                                                 | vork described in this thesis has<br>In the relevant Chapters with ack<br>may delete all the material on pa | been published and it has been                                                                                                                                 |

| This thesis has                                                                                                                                                | s publications (either published on<br>to it in lieu of a chapter and the                                   |                                                                                                                                                                |

| micro i nave useu a                                                                                                                                            | the Thesis Examination Proced<br>publication in lieu of a Chapter,<br>quirements to be included in the      | the listed publication(s) thesis.                                                                                                                              |

| QIAN GE                                                                                                                                                        | Signature                                                                                                   | Date (dd/mm/yy)                                                                                                                                                |

| Postgraduate Coordinate                                                                                                                                        |                                                                                                             |                                                                                                                                                                |

| <ul> <li>the information below</li> <li>where listed publication</li> <li>with the Thesis Exam</li> <li>the minimum requiren</li> </ul>                        | on(s) have been used in liquids                                                                             | Chapter(s), their use complies                                                                                                                                 |

| PGC's Name                                                                                                                                                     | PGC's Signature                                                                                             | Date (dd/mm/yy)                                                                                                                                                |

|                                                                                                                                                                |                                                                                                             |                                                                                                                                                                |

### **Abstract**

Microarchitectural timing channels exploit resource contentions on a shared hardware platform to cause information leakage through timing variance. These channels threaten system security by providing unauthorised information flow in violation of the system's security policy. Present operating systems lack the means for systematic prevention of such channels. To address this problem, we propose *time protection* as an operating system (OS) abstraction, which provides mandatory temporal isolation analogous to the spatial isolation provided by the established memory protection abstraction.

In order to fully understand microarchitectural timing channels, we first study all published microarchitectural timing attacks, their countermeasures and analyse the underlying causes. Then we define two application scenarios, a confinement scenario and a cloud scenario, which between them represent a large class of security-critical use cases, and aim to develop a solution that supports both.

Our study identifies competition for limited hardware resources as the underlying cause for microarchitectural timing channels. From this we derive the requirement that proper isolation requires that all shared resources must be partitioned, either spatially or temporally (time-shared). We then analyse a number of recent processors across two instruction-set architectures (ISAs), x86 and Arm, for their support for such partitioning. We discover that all examined processors exhibit hardware state that cannot be partitioned by architected means, meaning that they all have uncloseable channels. We define the requirements hardware must satisfy for timing-channel prevention, and propose an *augmented ISA* as a new, security-oriented hardware-software contract.

Assuming conforming hardware, we then define the requirements that OS-provided time protection must satisfy. We propose a concrete design of time protection, consisting of a set of policy-free mechanisms, and present an implementation in the seL4 microkernel. We evaluate the efficacy and efficiency of the implementation, and show that it is highly effective at closing timing channels, to the degree supported by the underlying hardware. We also find that the performance overheads are small to negligible. We can conclude that principled prevention of timing channels is possible though mandatory, black-box enforcement by the OS, subject to hardware manufacturers providing mechanisms for scrubbing all shared microarchitectural state.

# **Contents**

| Al | bstrac            | et                       |                                                                                                                                                                                                | viii                                 |

|----|-------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| C  | onten             | ts                       |                                                                                                                                                                                                | ix                                   |

| A  | cknov             | ledgen                   | nents                                                                                                                                                                                          | xiii                                 |

| Ρι | ıblica            | tions                    |                                                                                                                                                                                                | XV                                   |

| A  | crony             | ms                       |                                                                                                                                                                                                | xvii                                 |

| Li | st of l           | Figures                  |                                                                                                                                                                                                | xxi                                  |

| Li | st of '           | <b>Fables</b>            |                                                                                                                                                                                                | XXV                                  |

| 1  | 1.1<br>1.2<br>1.3 | Resear                   | architectural Timing Channels                                                                                                                                                                  | 2<br>5<br>5                          |

| 2  |                   | kgroun                   |                                                                                                                                                                                                | 7                                    |

|    | 2.1<br>2.2<br>2.3 | Virtua                   | g Channels I-to-physical Address Translation ant Microarchitectural Components Caches Prefetching Pipelining In-flight data Buses and interconnects Hardware multithreading and multicore DRAM | 8<br>9<br>10<br>14<br>14<br>15<br>16 |

|    | 2.4<br>2.5<br>2.6 | 2.3.8<br>Cache<br>The La | GPU                                                                                                                                                                                            | 18<br>19<br>22<br>23<br>23<br>24     |

| 3 | Rela            | ated Wo  | ork 29                                                              |

|---|-----------------|----------|---------------------------------------------------------------------|

|   | 3.1             | Scope    | 29                                                                  |

|   |                 | 3.1.1    | Hardware multithreading                                             |

|   |                 | 3.1.2    | Timing channels due to self-contention                              |

|   |                 | 3.1.3    | Buses and interconnects                                             |

|   |                 | 3.1.4    | DRAM attacks                                                        |

|   |                 | 3.1.5    | DoS attacks                                                         |

|   | 3.2             | Timin    | g Attacks                                                           |

|   |                 | 3.2.1    | Attacking techniques                                                |

|   |                 | 3.2.2    | Timing attacks on core-shared state                                 |

|   |                 | 3.2.3    | Timing attacks on package-shared state                              |

|   |                 |          | 3.2.3.1 Time slicing                                                |

|   |                 |          | 3.2.3.2 Multicore                                                   |

|   |                 | 3.2.4    | Summary                                                             |

|   | 3.3             |          | ermeasures                                                          |

|   | 0.0             | 3.3.1    | Constant-time techniques                                            |

|   |                 | 3.3.2    | Injecting noise                                                     |

|   |                 | 3.3.3    | Enforcing determinism                                               |

|   |                 | 3.3.4    | Partitioning time                                                   |

|   |                 | 3.3.5    | Partitioning hardware                                               |

|   |                 | 3.3.6    | Summary                                                             |

|   | 3.4             |          | kernel                                                              |

|   | 3.5             |          | ernel                                                               |

|   | 3.3             | LAUKC    | inci                                                                |

| 4 | Thr             | eat Scei | narios and the Targeted System Solution 5'                          |

|   | 4.1             | Threat   | t Scenarios                                                         |

|   |                 | 4.1.1    | Confinement                                                         |

|   |                 | 4.1.2    | Cloud                                                               |

|   | 4.2             | Hardw    | vare Requirements                                                   |

|   |                 | 4.2.1    | Resetting on-core state                                             |

|   |                 | 4.2.2    | Partitioning                                                        |

|   | 4.3             | The Sy   | ystem Solution – Providing Time Protection in the OS 62             |

|   |                 |          |                                                                     |

| 5 |                 | _        | Microarchitectural Timing Channels by Resetting Hardware            |

|   | <b>Stat</b> 5.1 |          | 69<br>Ating Intra-core Timing Channels with Resetting Operations 60 |

|   | 5.2             | _        |                                                                     |

|   |                 |          | 1                                                                   |

|   | 5.3             |          | 27                                                                  |

|   |                 | 5.3.1    |                                                                     |

|   |                 |          |                                                                     |

|   |                 |          | 5.3.1.2 L1-I cache                                                  |

|   |                 |          | 5.3.1.3 TLB                                                         |

|   |                 |          | 5.3.1.4 BTB                                                         |

|   |                 |          | 5.3.1.5 BHB                                                         |

|   |                 |          | 5.3.1.6 Summary                                                     |

|   |                 | 5.3.2    | Mitigations                                                         |

|   |                 |          | 5.3.2.1 Architectural support on x86                                |

|   |                 |          | 5.3.2.2 Architectural support on Arm                                |

|   |                 | 5.3.3    | Evaluating Channels                                                 |

|   |     |         | 5.3.3.1    | The channel matrix                                                               | . 75  |

|---|-----|---------|------------|----------------------------------------------------------------------------------|-------|

|   |     |         | 5.3.3.2    | Channel leakage                                                                  | . 76  |

|   |     |         | 5.3.3.3    | Analysing timing channels                                                        | . 77  |

|   | 5.4 | Result  | s          |                                                                                  | . 79  |

|   |     | 5.4.1   | Evaluati   | on platforms                                                                     | . 79  |

|   |     | 5.4.2   | Overvie    | w of results                                                                     | . 79  |

|   |     | 5.4.3   | The effe   | ctiveness of hardware resetting operations                                       | . 81  |

|   |     |         | 5.4.3.1    | L1-D cache                                                                       | . 81  |

|   |     |         | 5.4.3.2    | L1-I cache                                                                       | . 81  |

|   |     |         | 5.4.3.3    | TLB                                                                              | . 82  |

|   |     |         | 5.4.3.4    | BTB                                                                              | . 82  |

|   |     |         | 5.4.3.5    | ВНВ                                                                              | . 83  |

|   |     |         | 5.4.3.6    | Summary                                                                          | . 84  |

|   | 5.5 | Securi  | ty Needs a | a New Hardware-Software Contract                                                 | . 85  |

|   |     | 5.5.1   | The Aug    | gmented ISA: A New Hardware-Software Contract                                    | . 85  |

|   |     | 5.5.2   | Discussi   | on                                                                               | . 87  |

|   |     |         | 5.5.2.1    | Implications                                                                     | . 87  |

|   |     |         | 5.5.2.2    | Cost                                                                             | . 88  |

| , | T:  | a Duada | ation Mad  | havious and Their Innlamentation in set 4                                        | 105   |

| 6 | 6.1 |         |            | chanisms and Their Implementation in seL4 or Providing Time Protection in the OS |       |

|   | 6.2 |         |            | OS: Cloning the Kernel                                                           |       |

|   | 6.3 |         | _          | rrupts                                                                           |       |

|   | 6.4 |         | _          | in seL4                                                                          |       |

|   | 0.4 | 6.4.1   |            | lone overview                                                                    |       |

|   |     | 0.4.1   | 6.4.1.1    | Representing a kernel image                                                      |       |

|   |     |         | 6.4.1.2    | Representing memory used by a kernel image                                       |       |

|   |     |         | 6.4.1.3    | Creating a partitioned system                                                    |       |

|   |     | 6.4.2   |            | cess of cloning a kernel image                                                   |       |

|   |     | 6.4.3   |            | ng a cloned kernel image                                                         |       |

|   |     | 6.4.4   |            | the shared global data section                                                   |       |

|   |     | 6.4.5   |            | ing interrupts                                                                   |       |

|   |     | 6.4.6   |            | -switch actions                                                                  |       |

|   |     | 0.4.0   | 6.4.6.1    | Switching kernel window mapping                                                  |       |

|   |     |         | 6.4.6.2    | Flushing on-core state                                                           |       |

|   |     |         | 6.4.6.3    | Flushing deterministically                                                       |       |

|   |     |         | 6.4.6.4    | Deterministic data sharing                                                       |       |

|   |     |         | 6.4.6.5    | Switching interrupts                                                             |       |

|   |     |         | 6.4.6.6    |                                                                                  |       |

|   |     | 6.4.7   |            | Summary                                                                          |       |

|   | 6.5 |         |            |                                                                                  |       |

|   | 0.5 | 6.5.1   |            | re platforms                                                                     |       |

|   |     | 6.5.2   |            | •                                                                                |       |

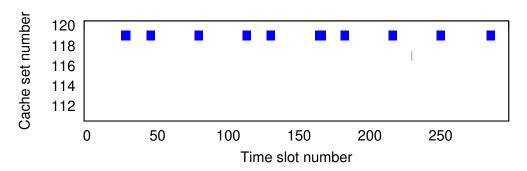

|   |     | 0.3.2   | 6.5.2.1    | Covert timing channels on each or cache like company                             |       |

|   |     |         |            | Covert timing channels on cache or cache-like compone                            |       |

|   |     |         | 6.5.2.2    | Covert timing channel on domain switching latency.                               |       |

|   |     |         | 6.5.2.3    | Covert timing channel on a shared kernel image                                   |       |

|   |     |         | 6.5.2.4    | Covert timing channel on a shared Interrupt                                      |       |

|   |     | 652     | 6.5.2.5    | Cross-core LLC side channel                                                      |       |

|   |     | 6.5.3   | remorm     | ance                                                                             | . 151 |

|    |        |         | 6.5.3.1    | IPC microbenchmark                  | 151 |

|----|--------|---------|------------|-------------------------------------|-----|

|    |        |         | 6.5.3.2    | Domain switching cost               | 152 |

|    |        |         | 6.5.3.3    | Kernel cloning and destruction cost | 153 |

|    |        |         | 6.5.3.4    | The cost of cache colouring         | 155 |

|    |        |         | 6.5.3.5    | The impact of domain switches       | 157 |

|    |        | 6.5.4   | Summary    | y                                   | 159 |

| 7  | Con    | clusion |            |                                     | 161 |

|    | 7.1    | Contril | butions .  |                                     | 161 |

|    | 7.2    | Streng  | th and Lin | nitations                           | 162 |

|    | 7.3    | Discus  | sion and F | Suture Work                         | 163 |

| Bi | bliogr | aphy    |            |                                     | 165 |

## Acknowledgements

I would like to thank my supervisor, Gernot Heiser, for his support, guidance, and patience during my PhD. My PhD topic, principled elimination of microarchitectural timing channels through operating-system enforced time protection, is extremely challenging, and this work would not be possible without his extremely high standard and wise insight. Being his student was very challenging, but also rewarding.

Thanks to my partner, Adrian Danis, who gave me tremendous encouragement during those very dark days while I was struggling with both work and life. Thanks also to my families, Lihua Zhang, Xingjie Ge, Jiale Li, Lijuan Zhang, and Lili Zhang, for their great support and understanding.

Thanks to past and current students, engineers and researchers in the Trustworthy Systems team, who have helped me: Peter Chubb, Anna Lyons, Luke Mondy, and Yuval Yarom.

Special thanks to my friends: Cai Li, and Lei Zeng, for being there at the moment I needed it the most.

Particularly, I would like to thank those who helped with proof reading my thesis draft: Peter Chubb, Anna Lyons, Branden Robinson, Victor Phan, Sylvain Gauthier, Oliver Scott, Damon Lee, Amos Robinson, Santiago Bautista, Joel Beeren, Alex Legg and my supervisor, Gernot Heiser.

Bow to all of you, as the most formal way to show my respect.

# **Publications**

This thesis is partially based on work described in the following publications: <sup>1</sup>

Qian Ge, Yuval Yarom, Tom Chothia, and Gernot Heiser. Time protection: the missing OS abstraction. In *EuroSys Conference*, Dresden, Germany, March 2019. ACM. Best Paper Award.

Citation count: 9.

- Qian Ge, Yuval Yarom, and Gernot Heiser. No security without time protection: We need a new hardware-software contract. In *Asia-Pacific Workshop on Systems* (*APSys*), Korea, August 2018b. ACM SIGOPS. **Best Paper Award**. Citation count: 9.

- Qian Ge, Yuval Yarom, David Cock, and Gernot Heiser. A survey of microarchitectural timing attacks and countermeasures on contemporary hardware. *Journal of Cryptographic Engineering*, 8:1–27, April 2018a.

Citation count: 135.

Other papers published during my PhD:

- Fangfei Liu, Qian Ge, Yuval Yarom, Frank Mckeen, Carlos Rozas, Gernot Heiser, and Ruby B Lee. CATalyst: Defeating last-level cache side channel attacks in cloud computing. In *IEEE Symposium on High-Performance Computer Architecture*, pages 406–418, Barcelona, Spain, March 2016. IEEE.

Citation count: 145.

- Fangfei Liu, Yuval Yarom, Qian Ge, Gernot Heiser, and Ruby B Lee. Last-level cache side-channel attacks are practical. In *IEEE Symposium on Security and Privacy*, pages 605–622, San Jose, CA, US, May 2015. IEEE. Citation count: 455.

- David Cock, Qian Ge, Toby Murray, and Gernot Heiser. The last mile: An empirical study of some timing channels on seL4. In *ACM Conference on Computer and Communications Security*, pages 570–581, Scottsdale, AZ, USA, November 2014. ACM.

Citation count: 65.

<sup>&</sup>lt;sup>1</sup>The citation counts are based on statistics offered by Google scholar on September 2019.

# Acronyms

AES avanced encryption standard. 30, 40-45, 51

aISA augmented ISA. 83-85, 103, 104

ALU arithmetic logic unit. 18

APIC advanced programmable interrupt controller. 120

**ASID** address space ID. 8, 9, 13, 24, 25, 110, 112–114, 123, 124

**ASLR** address space layout randomization. 31, 39–42

**BHB** branch history buffer. 13, 17, 20, 37, 39, 43, 56, 59, 64, 65, 68, 69, 78, 81–83, 104, 117, 125, 128, 133

**BPU** branch prediction unit. 48, 117

**BTB** branch target buffer. 13, 17, 20, 29, 37, 40, 43, 56, 59, 64, 67–69, 76, 78, 80, 82, 83, 104, 117, 125, 128, 132

CAT cache allocation technology. 50, 161, 162

**CPU** central processing unit. 1, 2, 10, 13–18, 21–23, 30, 37–40, 43, 46–48, 50, 65, 69, 72, 81, 120, 155, 159, 162

**DES** data encryption standard. 51

**DoS** denial-of-service. 31, 34, 56

**DRAM** dynamic random-access memory. 10, 17, 18, 29, 32–34, 56

ECC error-correcting code. 18, 32, 34

ECDSA elliptic curve digital signature algorithm. 29, 42

**FIFO** first in, first out. 117

**FPU** floating point unit. 17, 37, 43

**GPU** graphics processing unit. 10, 18, 33

HTTP HyperText Transfer Protocol. 54

IaaS infrastructure-as-a-service. 1

- **IBC** indirect branch control. 5, 49, 71, 78–83, 117, 161

- **IBS** instruction-based scheduling. 46, 47

- **IPC** inter-process communication. 22–25, 27, 108, 110, 149, 150

- **IPI** inter-processor interrupt. 41, 123

- IRQ interrupt request. 25, 107, 112, 114, 148

- **ISA** instruction-set architecture. 4, 5, 8–10, 63, 64, 83, 85, 103, 157, 160

- **L1** first-level. 11–14, 17, 18, 20, 43, 49–51, 53, 56, 58, 59, 72, 85, 86, 103, 104, 117, 125–127, 139, 150, 153

- **L1-D** first-level data. 10, 11, 15, 16, 29, 36–38, 40, 49, 51, 64–67, 69, 72, 78–80, 82, 85, 86, 105, 117, 127–129, 134, 150, 151

- **L1-I** first-level instruction. 10, 11, 29, 37, 41, 51, 64, 66, 67, 69, 72–74, 79, 80, 82, 83, 85, 117, 127, 128, 131, 133, 150, 151

- **L2** second-level. 10, 11, 13, 14, 17, 18, 43, 46, 60, 72, 104, 126, 128, 129, 134, 138, 145, 149–155, 157, 161

- **L3** third-level. 10, 11, 13, 17, 21, 36, 126, 150, 151, 153

- **LLC** last-level cache. 10, 16, 20, 21, 31, 34–36, 41–43, 50, 51, 53, 56, 59, 60, 83–86, 104, 126, 127, 142, 148, 161

- LRU least-recently used. 78, 117

- MBA memory bandwidth allocation. 32

- MI mutual information. 63, 74–82, 128, 130–132, 136–139, 144–146, 148

- MLS multi-level secure. 61

- MMU memory management unit. 8, 13, 31, 38

- MSR machine state register. 71

- **NUMA** non-uniform memory access. 106

- **OS** operating system. 1–4, 8, 9, 19–21, 30, 37–39, 42, 48, 49, 53–61, 63, 65, 77, 78, 83–85, 103, 104, 120, 153, 158–162

- PaaS platform-as-a-service. 42

- PARA probabilistic adjacent row activation. 33, 34

- **PIPT** physically-indexed, physically-tagged. 12, 13, 33

- **PIVT** physically-indexed, virtually-tagged. 12

- **PMU** performance monitoring unit. 47

**POSIX** portable operating system interface. 153

**QoS** quality of service. 34, 50, 56

RIDL rogue in-flight data load. 39

**RPcache** random permutation cache. 45, 46

**RSA** Rivest-Shamir-Adleman. 31, 32, 34, 40–42

**RSB** return stack buffer. 40, 43

**SGX** software guard extensions. 38, 39

**SMM** system management mode. 38

SMT simultaneous multithreading. 16, 17, 56

**SoC** system on a chip. 33

**SP** stream processor. 18

**SVG** scalable vector graphics. 30

**TCB** thread control block. 24, 25, 105, 107, 108, 110, 112, 116, 142

TIFF tagged image file format. 154

**TLB** translation look-aside buffer. 2, 13, 17, 20, 21, 29, 30, 37, 40, 42, 43, 48, 51, 53, 56, 59, 64, 67, 69, 71, 72, 76, 80, 82, 85, 103, 104, 117, 123, 128, 131, 132, 150, 155, 157

**TP** texture processor. 18

**TPR** task priority register. 120

**TSX** transactional synchronization extension. 31, 36, 42, 43

**VIPT** virtually-indexed, physically-tagged. 12

VIVT virtually-indexed, virtually-tagged. 12, 13

VM virtual machine. 1, 38, 39, 41–43, 45, 46, 49, 50, 52, 55, 57, 58, 86, 104, 148, 159

VMM virtual machine monitor. 1, 38, 85

# **List of Figures**

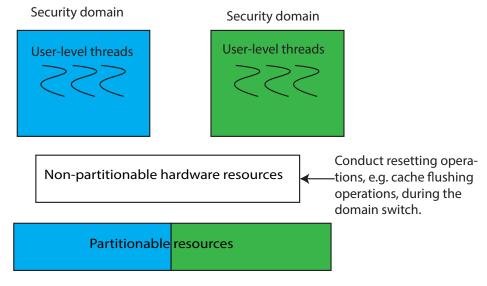

| 1.1  | An overview of the system solution for mitigating microarchitecture timing channels                                                                                                                                                                                                                                         | 3  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

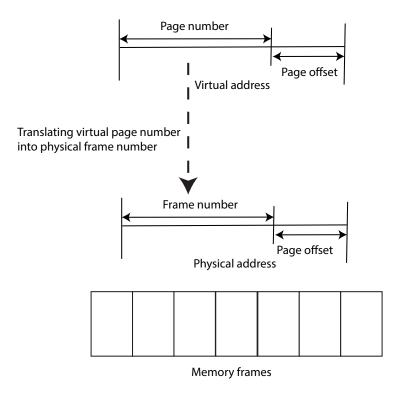

| 2.1  | The virtual-to-physical address translation                                                                                                                                                                                                                                                                                 | 9  |

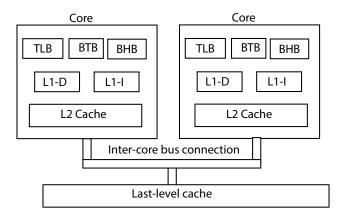

| 2.2  | The hierarchical cache structure on a multicore Intel processor                                                                                                                                                                                                                                                             | 11 |

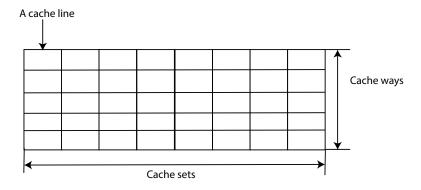

| 2.3  | The internal structure of a hardware cache                                                                                                                                                                                                                                                                                  | 11 |

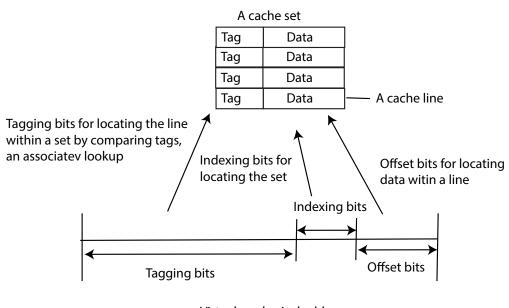

| 2.4  | The indexing scheme of a hardware cache                                                                                                                                                                                                                                                                                     | 12 |

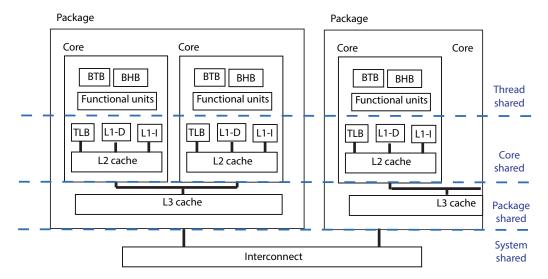

| 2.5  | The shared resources in a multi-core Intel system                                                                                                                                                                                                                                                                           | 17 |

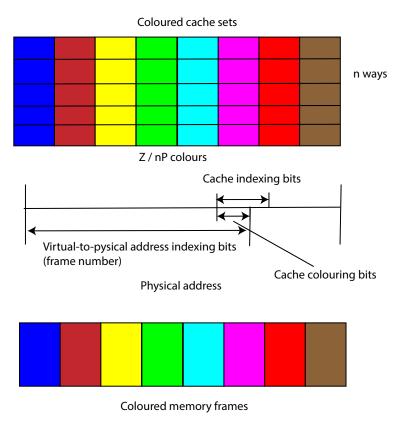

| 2.6  | The cache colouring mechanism                                                                                                                                                                                                                                                                                               | 19 |

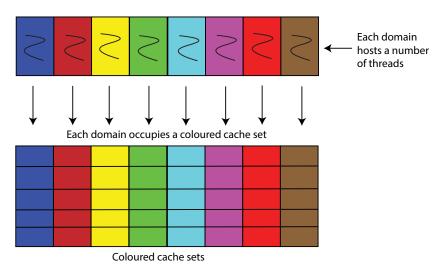

| 2.7  | Assigning security domains with different cache colours                                                                                                                                                                                                                                                                     | 21 |

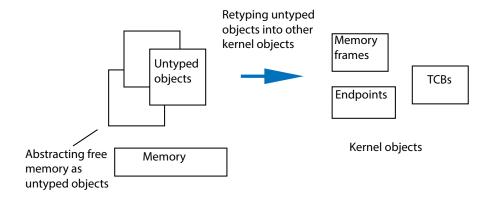

| 2.8  | The memory model in seL4                                                                                                                                                                                                                                                                                                    | 24 |

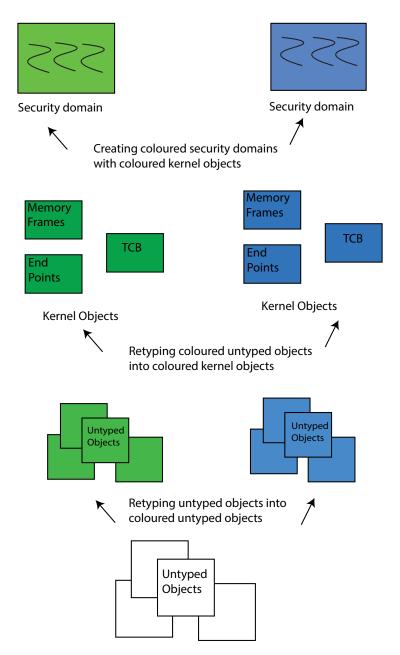

| 2.9  | Creating coloured security domains using the memory model in seL4                                                                                                                                                                                                                                                           | 27 |

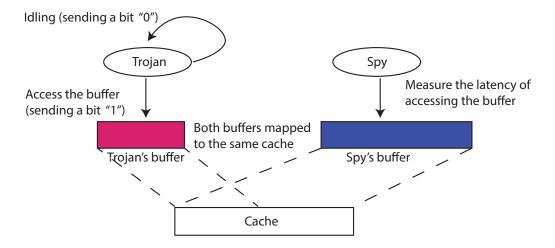

| 3.1  | A covert cache-based timing channel using the PRIME+PROBE technique                                                                                                                                                                                                                                                         | 36 |

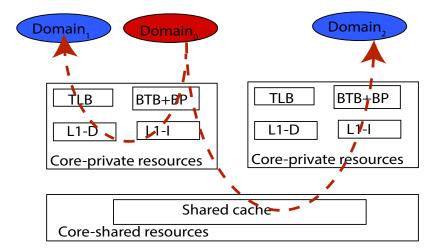

| 4.1  | Threat scenarios: The arrow from Domain <sub>0</sub> to Domain <sub>1</sub> represents the confinement scenario of information leakage through intra-core covert channels, while the arrow from Domain <sub>0</sub> to Domain <sub>2</sub> indicates the cloud scenario of a cross-core side channel through a shared cache | 59 |

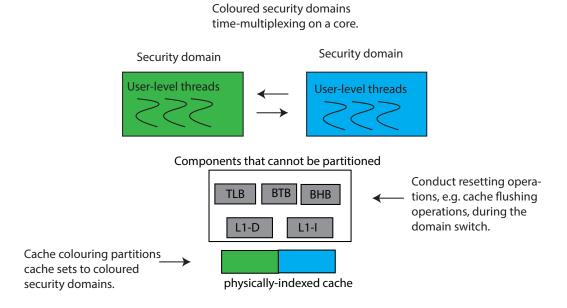

| 4.2  | An overview of mitigating covert timing channels between two security domains executing on a core.                                                                                                                                                                                                                          | 60 |

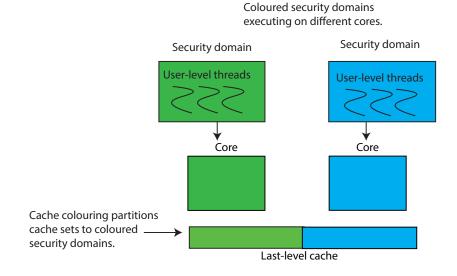

| 4.3  | An overview of mitigating timing side channels between two security domains                                                                                                                                                                                                                                                 |    |

|      | executing on different cores                                                                                                                                                                                                                                                                                                | 61 |

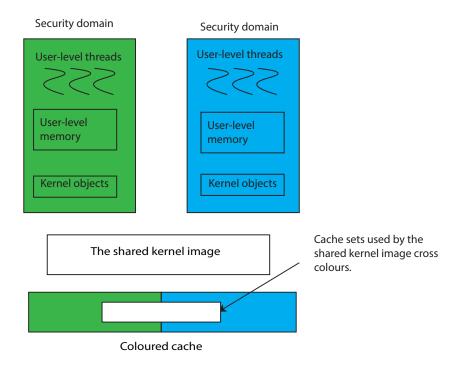

| 4.4  | Coloured security domains share an un-coloured kernel image                                                                                                                                                                                                                                                                 | 64 |

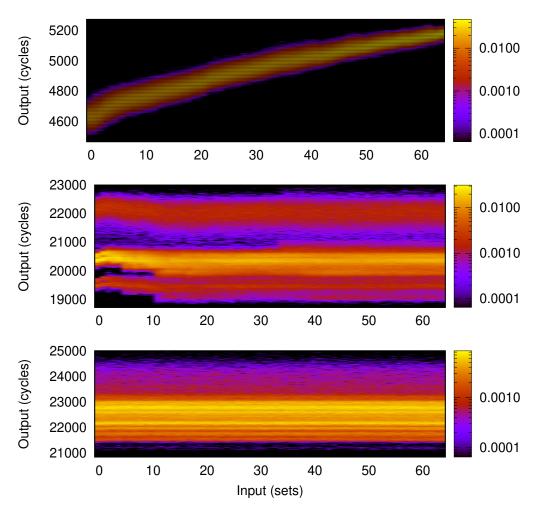

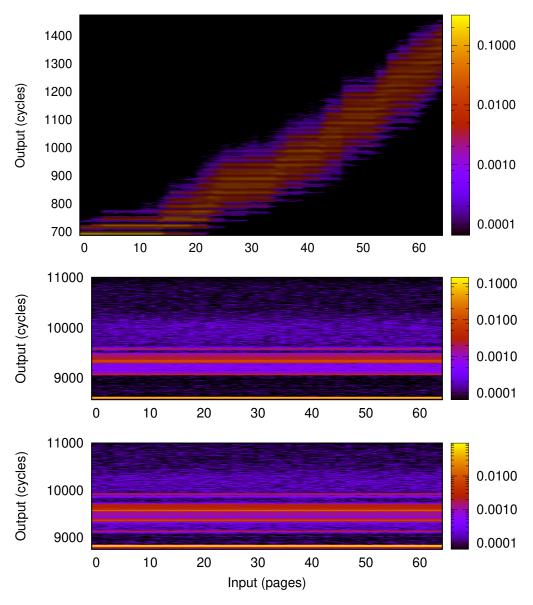

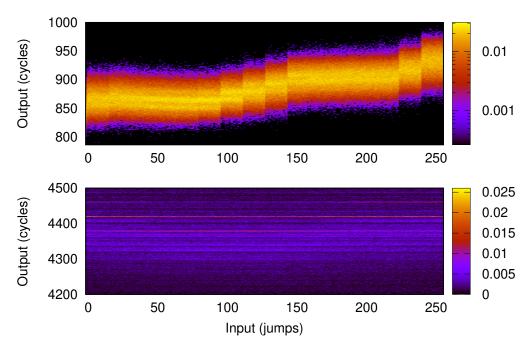

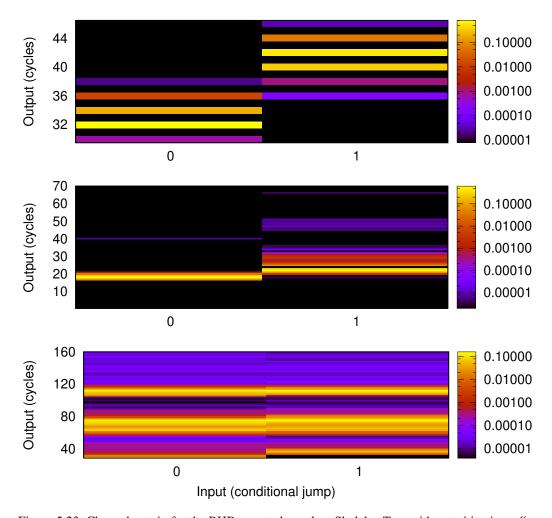

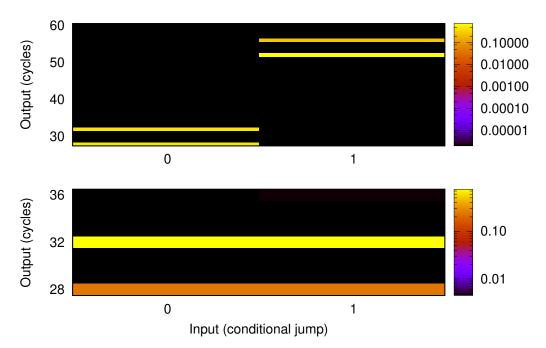

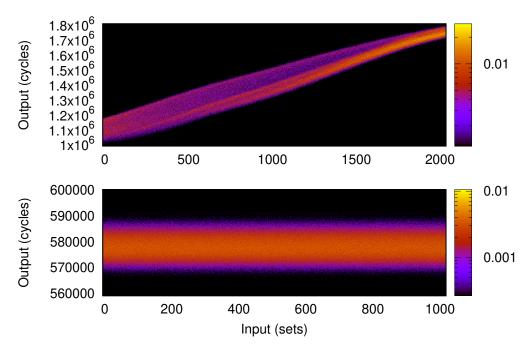

| 5.1  | Covert timing channels on core-private cache and cache-like components                                                                                                                                                                                                                                                      | 67 |

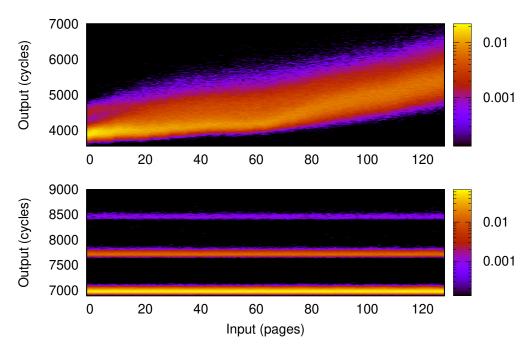

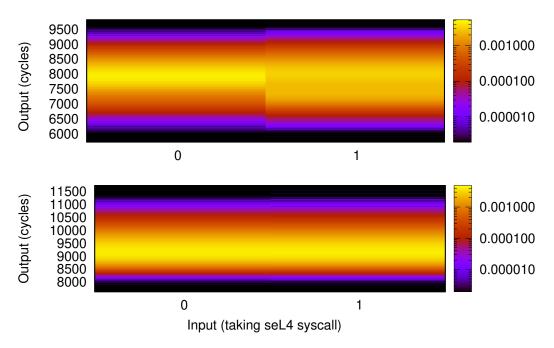

| 5.2  | The covert timing channel on the L1-D cache                                                                                                                                                                                                                                                                                 | 69 |

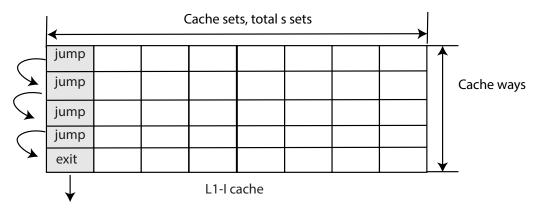

| 5.3  | The covert timing channel on the L1-I cache                                                                                                                                                                                                                                                                                 | 70 |

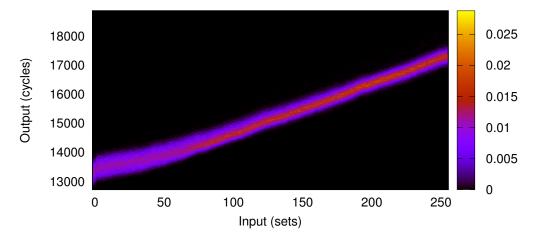

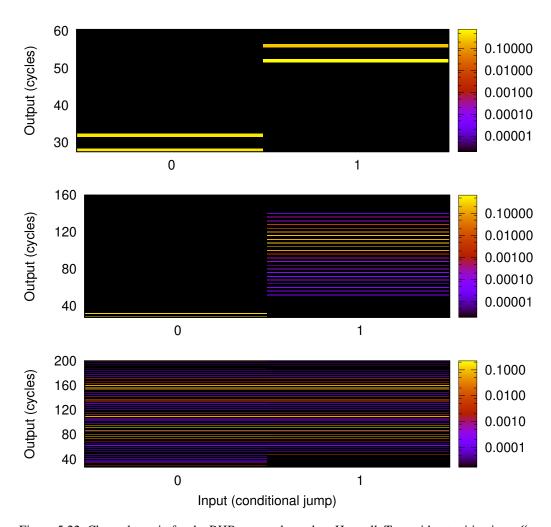

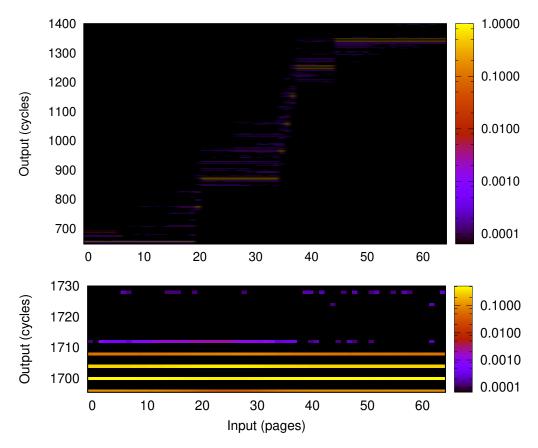

| 5.4  | Channel matrix for the unmitigated L1-I covert channel on an Arm Cortex-A9.                                                                                                                                                                                                                                                 | 76 |

| 5.5  | Channel matrix for the mitigated L1-I covert channel on an Arm Cortex-A9                                                                                                                                                                                                                                                    | 76 |

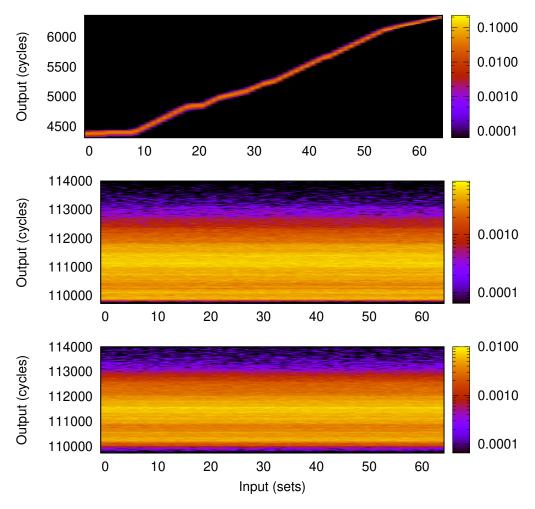

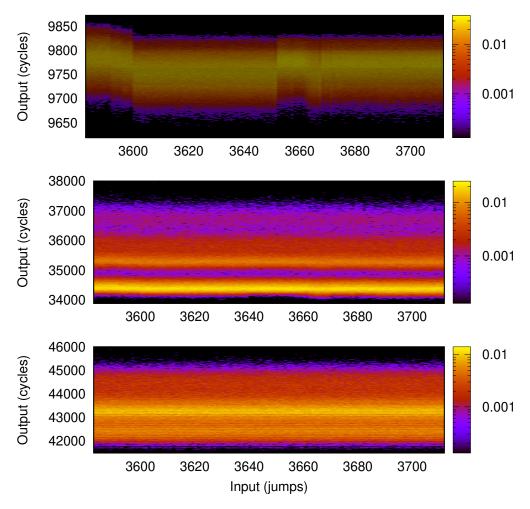

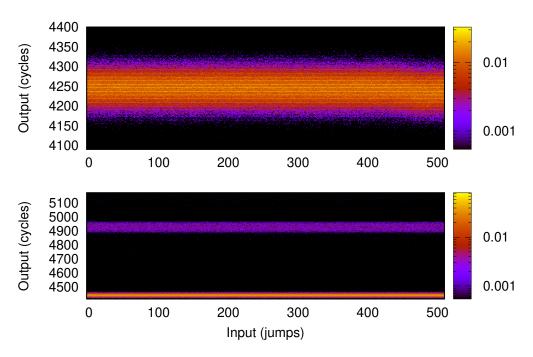

| 5.6  | Channel matrix for the L1-D covert channel on Haswell                                                                                                                                                                                                                                                                       | 89 |

| 5.7  | Channel matrix for the L1-D covert channel on Skylake                                                                                                                                                                                                                                                                       | 90 |

| 5.8  | Channel matrix for the L1-D covert channel on Arm Cortex-A9                                                                                                                                                                                                                                                                 | 91 |

| 5.9  | Channel matrix for the L1-D covert channel on Arm Cortex-A53                                                                                                                                                                                                                                                                | 91 |

|      | Channel matrix for the L1-I covert channel on Haswell                                                                                                                                                                                                                                                                       | 92 |

|      | Channel matrix for the L1-I covert channel on Skylake                                                                                                                                                                                                                                                                       | 93 |

|      | Channel matrix for the L1-I covert channel on Arm Cortex-A9                                                                                                                                                                                                                                                                 | 94 |

|      | Channel matrix for the L1-I covert channel on Arm Cortex-A53                                                                                                                                                                                                                                                                | 94 |

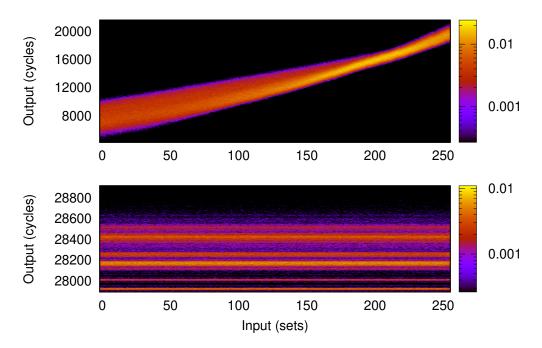

| 5.14 | Channel matrix for the TLB covert channel on Haswell                                                                                                                                                                                                                                                                        | 95 |

| 5.15  | Channel matrix for the TLB covert channel on Skylake                                                              | 96  |

|-------|-------------------------------------------------------------------------------------------------------------------|-----|

|       | Channel matrix for the TLB covert channel on Arm Cortex-A9                                                        | 97  |

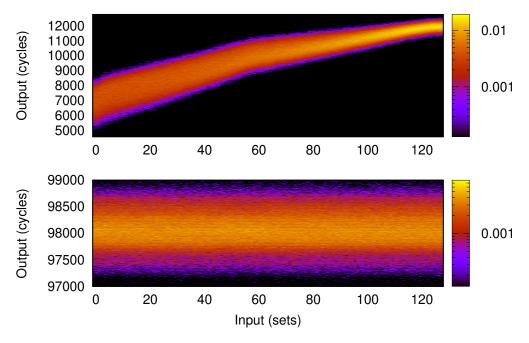

| 5.17  | Channel matrix for the TLB covert channel on Arm Cortex-A53                                                       | 97  |

| 5.18  | Channel matrix for the BTB covert channel on Haswell                                                              | 98  |

| 5.19  | Channel matrix for the BTB covert channel on Skylake                                                              | 99  |

|       | Channel matrix for the BTB covert channel on Arm Cortex-A9                                                        | 100 |

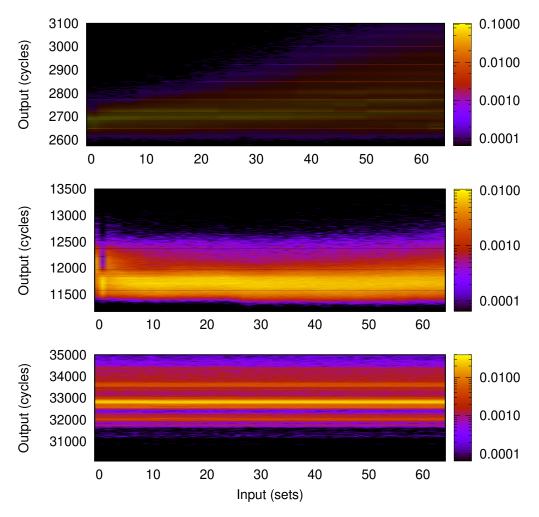

| 5.21  | Channel matrix for the BTB covert channel on Arm Cortex-A53                                                       | 100 |

| 5.22  | Channel matrix for the BHB covert channel on Haswell                                                              | 101 |

| 5.23  | Channel matrix for the BHB covert channel on Skylake                                                              | 102 |

| 5.24  | Channel matrix for the BHB covert channel on Arm Cortex-A9                                                        | 103 |

| 5.25  | Channel matrix for the BHB covert channel on Arm Cortex-A53                                                       | 103 |

|       |                                                                                                                   |     |

| 6.1   | Coloured security domain.                                                                                         | 109 |

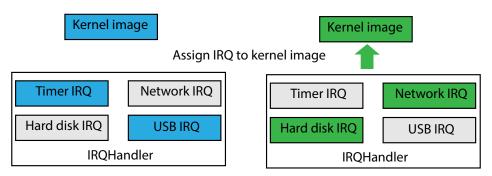

| 6.2   | Partitioning IRQs sources by assigning IRQHandler capabilities to kernel images.                                  |     |

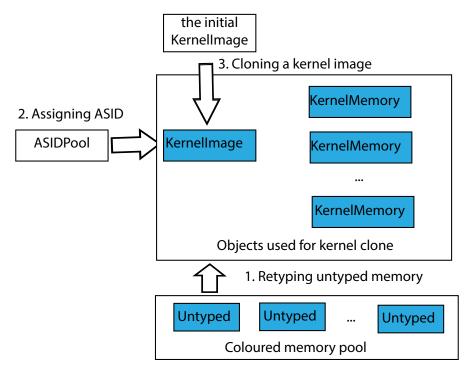

| 6.3   | An overview of the kernel clone mechanism                                                                         | 113 |

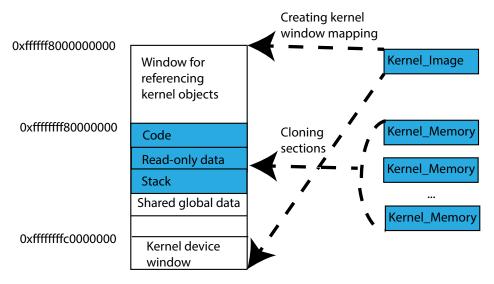

| 6.4   | Cloning a kernel window mapping on x86                                                                            | 114 |

| 6.5   | The structure of the kernel metadata                                                                              | 115 |

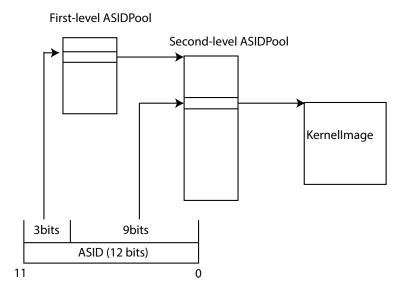

| 6.6   | Addressing a kernel image with an ASID on x86                                                                     | 115 |

| 6.7   | The configured domain tick length, K represents kernel mode                                                       | 120 |

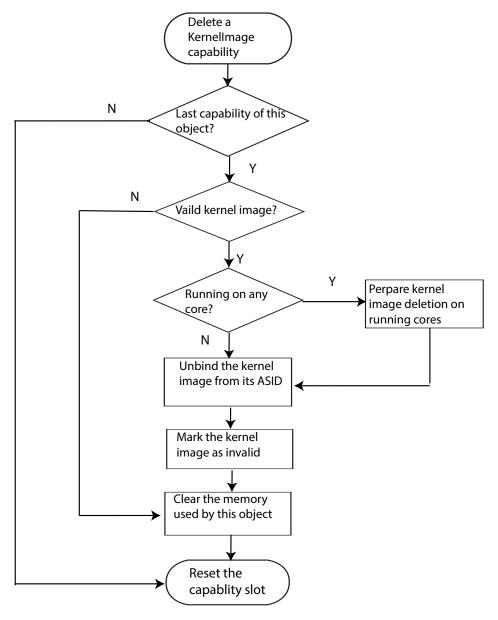

| 6.8   | The flow chart of deleting a Kernellmage capability                                                               | 124 |

| 6.9   | The flow chart of preparing a kernel image deletion                                                               | 125 |

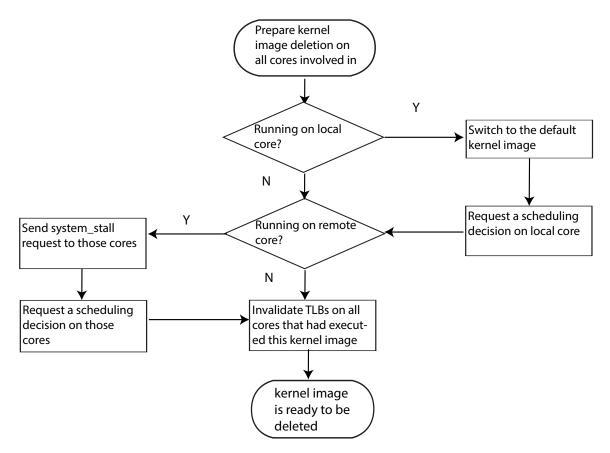

| 6.10  |                                                                                                                   | 126 |

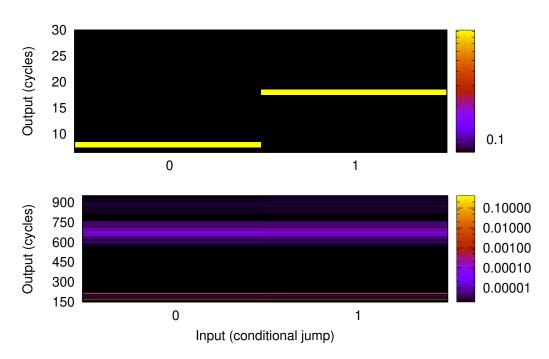

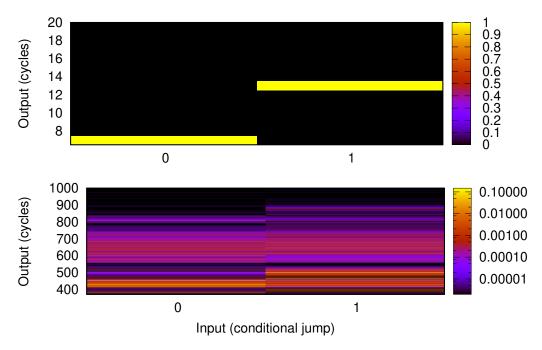

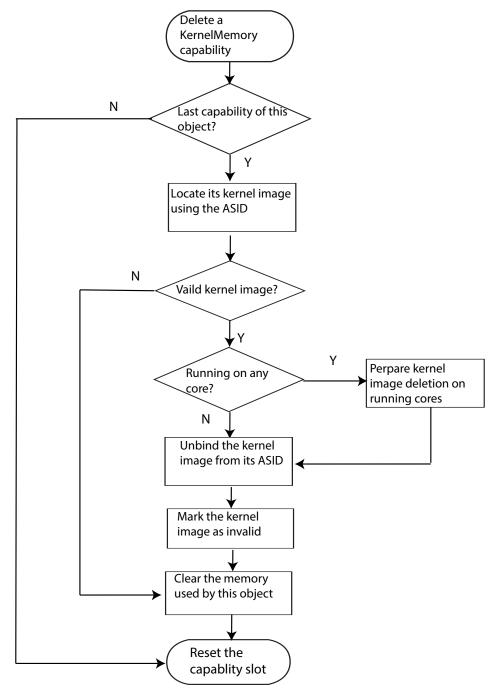

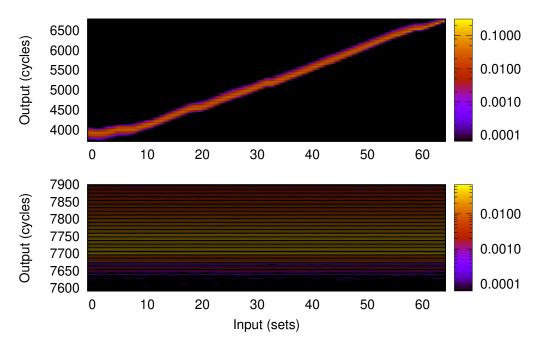

| 6.11  |                                                                                                                   | 131 |

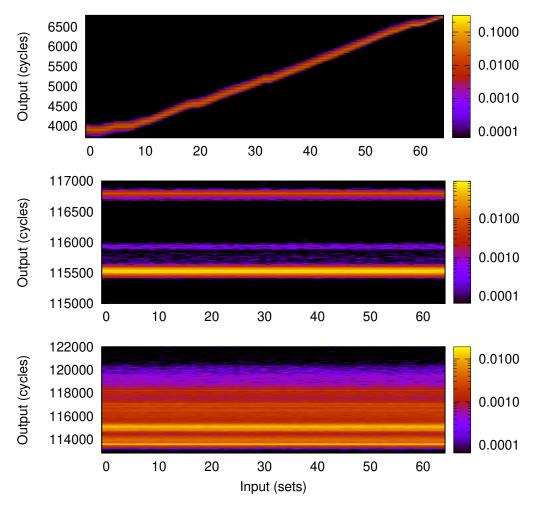

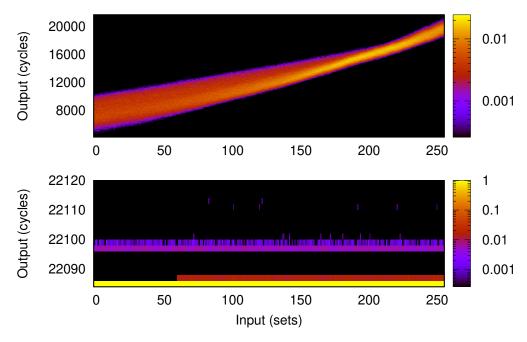

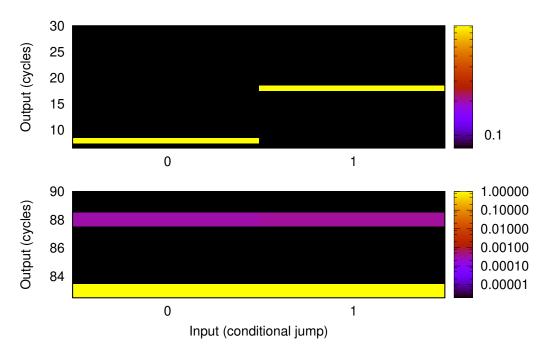

|       | The L1-D cache channel on Sabre (Arm Cortex-A9)                                                                   | 132 |

| 0.13  | The L1-D cache covert channel on Sabre (Arm Cortex-A9), mitigated with                                            | 132 |

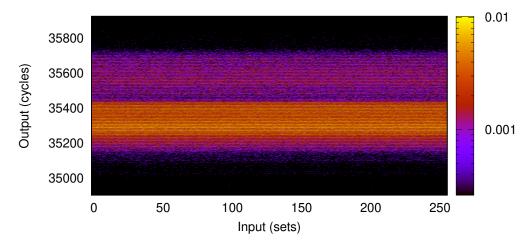

| 6 1 1 | time protection and disabling both prefetcher and branch prediction unit The L1-I cache covert channel on Haswell | 132 |

|       | The L1-I cache covert channel on Sabre (Arm Cortex-A9)                                                            | 133 |

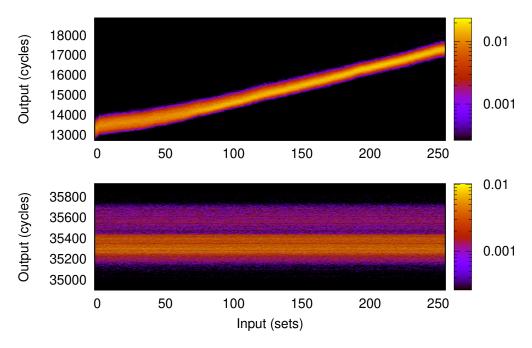

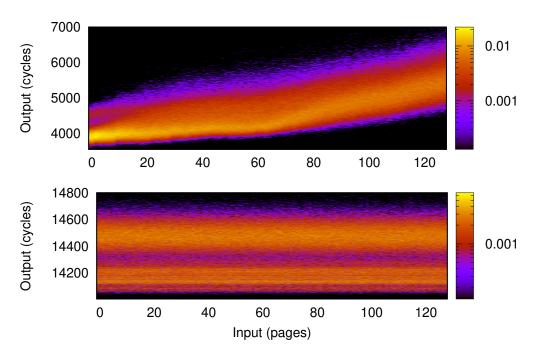

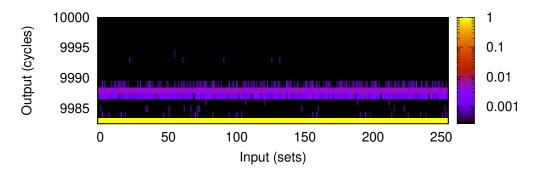

|       | The TLB covert channel on Haswell                                                                                 | 135 |

|       | The TLB covert channel on Sabre (Arm Cortex-A9).                                                                  | 136 |

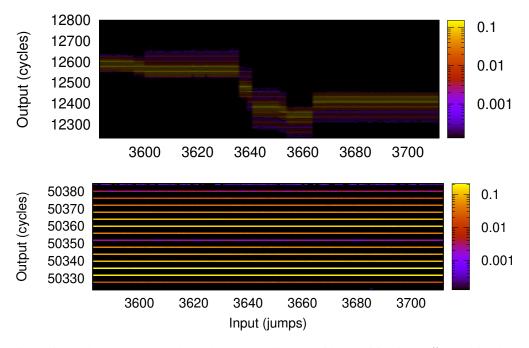

|       | The BTB covert channel on Haswell                                                                                 | 136 |

|       | The BTB covert channel on Sabre (Arm Cortex-A9)                                                                   | 137 |

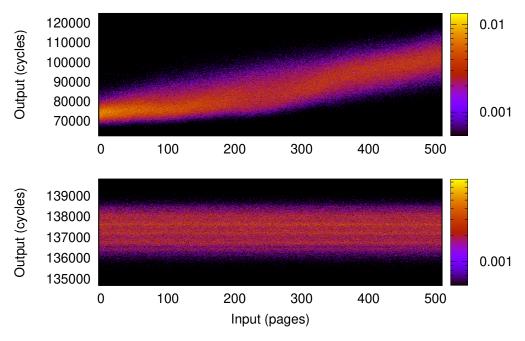

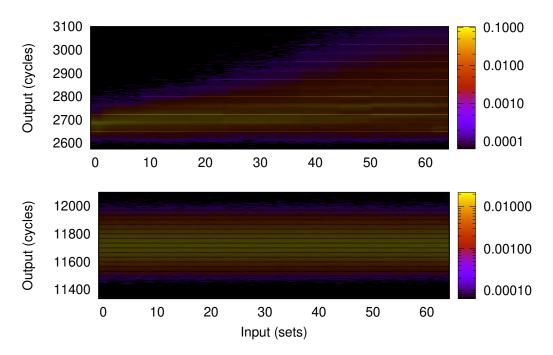

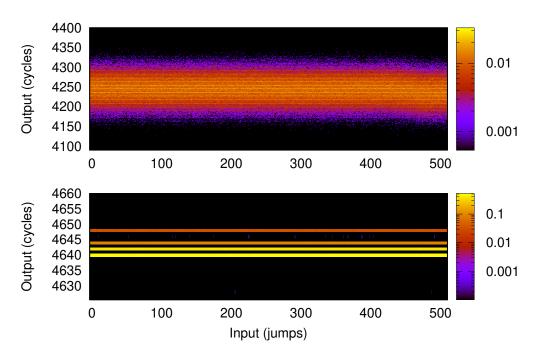

|       | The BHB covert channel on Haswell.                                                                                | 137 |

|       | The BHB covert channel on Sabre (Arm Cortex-A9)                                                                   | 138 |

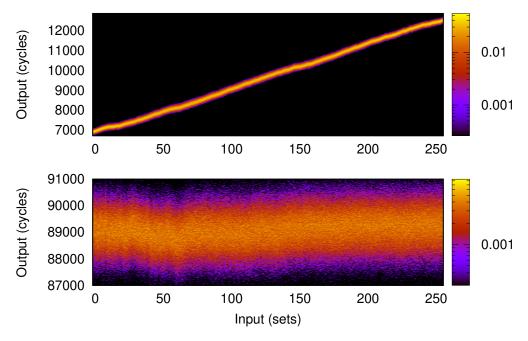

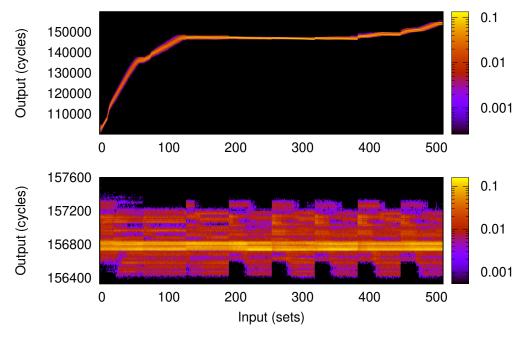

|       | The L2 cache covert channel on Haswell                                                                            | 139 |

|       | The L2 cache covert channel on Haswell, mitigated with time protection and                                        | 10) |

| 0.25  | disabling prefetcher                                                                                              | 139 |

| 6.24  | The L2 cache covert channel on Sabre (Arm Cortex-A9)                                                              | 140 |

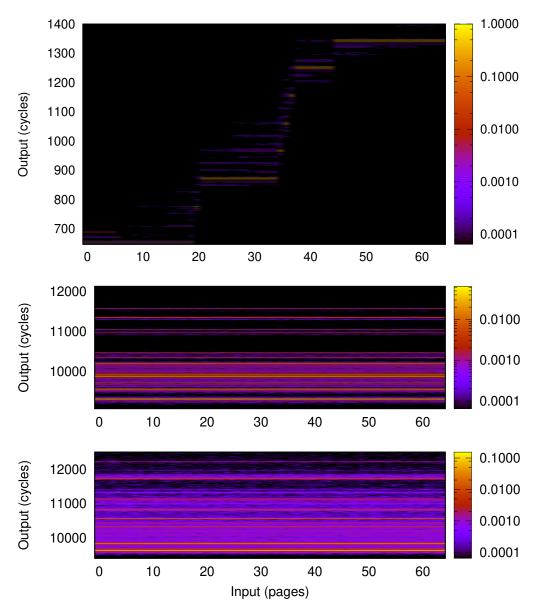

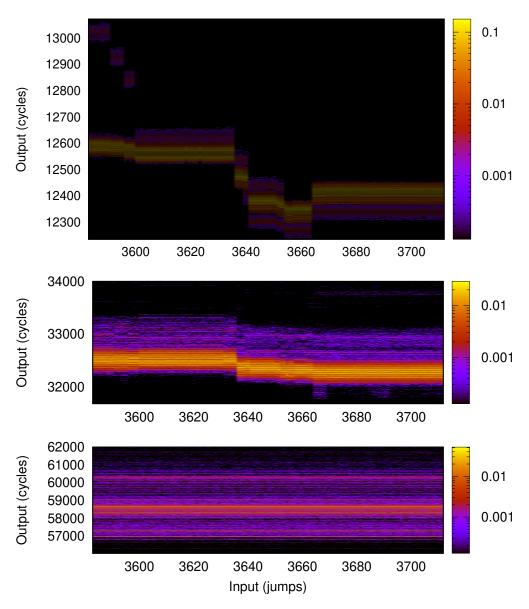

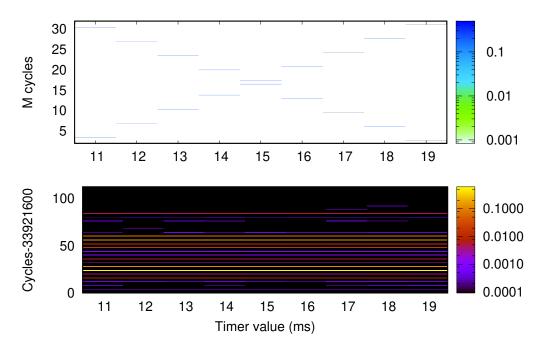

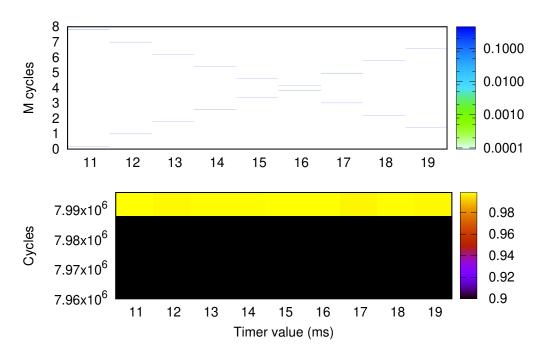

|       | The system scenario of the cache-flush channel                                                                    | 141 |

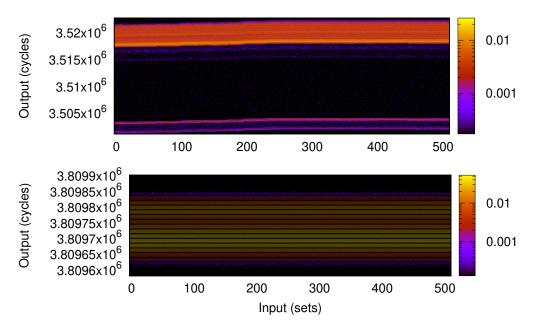

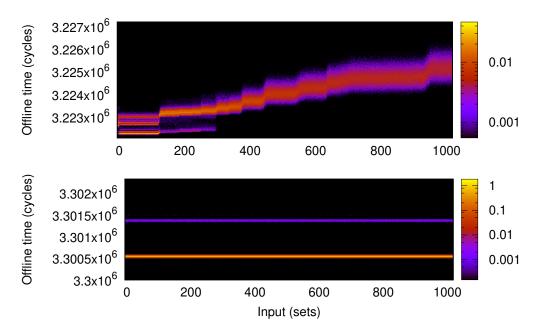

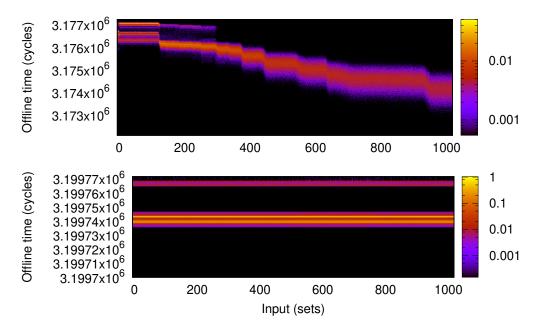

|       | The offline time observed by the spy vs. the Trojan's cache footprint on Haswell                                  |     |

|       | (x86)                                                                                                             | 142 |

| 6.27  | The online time observed by the spy vs. the Trojan's cache footprint on Haswell                                   |     |

|       | (x86)                                                                                                             | 142 |

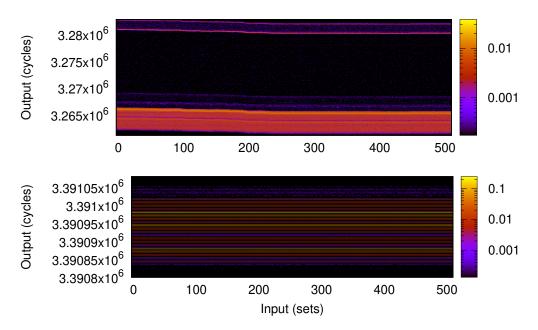

| 6.28  | The offline time observed by the spy vs. the Trojan's cache footprint on Sabre                                    |     |

|       | (Arm Cortex-A9)                                                                                                   | 143 |

| 6.29  | The online time observed by the spy vs. the Trojan's cache footprint on Sabre                                     |     |

|       | (Arm Cortex-A9)                                                                                                   | 143 |

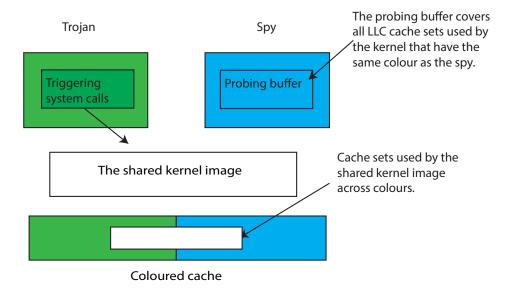

| 6.30  | The Trojan sends information to the spy via a shared kernel image, even though                                    |     |

|       | both of them are coloured.                                                                                        | 145 |

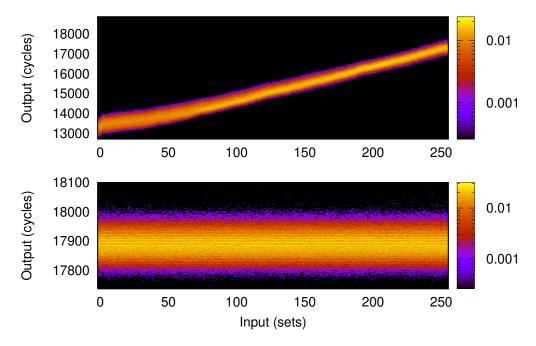

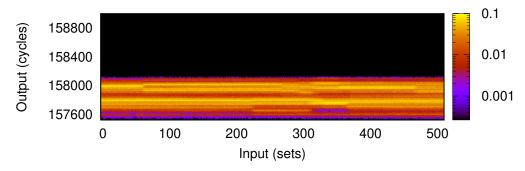

| 6.31 | Kernel covert timing channel on Haswell (x86)                                 | 146 |

|------|-------------------------------------------------------------------------------|-----|

| 6.32 | Kernel covert timing channel on Sabre (Arm Cortex-A9)                         | 147 |

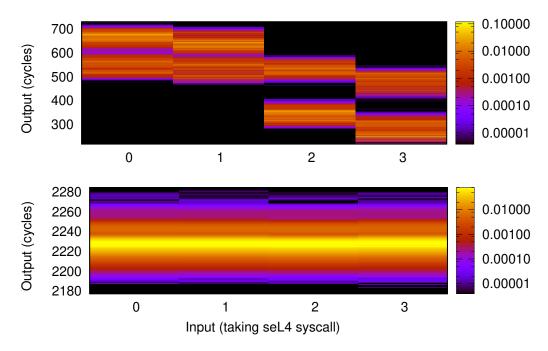

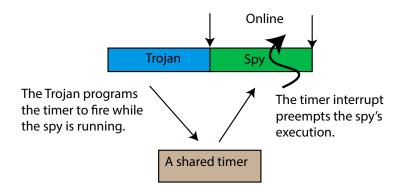

| 6.33 | The Trojan sends information to the spy via a shared timer interrupt          | 148 |

| 6.34 | The online time observed by the spy vs. the timer interrupt configured by the |     |

|      | Trojan on Haswell (x86)                                                       | 149 |

| 6.35 | The online time observed by the spy vs. the timer interrupt configured by the |     |

|      | Trojan on Sabre (Arm Cortex-A9)                                               | 150 |

| 6.36 | Unmitigated concurrent LLC side-channel attack on Haswell (x86)               | 150 |

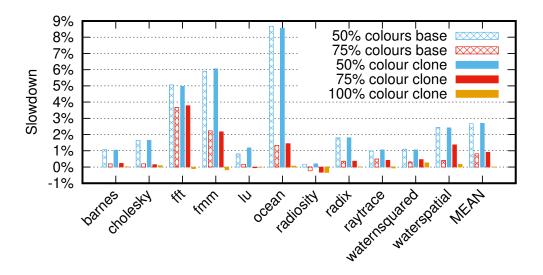

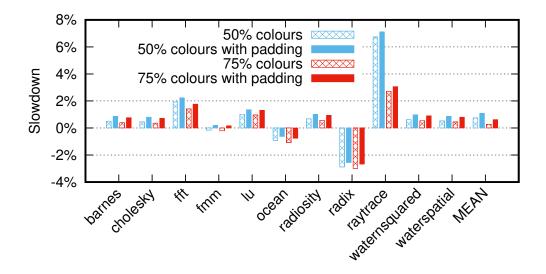

| 6.37 | Slowdowns of Splash-2 benchmarks against baseline kernel without partition-   |     |

|      | ing for Haswell (x86) and geometric mean                                      | 156 |

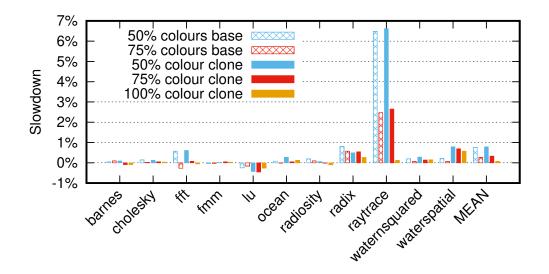

| 6.38 | Slowdowns of Splash-2 benchmarks against baseline kernel without partition-   |     |

|      | ing for Sabre (Arm Cortex-A9) and geometric mean                              | 157 |

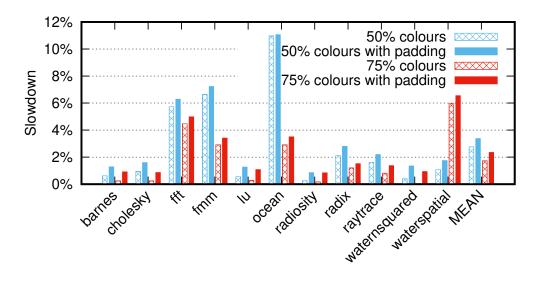

| 6.39 | Slowdowns of Splash-2 benchmarks of time protection, including the in-        |     |

|      | creased domain-switching latency in a time-shared setup, against baseline     |     |

|      | kernel without partitioning for Haswell (x86) and geometric mean              | 158 |

| 6.40 | Slowdowns of Splash-2 benchmarks of time protection, including the in-        |     |

|      | creased domain-switching latency in a time-shared setup, against baseline     |     |

|      | kernel without partitioning for Sabre (Arm Cortex-A9) and geometric mean.     | 159 |

# **List of Tables**

| 2.1  | Kernel objects in seL4 for 32-bit Arm processors                                     | 25   |

|------|--------------------------------------------------------------------------------------|------|

| 5.1  | Experimental hardware, covering 2 generations of microarchitectures across           |      |

|      | x86 and Arm                                                                          | 72   |

| 5.2  | Architectural support on x86 for mitigating on-core timing channels                  | 73   |

| 5.3  | Architectural support on Arm for mitigating on-core timing channels                  | 74   |

| 5.4  | Observed unmitigated ("none"), maximally mitigated ("full"), and mitigated           |      |

|      | without IBC ("no IBC", x86 only) MI (millibit) and the 95% confidence interval       |      |

|      | of simulated zero-leakage channels ( $\mathcal{M}_0$ )                               | 80   |

| 6.1  | Operations for flushing on-core states                                               | 119  |

| 6.2  | Hardware platforms                                                                   | 128  |

| 6.3  | Cost of cache flushes                                                                | 129  |

| 6.4  | MI (millibit) of unmitigated (raw) covert timing channels on cache or cache-         |      |

|      | like components, mitigated with full cache flush (full flush) and time protection    |      |

|      | (protected)                                                                          | 130  |

| 6.5  | Channels resulting from cache-flush latency (mb) without and with time pro-          |      |

|      | tection.                                                                             | 144  |

| 6.6  | MI (mb) of the interrupt channel (shared), mitigated with time protection (IRQ       |      |

|      | partitioning)                                                                        | 149  |

| 6.7  | IPC performance microbenchmarks                                                      | 151  |

| 6.8  | Cost $(\mu s)$ of switching away from a domain running various cache probing $(spy)$ | .153 |

| 6.9  | Cost of cloning ( $\mu$ s) on seL4 with coloured memory                              | 154  |

| 6.10 | Cost of fork and exec system calls on Linux ( $\mu$ s)                               | 155  |

# Listings

| 5.1 | BHB channel implementation on x86                                       | 71  |

|-----|-------------------------------------------------------------------------|-----|

| 6.1 | The format of Kernellmage capability on the 64 bit x86 architecture     | 111 |

| 6.2 | The format of KernelMemory capability on the 64 bit x86 architecture    | 112 |

| 6.3 | Switching kernel image on x86                                           | 118 |

| 6.4 | The layout of the kernel image on x86                                   | 121 |

| 6.5 | The pesudo code for acknowledging any pending interrupts that belong to |     |

|     | the previous running kernel image on x86                                | 122 |

| 6.6 | The online and offline time measurement                                 | 141 |

| 6.7 | Detecting a system tick by probing on the time-stamp counter            | 145 |

| 6.8 | The Trojan programs the timer interrupts in every system tick           | 148 |

# 1 Introduction

To achieve contiguous growth of compute power, computer architectures have become increasingly complicated as a result of consolidating more and more functional features on hardware. Currently, central processing units (CPUs) are equipped with various functional units, such as multi-stage pipelines (e.g., commonly more than 10 stages on Intel processors [Intel, c]), sophisticated speculative execution engines, on-core caches, or internal buses [Intel, 2018b].

Meanwhile, both the capacity and complexity of hardware caches have continued to increase. For example, Intel's Conroe architecture, which was released in 2006, contains two levels of caches with a maximum capacity of 4 MiB [Int, 2018a], whereas Intel's Skylake architecture which was released in 2015 has three levels of caches offering more than 30 MiB of capacity [Int, 2018c]. Additionally, this trend occurs on all the other hardware components that cache the execution history, including units that store destinations of recently taken branch instructions, or buffers that cache the result of recently solved virtual-to-physical address translation. For the rest of this thesis, we call these components *cache-like* hardware components.

Due to the increased processing power of computer hardware, industry has consolidated more and more software services on a single hardware platform, which are shared by mutually distrusted programs or virtual machines (VMs). Systems with such sharing range from cloud computing services to embedded platforms. For instance, infrastructure-as-a-service (IaaS) [Microsoft, 2018], a cloud computing service, hosts multiple mutually distrusting VMs on a hardware platform, through the management service provided by the bottom layer virtual machine monitor (VMM) or hypervisor. Similarly, the embedded operating system (OS) schedules applications authored by different companies together on a smartphone platform.

Sharing a hardware platform among mutually distrusting software entities indeed benefits the economy by offering virtualised machines as a service. However, sharing requires the system to provide much stronger isolation services to mutually distrusting VMs or software components, to achieve the same level of protection as if they are executing on dedicated hardware. Therefore, the software platform has to enforce a *security policy*

which controls or limits information flow among different software entities (i.e., security domains), such as VMs, mobile applications, or web pages.

# 1.1 Microarchitectural Timing Channels

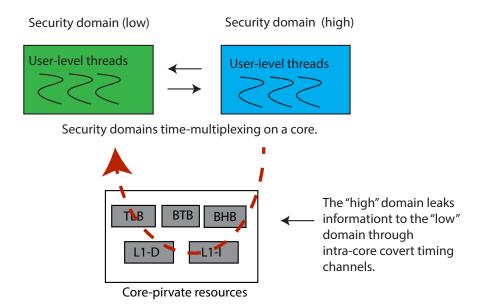

*Microarchitectural* timing channels threaten security on shared systems, by exploiting timing variances resulting from the shared use of hardware components, such as caches. These channels transfer secret information through timing which is affected by the shared microarchitecture state, such as cached contents of memory or the history of recently executed branch instructions. To transmit information, a sender program deliberately or incidentally manipulates hardware state during its execution, which affects the measurable efficiency of a receiver program.

The *cache-based timing channel* is a classic microarchitectural timing attack [Actiçmez, 2007; Hu, 1992; Osvik et al., 2006; Tromer et al., 2010], which transmits information between a sender and a receiver through competing shared cache lines. For sending a signal, the sender modulates its cache footprint during its execution, which then can be detected by the receiver through measuring its latency by systematically touching those cache lines. Low latency implies that a line is still cached from a previous access, whereas a high latency implies that the sender has evicted the line during its execution.

Timing channel attacks are applicable not only to caches, but also to other hardware components that cache execution histories, such as the branch predictor [Evtyushkin et al., 2016a], or the translation look-aside buffer (TLB) [Hund et al., 2013]. Recently, researchers have demonstrated a series of sophisticated microarchitectural timing channel attacks that exploit side effects of CPU features designed for performance improvement, including speculative execution [Kocher et al., 2019], and microinstruction scheduling on an out-of-order execution pipeline [Lipp et al., 2018; Van Bulck et al., 2018].

The cause of microarchitectural timing channels is resource contention on shared hardware components that have limitations on either capacity or bandwidth, depending on the type of resource. The above mentioned cache-based timing channel exploits the capacity limitation on a shared cache. As they hold microarchitectural state, caches and cache-like components are called *stateful resources*. In contrast, bandwidth-limited resources, such as interconnects, are *stateless* and require truly concurrent access to generate a timing channel. For example, a sender can transfer information through its bandwidth consumption on a shared bus, which can be detected by a concurrently executing receiver though sensing its share of the available bandwidth.

## 1.2 Research Aims

This research focuses on the open problem of preventing microarchitectural timing channels through the security enforcement by the OS. Our approach is called *time protection*, in

analogy to the established memory protection. We focus on providing a system solution for preventing timing channels on stateful resources, as preventing stateless channels requires bandwidth partitioning which does not exist on contemporary mainstream hardware.

Understanding the landscape To achieve our research goal, we examine all published microarchitectural timing attacks and related countermeasures. Through our study, we discover that all types of stateful resources, including cache and cache-like components, have been exploited as timing channels in intra-core as well as inter-core attacks. As these attacks result from sharing, a principled defence must prevent such sharing by partitioning all resources, either spatially or temporally. Such partitioning should be provided by the OS, in line with its general responsibility for enforcing security. The former requires resetting all history-dependent microarchitectural states between time slices, whereas the latter requires that the OS has control on resource allocation.

Virtualising all time sources can also mitigate timing channels as it removes the shared time source between the sender and the receiver. However, this mechanism is not only a very expensive solution [Li et al., 2013] but also impossible to apply to domains that interact with the physical world, including direct access to networks. Therefore, we focus on the above mentioned partitioning mechanisms.

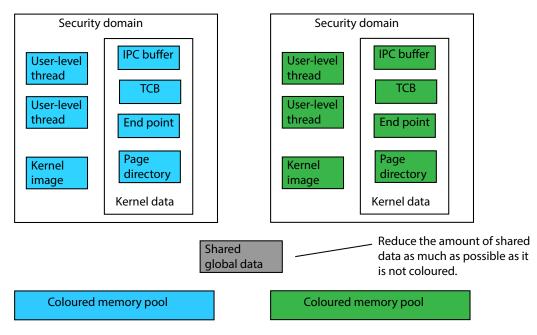

**Time protection—a core OS duty** We propose to provide *time protection* in the OS, treating temporal isolation analogously to memory protection used for preventing spatial interference. This requires that a hardware platform provide options to either partition or reset related microarchitectural states. Therefore, the OS can provide mechanisms to create domains as a security container for user-level threads, with the aim of preventing microarchitectural timing channels between domains through either resetting or partitioning shared hardware states (Figure 1.1).

Figure 1.1: An overview of the system solution for mitigating microarchitecture timing channels.

Investigating hardware resetting operations On mainstream hardware, an OS or a hypervisor can partition caches that are indexed by physical address with a software technique called cache colouring [Bershad et al., 1994; Kessler and Hill, 1992; Liedtke et al., 1997]. However, the cache colouring technique is not suitable for core-private caches or cache-like components that are indexed by virtual address, as the layout of the virtual address space is out of the OS's control. Hence, temporal partitioning (time multiplexing) is the only possible approach. This requires resetting the hardware state with flushing operations becomes the only option for mitigating timing attacks on virtually-indexed hardware components.

In order to understand the feasibility of this approach, we investigate the effectiveness of hardware resetting operations for mitigating those channels. We implement all possible timing attacks that are based on contending core-private caches or cache-like components. Then we analyse both original and mitigated channels on multiple generations of x86 and Arm processors. From this, we discover that selected hardware platforms are effective in mitigating many of the studied channels. However, there are residual channels on hardware state used for predicting branch instructions on studied x86 processors, and on states used for executing branch instructions on the Arm Cortex-A53 processor. The primary cause of these residual channels is that the current instruction-set architecture (ISA) is not a sufficient contract for ensuring temporal isolation, as it is completely hides the microarchitectural state and consequently does not provide the mechanisms required for temporally partitioning. As such, the ISA is insufficient for letting the OS enforce security. Therefore, we propose an *augmented ISA* as a new hardware-software contract to provide sufficient support on enforcing temporal isolation.

**Achieving the proposed system solution** We propose OS mechanisms for providing time protection, through a combination of partitioning and resetting techniques, with the assumption that the hardware can provide sufficient support for complete temporal isolation.

We implement our prototype on the seL4 microkernel, not only because of its integrity and confidentiality guarantees [Klein et al., 2014], but also for benefiting from its existing mechanisms for memory allocation. Additionally, previous work demonstrated that the kernel does not contain any storage channels [Murray et al., 2013], which gives us strong confidence in investigating the only possible remaining class of covert channels—timing channels.

Our solution allows not only partitioning user-level memory (including memory managed by the kernel), but also the kernel image itself with a new kernel mechanism called *kernel cloning*. Kernel cloning allows creating an almost complete copy of the kernel image that can be assigned to corresponding security domains, with an option of also partitioning hardware interrupts. With existing kernel mechanisms, we implement a system prototype and demonstrate that time protection effectively mitigates studied channels with a low impact on system performance.

# 1.3 Research Contributions and Thesis Outline

## 1.3.1 Research contributions

Our research produces the following contributions:

- We conduct a systematic study on all published microarchitectural timing attacks and related countermeasures (Chapter 3);

- we study the effectiveness of hardware-manufacturer provided operations on mitigating intra-core timing channels, for multiple generations of x86 and Arm processors (Chapter 5);

- we discover that the indirect branch control (IBC) mechanism [Intel, 2018c] introduced by Intel for mitigating the Spectre attack [Kocher et al., 2019] is partially effective at mitigating intra-core timing channels but leaves residual channels (Section 5.4);

- we propose an augmented ISA, a new software-hardware contract, as a solution for preventing any hidden microarchitectural state being exploited as timing channels. (Section 5.5);

- we establish the system requirements for enforcing confinement in the presence of microarchitectural timing channels (Section 6.1);

- we propose the *kernel cloning* mechanism for constructing dedicated kernel images that can be assigned to corresponding security domains (Section 6.2);

- we extend the cloning mechanism with an option for partitioning hardware interrupt sources (Section 6.2);

- we demonstrate the implementation on seL4, supporting both x86 and Arm multicore platforms (Section 6.4);

- we evaluate our system prototype for mitigating microarchitectural timing channels, showing that it is effective at closing studied microarchitectural timing channels, within limitations of present hardware (Section 6.5.2);

- we show that our mechanism introduces very low overhead on system performance (Section 6.5.3).

### 1.3.2 Thesis outline

This thesis is structured as follows. In Chapter 2, we provide the necessary background on timing channels, related microarchitecture, cache colouring, microkernels, and the seL4 microkernel. In Chapter 3, we define our research scope and examine the existing work on microarchitectural timing attacks and corresponding countermeasures. In Chapter 4, we define threat scenarios of this work, as well as hardware requirements for mitigating studied

channels, and propose a system solution for providing time protection. In Chapter 5, we show our study on the effectiveness of hardware provided operations on providing temporal isolation for mitigating intra-core timing channels, and our proposed augmented ISA as a solution for the lack of definition on time protection in the existing ISA. In Chapter 6, we demonstrate the kernel cloning mechanism which provides the service for assigning dedicated kernel images and hardware interrupts to security domains. We also evaluate the effectiveness of our time protection mechanisms and their performance overhead. Finally, in Chapter 7, we conclude our research with a summary of our work, including a discussion of the future work.

# 2 Background

# 2.1 Timing Channels

Interest in information leakage and secure data processing historically was centred on sensitive, and particularly cryptographic, military and government systems [Denning, 1976]. However, many—such as Lampson [1973]—recognised the problems faced by tenants of an untrusted commercial computing platform of the sort that is now commonplace. The US government's "Orange Book" standard [DoD], for example, collected requirements for systems operating at various security classification levels. The Orange Book introduced standards for information leakage in the form of limits on channel bandwidth. While these were seldom if ever actually achieved, this approach strongly influenced the direction of later work.

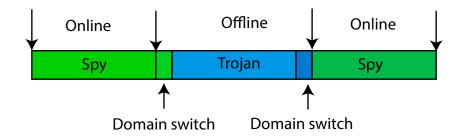

Threat models for information leakage are often classified as either *covert channels* or *side channels*. Covert channels allow colluding programs to transfer information by means that bypass system security policy. A typical attack scenario includes a *Trojan* (sender), who has access to sensitive information, and a *spy* (receiver), who does not have access to that sensitive information but is able to communicate easily with the external world. A side channel is similar to a covert channel, except that instead of relying on a Trojan to transfer information that is deliberately leaked, an attacker exploits the side channel to recover sensitive information owned by a *victim* through existing system services. Side channel attacks are much harder to implement than covert channel attacks as they steal information from non-colluding victims. As a result, the implementations of side channel attacks are normally more complicated and more interesting than covert channels which leak information through similar attacking mechanisms.