# Inside L4/MIPS

# **Anatomy of a High-Performance Microkernel**

# **Gernot Heiser**

Version 2.19 (5 syscalls+scheduling) of January 30, 2001

disy@cse.unsw.edu.au http://www.cse.unsw.edu.au/~disy/ Operating Systems and Distributed Systems Group School of Computer Science and Engineering The University of New South Wales UNSW Sydney 2052, Australia

Permission to make digital/hard copy of part or all of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage, the copyright notice, the title of the publication and its date appear, and notice is given that copying is by permission of the authors. To copy otherwise, to republish, to post on servers, or to redistribute to lists requires prior specific permission and/or a fee.

Copyright ©1999–2001 by Gernot Heiser, The University of New South Wales.

#### Abstract

This document is an attempt to document the internal structure of L4 and its operations. It is based on the L4 implementation for the MIPS R4x00 (L4/MIPS), kernel version 79 (February 1999). The document is meant as an aid in teaching operating systems internals, and as a guide for kernel implementors. While the actual code discussed is very specific to the MIPS processor, much of the overall structure and logic of L4 is quite uniform across platforms.

The present version of this report documents L4/MIPS data structures, exception handling and the IPC system call. Documentation of the implementation of the other system calls, and issues such as scheduling, will be added in the near future.

# Acknowledgments

This report would not have been possible without Jochen Liedtke, who created L4, and Kevin Elphinstone, who did an outstanding job in designing and implementing the MIPS version. Special thanks are due to both.

Thanks are also due to a number of other people who helped to get L4 into what is described here. Alan Au added a number of missing components to the kernel, and fixed a few bugs. UNSW undergraduate thesis students Brett Nash, Victoria Ong, Cristan Szmajda and Adam Wiggins studied the code, suggested a number of improvements, and helped with the documentation. Students taking Advanced Operating Systems at UNSW in 1997–1999 exercised the kernel and contributed to its stability.

# Contents

|   | List of Code Listings ix |         |                                          |      |

|---|--------------------------|---------|------------------------------------------|------|

|   | List                     | of Figu | res                                      | xiii |

|   | List                     | of Tabl | es                                       | xiv  |

|   | List                     | of Bug  | s and Restrictions                       | XV   |

| 1 | Intr                     | oductio | n                                        | 1    |

|   | 1.1                      | Intend  | ed Audience                              | 1    |

|   | 1.2                      | Why M   | ЛIPS?                                    | 2    |

|   | 1.3                      | Conve   | ntions                                   | 2    |

|   | 1.4                      | Structu | ıre                                      | 3    |

| 2 | Bac                      | kgroun  | 1                                        | 5    |

|   | 2.1                      | L4 Ov   | erview                                   | 5    |

|   |                          | 2.1.1   | L4 philosophy                            | 5    |

|   |                          | 2.1.2   | L4 abstractions                          | 6    |

|   | 2.2                      | Releva  | Int Features of the MIPS R4x00 Processor | 10   |

|   |                          | 2.2.1   | Target systems                           | 10   |

|   |                          | 2.2.2   | R4x00 general features                   | 10   |

|   |                          | 2.2.3   | Memory management unit                   | 11   |

|   |                          | 2.2.4   | Address space layout                     | 13   |

|   |                          | 2.2.5   | Exception processing                     | 15   |

| 3 | L4/N                     | MIPS O  | rganisation and Data Structures          | 17   |

|   | 3.1                      | L4/MI   | PS Source Structure                      | 17   |

|   | 3.2                      | Kernel  | Data Structures                          | 18   |

|   |                          | 3.2.1   | Kernel memory allocation                 | 18   |

### CONTENTS

|   |      | 3.2.2    | Miscellaneous kernel data: kernel_vars  | 19 |

|---|------|----------|-----------------------------------------|----|

|   |      | 3.2.3    | TCBs                                    | 20 |

|   |      | 3.2.4    | Other kernel data structures            | 22 |

| 4 | Exce | eption P | Processing                              | 23 |

|   | 4.1  | TLB M    | Iiss Handling                           | 23 |

|   |      | 4.1.1    | Fast miss handler                       | 23 |

|   |      | 4.1.2    | STLB miss handler                       | 25 |

|   | 4.2  | Genera   | al Exception Handling                   | 28 |

|   |      | 4.2.1    | General exception handler               | 28 |

|   |      | 4.2.2    | Return from exception                   | 30 |

|   |      | 4.2.3    | Exception dispatcher other_excpt        | 31 |

|   |      | 4.2.4    | TLB exceptions                          | 31 |

|   |      | 4.2.5    | Exceptions passed to the user           | 35 |

|   |      | 4.2.6    | TLB misses during long IPC              | 36 |

|   |      | 4.2.7    | Coprocessor unusable exception          | 44 |

| 5 | IPC  | Path     |                                         | 47 |

|   | 5.1  | Introdu  | uction                                  | 47 |

|   | 5.2  | Short I  | PC                                      | 47 |

|   |      | 5.2.1    | Send & receive: k_ipc                   | 48 |

|   |      | 5.2.2    | Fast context switch: thread_switch_fast | 52 |

|   |      | 5.2.3    | Discussion                              | 53 |

|   | 5.3  | Other S  | Short IPC Send Code                     | 55 |

|   |      | 5.3.1    | Non-blocking send: send_only_short      | 55 |

|   |      | 5.3.2    | Blocking send: pending                  | 56 |

|   |      | 5.3.3    | Short IPC send: odds & ends             | 57 |

|   |      | 5.3.4    | Discussion                              | 59 |

|   | 5.4  | Short I  | PC Receive                              | 59 |

|   |      | 5.4.1    | receive_only                            | 59 |

|   |      | 5.4.2    | pending_receive_only                    | 62 |

|   |      | 5.4.3    | Discussion                              | 63 |

|   | 5.5  | Long I   | PC                                      | 63 |

|   |      | 5.5.1    | Class & Chiefe and Departient in a last | 64 |

|   |      | 5.5.1    | Clans & Chiefs and Deception: ipc_long  | 04 |

| 6 | Oth  | er Syste | em Calls                                     | 75    |

|---|------|----------|----------------------------------------------|-------|

|   | 6.1  | id_ne    | earest                                       | . 75  |

|   |      | 6.1.1    | Introduction                                 | . 75  |

|   |      | 6.1.2    | id_nearest                                   | . 76  |

|   |      | 6.1.3    | nchief                                       | . 76  |

|   | 6.2  | lthre    | ead_ex_regs                                  | . 79  |

|   |      | 6.2.1    | Introduction                                 | . 79  |

|   |      | 6.2.2    | Prologue                                     | . 79  |

|   |      | 6.2.3    | Thread creation                              | . 79  |

|   |      | 6.2.4    | Exchanging register values                   | . 83  |

|   |      | 6.2.5    | Cleanup: Terminating pending or running IPCs | . 83  |

|   | 6.3  | task     | new                                          | . 87  |

|   | 6.4  | threa    | ad_schedule                                  | . 101 |

|   | 6.5  | threa    | ad_switch                                    | . 101 |

|   | 6.6  | fpage    | e_unmap                                      | . 102 |

| 7 | Oth  | er Stuff | (Provisional)                                | 103   |

|   | 7.1  | Sched    | uling                                        | . 103 |

|   |      | 7.1.1    | make_busy                                    | . 103 |

|   |      | 7.1.2    | ins_busy_list                                | . 104 |

|   |      | 7.1.3    | get_next_thread                              | . 105 |

|   | 7.2  | Interru  | npts                                         | . 105 |

|   | 7.3  | Initiali | sation                                       | . 105 |

|   | 7.4  | Sigma    | Zero                                         | . 105 |

|   | Bibl | iograpł  | Ŋ                                            | 107   |

|   | Inde | dex 109  |                                              |       |

# **List of Code Listings**

| 1.1     | Sample code listing                                                       | 2  |

|---------|---------------------------------------------------------------------------|----|

| 4.1     | TLB refill handler xtlb_refill                                            | 24 |

| 4.2     | STLB miss handler tlb2_miss                                               | 26 |

| 4.3     | General exception handler gen_exc.                                        | 28 |

| 4.4     | The syscall_ret macro                                                     | 30 |

| 4.5     | Exception dispatcher other_excpt, first part.                             | 32 |

| 4.6     | Exception dispatcher other_excpt, second part.                            | 33 |

| 4.7     | General exception return code other_excpt_ret.                            | 33 |

| 4.8     | TLB fault handler exc_tlbs, prologue                                      | 34 |

| 4.9     | TLB fault handler exc_tlbs, main part                                     | 35 |

| 4.10    | TLB fault handler exc_tlbs, long IPC faults.                              | 36 |

| 4.11    | Resumption code after pager IPC: ipc_fault_ret                            | 38 |

| 4.12    | Mapping window TLB misses: window_fault, first part                       | 39 |

| 4.13    | Mapping window TLB misses: window_fault, second part                      | 40 |

| 4.14    | Mapping window TLB misses: window_fault, third part.                      | 41 |

| 4.15    | Mapping window TLB misses: window_fault, final part.                      | 42 |

| 4.16    | Sender-side continuation after receiver-side page fault: window_fault_ret | 43 |

| 4.17    | Error handling code of window_fault_ret.                                  | 44 |

| 4.18    | Coprocessor-unusuable exception handler: exc_cpu, first part              | 44 |

| 4.19    | Coprocessor-unusuable exception handler: exc_cpu, second part             | 45 |

| 4.20    | Coprocessor-unusuable exception handler: exc_cpu, final part.             | 46 |

| 5.1     | Prologue of k_ipc.                                                        | 48 |

| 5.2     | Delivery part of k_ipc.                                                   | 50 |

| 5.3     | The thread_switch_fast macro.                                             | 52 |

| 5.4     | Send-only delivery: send_only_short.                                      | 55 |

| 5.5     | Blocking send code: pending.                                              | 56 |

| <i></i> | proteing send code, perioditiz,                                           |    |

### LIST OF CODE LISTINGS

| 5.6        | Unblocking sender: pending_restart                      | 57       |

|------------|---------------------------------------------------------|----------|

| 5.7        | Determining real destination: to_chief                  | 58       |

| 5.8        | The to_next_thread macro.                               | 59       |

| 5.9        | Prologue of receive_only.                               | 60       |

| 5.10       | Interrupt association part of receive_only              | 61       |

| 5.11       | Epilogue of receive_only.                               | 62       |

| 5.12       | Receiver finds sender ready: pending_receive_only.      | 63       |

| 5.13       | Long IPC code: ipc_long, first part.                    | 64       |

| 5.14       | Long IPC: ipc_long, second part.                        | 65       |

| 5.15       | Prologue of dollong_ipc                                 | 66       |

| 5.16       | Locating the receive fpage in do_long_ipc.              | 67       |

| 5.17       | Processing mappings in do_long_ipc.                     | 68       |

| 5.18       | Processing memory messages in do_long_ipc.              | 69       |

| 5.19       | Processing direct strings in do_long_ipc.               | 70       |

| 5.20       | Processing indirect strings in do_long_ipc, first part. | 71       |

| 5.21       | Processing indirect strings in do_long_ipc, final part  | 72       |

| 6.1        | id_nearest                                              | 76       |

| 6.2        | nchief.                                                 |          |

| 6.3        | Prologue of lthread_ex_regs.                            | 80       |

| 6.4        | Allocation and initialisation of new TCBs.              | 81       |

| 6.5        | Initialisation of new thread's scheduling parameters.   |          |

| 6.6        | Exchanging thread attribute values.                     |          |

| 6.7        | Cancelling pending IPCs.                                |          |

| 6.8        | Target thread state was LOCKS.                          |          |

| 0.8<br>6.9 | Target thread's <i>stacked</i> state was LOCKS.         |          |

|            | Target thread was blocked or ready.                     |          |

|            | task_new (create_thread) part 0.                        | 87       |

|            | task_new (create_thread) part 1                         | 88       |

|            | task_new (create_thread) part 2.                        | 89       |

|            | task_new (create_thread) part 3.                        | 90       |

|            | task_new (create_thread) part 4.                        | 90<br>91 |

|            | -                                                       |          |

|            | task_new (create_thread) part 5                         | 92       |

|            | task_new (create_thread) part 6.                        |          |

| 0.18       | task_new (create_thread) part 7                         | 94       |

### LIST OF CODE LISTINGS

| 6.19 | task_new (create_thread) part 8               |

|------|-----------------------------------------------|

| 6.20 | task_new (create_thread) part 9               |

| 6.21 | task_new (create_thread) part 10              |

| 6.22 | task_new (create_thread) final part           |

| 6.23 | vm_new_as                                     |

| 6.24 | thread_schedule                               |

| 6.25 | thread_switch                                 |

| 7.1  | The code generated by the make_busy macro     |

| 7.2  | The preempt_ret routine                       |

| 7.3  | The code generated by the ins_busy_list macro |

| 7.4  | The scheduler function get_next_thread        |

# **List of Figures**

| 2.1 | The format of R4x00 TLB entries and of the corresponding coprocessor registers | 12 |

|-----|--------------------------------------------------------------------------------|----|

| 2.2 | MIPS R4x00 address space.                                                      | 14 |

| 2.3 | R4x00 status register format.                                                  | 15 |

| 3.1 | Kernel physical memory map.                                                    | 18 |

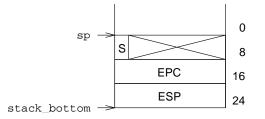

| 4.1 | Exception stack frame                                                          | 29 |

# **List of Tables**

| 2.1 | R4x00 general purpose register set                           | 11  |

|-----|--------------------------------------------------------------|-----|

| 2.2 | Memory cacheability and coherency attributes on the $R4x00.$ | 13  |

| 5.1 | Register usage and naming convention in IPC code.            | 48  |

| 6.1 | Register usage in id_nearest and nchief code                 | 76  |

| 6.2 | Register usage in lthread_ex_regs                            | 79  |

| 6.3 | Register usage in task_create.                               | 87  |

| 6.4 | Register usage in thread_switch                              | 101 |

# **List of Bugs and Restrictions**

| 1  | No granting                                             | 8   |

|----|---------------------------------------------------------|-----|

| 2  | HI/LO not saved                                         | 31  |

| 3  | FPU state incorrectly restored                          | 45  |

| 4  | Priority inversion in send_only_short                   | 55  |

| 5  | Send queue not prioritised                              | 57  |

| 6  | a7 not initialised when ipc_nchief is called            | 58  |

| 7  | Wait-for checks real instead of virtual sender          | 62  |

| 8  | Four fpages only                                        | 68  |

| 9  | Fpage processing terminated too late                    | 68  |

| 10 | Exiting id_nearest may cause fatal TLB miss.            | 78  |

| 11 | ex_regs incorrectly initialises pager and excepter      | 80  |

| 12 | ex_regs return values trashed if terminating IPC        | 84  |

| 13 | Stacked state not reset if in recursive IPC             | 85  |

| 14 | Kernel panics on task version or nesting depth overflow | 89  |

| 15 | Terminating nested IPC trashes v0                       | 104 |

# **Chapter 1**

# Introduction

L4/MIPS is the implementation of the L4 microkernel [Lie93, Lie95] on R4000 series CPUs [R4695]. The R4600/R4700 is an implementations of the MIPS R4x00 architecture [KH92] aimed at embedded applications. The L4/MIPS API is based on the ix86 version of L4 [Lie96a] as of mid-1996 ("Version 2") with a few minor extensions (compatible to "Version 4").

L4/MIPS was designed by Kevin Elphinstone, then a PhD student at UNSW, and Jochen Liedtke, then a researcher at GMD, Germany, in 1995–6. It was mostly implemented by Kevin Elphinstone between mid 1995 and mid 1997. Improvements were since made by Kevin Elphinstone and Alan Au, the latter also a PhD student at UNSW. This document is based on L4/MIPS kernel version 79 [L4M99], which was released in February 1999.

L4/MIPS is now in regular use at UNSW for research and teaching. The Mungi single-address-space operating system [HEV<sup>+</sup>98] has been implemented on top if it, Linux has been ported to it [HHL<sup>+</sup>97], and the kernel is used in teaching *Advanced Operating Systems*.

This report is an attempt to document the internal operations of the kernel, and to shed some light on what "makes it tick" and where it gets its performance from.

# **1.1 Intended Audience**

This document is written to serve two purposes:

• to be used in operating systems teaching.

L4/MIPS has been used as a platform on which students built operating systems in UNSW's COMP9242 *Advanced Operating Systems* course since August 1997. Since 1999 the course took a closer look at microkernel implementation issues, and the first version of this document grew out of that. It is planned to expand the coverage of microkernel internals in the future, based on a more complete version of this document. Arizona State University is also planning to use this report as an aid in teaching an operating systems internals course.

• as an aid to future kernel implementors.

L4 implementations are highly optimised, contain lots of assembler code, and tend to employ plenty of architecture-specific tricks. However, the general structure, and the "course-grain logic" is remarkably similar across platforms. An in-depth study of L4 source code for one particular architecture will therefore provide a good guide on how to approach a re-implementation on a different platform.

| 0    | mtc0                              | t0, C0_STATUS         |  |  |  |

|------|-----------------------------------|-----------------------|--|--|--|

| 1    | dli                               | аб, О                 |  |  |  |

| 2    | j                                 | k_ipc                 |  |  |  |

| 3    | move                              | a5, a4                |  |  |  |

| 4 3: | lui                               | a0, KERNEL_BASE       |  |  |  |

| 5    | ld                                | a0, K_GPT_POINTER(a0) |  |  |  |

| 6    | move                              | al, s3                |  |  |  |

| 7    | and                               | a2, a0, a4            |  |  |  |

|      | Listing 1.1: Sample code listing. |                       |  |  |  |

In both of these aspects, this report aspires to follow the example of the famous *Lions Book* [Lio77, Lio96], also from UNSW, without pretending to rival the Commentary's impact and significance.

This report, as well as the source code it describes, is available from the UNSW L4 web site.<sup>1</sup> That site also contains the latest releases of L4 for various architectures, associated documentations and forms to register for mailing lists with L4-related announcements. Feedback on this report is highly welcomed and should be directed to 14.inside@cse.unsw.edu.au.

## 1.2 Why MIPS?

Why did we go through the trouble of writing this report on L4 for the MIPS architecture, when it is more than doubtful whether this architecture has any future?

The answer comes in two parts:

- 1. For the purposes stated in the previous section, it doesn't matter much. For teaching microkernel internals the specific platform it is of little relevance. Teaching use is also supported by a R4x00 simulator which can run L4, and thus provides independence from actually available hardware. *Real Soon Now...* Similarly, as an aid for future kernel builders the MIPS source as relevant as any other.

- 2. The MIPS implementation is very clean, certainly the most readable one available at this time. It is about half assembler, half C, but even the assembler code is mostly very readable and not too hard to understand. The same cannot be said about other implementations.

And, of course, it helped that the code was developed locally, and as a result a number of people were familiar with at least parts of it, and could therefore answer questions.

## **1.3** Conventions

Most of this report consists of verbatim source code listings and associated annotations. Source code is shown in displays called "Listings", such as the example Listing 1.1. Wherever feasible, listings and annotations appear on the same or on opposite pages. To make this possible the listings have been condensed as much as possible, by eliminating empty lines, instrumentation code, compiler directives, and even the (rare) comments.

The listing shows the format of MIPS assembler instructions. In general an instruction consists of an opcode and up to three operands. The first operand is **always** the destination register. The second operand is normally the source register. The third operand is a second input to the instruction, and can be a register or an immediate value. If a three operand instruction is written with two operands only, then the first operand represents both source and destination registers. In the case of a store instruction, the first ("destination") operand is the register to be saved.

<sup>&</sup>lt;sup>1</sup>The URL of the UNSW L4 web site is http://www.cse.unsw.edu.au/~disy/L4/.

Assemblers on RISC architectures such as the MIPS generally do a good job of scheduling instructions into load and branch delay slots. For some of the tightest system code, however, the "DIY" approach is still better. Consequently, much of the critical kernel code is covered by .set noreorder directives, which prevent the assembler from changing the order of instructions. To avoid cluttering up the listings with these directives, any code for which a noreorder directives is in force, is shown in the listings with **bold** line numbers. In Listing 1.1 this is the case for Lines 0–3. Here, Line 3 is in Line 2's branch delay slot; logically Line 3 precedes Line 2.

In the reminder of this document we will make an attempt to point out (often non-obvious) implementation decisions/simplifications as follows:

Implementation choice: This highlights an implementation choice.

Any known bugs in the exhibited code will be indicated like this:

**Bug/Restriction 0: Sample bug.**

This is how bugs are shown.

A bug is code which causes the kernel to operate in a way that is inconsistent with the specification. This includes unimplemented features.

There are other shortcomings of the implementation, for example affecting efficiency, which are not bugs as they do not affect correctness. These are highlighted like this:

Implementation criticism: This criticises the implementation.

Note that these shortcomings are often "quick-and-dirty hacks" which were put in place to get things going, and were never removed because there was not enough pressure for having them removed. Much of this is actually nitpicking. The frequent use of *implementation criticisms* should not create an impression that the L4/MIPS implementation is highly deficient. In fact, it's great code!

Text in **bold italics** indicates something that needs fixing up in this document.

## 1.4 Structure

Chapter 2 provides background information required for the understanding of the remainder of the report. There are two parts to this: L4 in general, and the MIPS R4x00 architecture. The description of L4 is kept extremely brief, for the simple reason that we consider it essential to have the L4 Reference Manual [EHL99] handy when reading this document. Hence it makes little sense to repeat much of what is said in the Reference. The R4x00 architecture description is much more detailed, and, hopefully, sufficient for the understanding of the code.

Chapter 3 provides the introduction to the L4 code. It contains a short overview of the structure of the source code, and then presents and explains the main kernel data structures and their use.

The remaining chapters consist mostly of annotated source code listings. Chapter 4 presents the exception handling code, Chapter 5 the IPC code, and Chapter 6 the code implementing the other system calls.

# **Chapter 2**

# Background

This chapter provides some background information on L4 and the MIPS R4x00 architecture.

## 2.1 L4 Overview

Here we give a quick summary of the main features of L4. However, the reminder of this document assumes a fair amount of familiarity with L4 and its API, well beyond what is presented in this section. The reader is advised to have the L4/MIPS reference manual [EHL99] handy when reading on. A practical guide to using L4 and its various features is provided by the User Manual [AH98].

## 2.1.1 L4 philosophy

The design of the L4 microkernel is based on the principle of minimality: A feature should be in the microkernel if and only if security requires that the feature be implemented in privileged mode. The term "kernel" refers to code which executes in the hardware's privileged mode. This implies, for example, that device drivers should not be part of the kernel. While drivers have access to physical memory, and are thus part of the system's *trusted computing base*, security of the system does not depend on running device drivers in privileged mode, only on protecting the drivers from interference by untrusted code [Lie96b].

Another important principle is that *it should be possible to implement arbitrary systems on top of the microkernel*. Together with the minimality principle this leads to a requirement for a small number of powerful and orthogonal abstractions, and for a strictly *policy-free* kernel.

It is important to note that Liedtke does not claim that the present versions of L4 fully satisfies these requirements. In fact, the L4 API is still developing in an attempt to better meet its design goals.

Interestingly, efficiency is not a primary design principle. However, all features have been carefully analysed and were only included into the interface if it was clear that they could be implemented efficiently. Smallness itself is a very good basis for efficiency. The performance of modern computer systems is critically dependent on maintaining high hit rates in the CPU caches, and the kernel's cache footprint has a dramatic impact on performance [Lie95]. Small is certainly beautiful in the world of microkernels.

But that is not the full story. A careful implementation which makes the best possible use of hardware features is a major factor for kernel efficiency. A careful design of kernel data structures and algorithms is, maybe, the most important factor in making a kernel fast.

#### 2.1.2 L4 abstractions

L4's main abstractions are:

- **Threads** represent program execution. The CPU is multiplexed between threads, each of which has some context, including its view of hardware registers. Each thread is uniquely identified via a *thread ID* (TID).

- Address spaces form the basis of protection. A thread can access data which are mapped into its address space. Address spaces are constructed by **mapping** sections of other address spaces.

- **Inter-process communication,** based on synchronous message-passing, provides for a controlled way to communicate between address spaces. L4 IPC also serves as a **synchronisation** primitive between threads.

#### Address spaces and tasks

Each thread belongs to a *task*. There is a one-to-one correspondence between tasks and address spaces.<sup>1</sup> Creating and deleting tasks implies creating and deleting address spaces. This is done via the task\_new system call.

Logically, the number of tasks is fixed (2048 in L4/MIPS Version 79). Hence tasks are strictly speaking not created or destroyed, but their state is changed from *inactive* to *active* or vice versa. Inactive tasks consume (almost) no resources.

Creation (activation) of a task implies creation of a fixed-size set of threads (128 in L4/MIPS Version 79). These are numbered consecutively, starting at zero. All of a task's threads, except local thread zero ("Ithread zero", or  $l_0$ ) are logically created executing an idle loop (but without consuming any resources).  $L_0$  is immediately active and starts execution at a start address passed to the task\_create syscall.

A new task's address space is initially empty, and can only be populated by mapping-in parts of other address spaces. Consequently,  $l_0$ , when it begins execution, will immediately trigger a page fault when attempting to fetch its first instruction. It is the responsibility of its *page fault handler* (pager) to provide a mapping for that page.

A task has a number of attributes:

- **chief** or owner. For an active task, this is the task to which the thread belongs which has activated the task. Only a task's chief can activate or deactivate a task. As a side effect of deactivation, a task can be *donated* to a new chief. Task IDs are effectively capabilities conferring rights over tasks.

- **maximum controlled priority** (MCP). This is the upper limit to which a thread of the task can influence the priority of other threads (including its own). The MCP is *not* a priority. A task's MCP is specified at the time the task is activated (and cannot be higher that the MCP of its chief).

Further attributes are (explicitly) specified when a task is activated, but they are attributes of  $l_0$  rather than the task's.

#### Threads

Threads are the active entities in L4, they are the source and destination of IPC messages. Threads have the following attributes:

task: the task (and thus address space) to which the thread belongs;

**pager:** the thread responsible for handling this thread's page faults. On a page fault the kernel will send a page fault IPC message to the pager, and the pager is expected to reply with a message containing a mapping for the faulting page;

<sup>&</sup>lt;sup>1</sup>For that reason, tasks are not a primitive concept, and it can be argued that the task concept is redundant. Not surprisingly, it is due for removal in a future version of the L4 specification. But for the time being tasks are an essential component of L4.

- **excepter** (exception handler)<sup>2</sup>: the thread responsible for handling this thread's exceptions. On an exception, the kernel will send an exception IPC message to the excepter. It is then up to the excepter to implement whatever policy it chooses for handling exceptions;

- internal preempter: not implemented on L4/MIPS Version 79.

- external preempter: not implemented on L4/MIPS Version 79.

- **scheduling priority:** determines when a thread will be scheduled by the kernel. L4 implements hard priorities (values 0–255): The scheduler will select the highest-priority runnable thread, using round-robing within priority levels;

- **time-slice length:** the value a thread's *current time-slice length* will be set to by the scheduler to the value of the thread's time-slice length when selecting the thread to run;

- **current priority** determines preemptability of a thread. A thread may be preempted by another thread whose priority is higher than the presently running thread's current priority. The current priority of a thread may be set at scheduling time, or by time-slice donation;

- **current time-slice length** determines the time a thread is allowed to run until preempted (unless a higher-priority thread becomes runnable). The current time slice is obtained either by scheduling or by time-slice donation.

A thread's stack pointer, program counter, excepter, internal preempter and pager can be obtained and manipulated via the lthread\_ex\_regs syscall. This call can be performed by any thread on another thread belonging to the same task. It is the means by which new threads can, for example, be activated (taken away from their logical idle loops to more productive endeavours), or moved out of harm's way (by forcing them to block on an IPC which will never succeed). An excepter can use this system call to redirect a thread to some code which saves its user state, and later restores it.

A thread's scheduling parameters (time-slice length, scheduling priority and external preempter) can be obtained and manipulated via the thread\_schedule system call. A thread may only perform such an operation on another thread whose priority does not exceed the caller's MCP.

Time-slice donation can happen in one of two ways:

- explicitly via the thread\_switch system call. This call donates the remainder of the caller's current time slice to a specific thread. If that thread does not exist, or is blocked, the system call becomes a "yield" operation, i.e., the caller forfeits the remainder of its present time slice, and the scheduler is invoked to select another thread to run with a new time slice;

- implicitly via IPC. IPC operations are often accompanied by a context switch from the sender to the receiver, in which case the sender's current time slice is implicitly donated to the receiver.

#### **IPC and mapping**

IPC is performed via the ipc system call. All L4 IPC is blocking — a message transfer only takes place when both he sender and receiver are ready for it. This implies a synchronisation between the communication partners. It also means that messages only have to copied once, no buffering of messages in the kernel is required.

An IPC system call specifies an optional send operation and an optional receive operation. This reduces the number of system calls required in many frequent situations, such as RCP (or "call": send message and wait for answer) or server-style reply-and-wait-for-next-request.

To prevent indefinite blocking, timeouts are specified for each IPC. An IPC system call has four timeout arguments:

$<sup>^{2}</sup>$ Excepters are a MIPS-specific feature. Other L4 implementations handle exceptions differently, e.g., by mirroring hardware exceptions [Lie96a].

- **send timeout:** the maximum amount of time the caller is willing to block on the send operation (if any), measured from the time of trapping into the kernel until the partner becomes ready to receive;

- **receive timeout:** the maximum amount of time the caller is willing to block on the receive operation (if any), measured from the time of concluding the send operation (if any, time of trapping into the kernel otherwise) until the partner becomes ready to send (if any);

- **send page-fault timeout:** the timeout value to use for the send and receive parts of any page-fault IPC that may be required for the partner's address space during delivery of the send message (if any);

- **receive page-fault timeout:** the timeout value to use for the send and receive parts of any page-fault IPC that may be required for the partner's address space during delivery of the receive message.

Timeouts may be specified as zero (poll partner) or infinity (block indefinitely).

IPC messages may transfer data in two ways:

By value: data is copied from sender to receiver. By-value data is supported in three forms:

- registers up to 64 bytes (on MIPS R4x00) may be transferred in registers. This is in many cases a zero-copy operation, and is therefore highly efficient;

- direct strings a message buffer contains data which is copied by the kernel into the receiver's message buffer. Direct strings must be word aligned;

- indirect strings the message buffer contains an arbitrary number of pointers to data buffers, which are copied by the kernel into the corresponding buffers pointed to by the receiver's message buffer.

Direct and indirect strings are copied only once, from the sender's address space directly into the receiver's address space.

- **By reference:** the sender can designate a range of pages in its address space, which get mapped into the receiver's address space during the IPC. The receiver must specify a window where the pages may be mapped. By-reference data transfer can happen in two ways:

- mapping sender and receiver share the mappings after a successful IPC map operations. The sender may revoke ("flush") the mappings at any time via a fpage\_unmap system call;

- granting the pages are implicitly unmapped from the sender's address space, who loses any access or control over them. This operation is not reversible by the sender.

#### **Bug/Restriction 1: No granting.**

Granting is not implemented in L4/MIPS Version 79.

Address-space regions are specified via an abstraction of variable size pages, called a *flexpage* or *fpage*. An fpage is a section of virtual address space whose size is a power-of-two multiple of the smallest page size supported by the hardware, and must be aligned to its size. A single IPC operation may specify several fpages for mapping. The receiver specifies its window via a single *receive fpage*.

#### **Clans and chiefs**

Clans and chiefs are a mechanism allowing control over information flow. Tasks, via the relation to their chiefs, form a hierarchy. All tasks which are owned by the same chief form that chief's *clan*. A thread can send an IPC message only to

- a thread belonging to its chief task,

- a thread belonging to a task which is part of the same clan as the sender's task, or

- a thread belonging to a task which is (directly) part of the sender's task's clan.

All other IPC is redirected to the nearest chief. The nearest chief is

- the sender's chief, in the case of a message directed to a task not directly or indirectly inside the caller's clan,

- otherwise the task inside the caller's clan whose clan directly or indirectly contains the intended receiver.

The id\_nearest syscall returns the ID of the "nearest" chief which would be the actual receiver of such an IPC message.

For the purpose of IPC redirection, the chief is thread  $l_0$  of the chief task. The receiving chief is informed, via a bit in the IPC syscall's result word, that the message was redirected, and is also informed of the intended receiver. The chief has then the option of forwarding the message to the intended receiver (or the next nearest chief along the way). In order to maintain RPC semantics, the chief can send on the message using *deceiving* IPC. A deceiving IPC specifies a *virtual sender*, different from the actual sender, which will be returned to the receiver as the originator of the message. The receiver is alerted to the deceit via a bit in the IPC result code. The kernel allows a deceit only if it is *direction preserving*. Loosely speaking, a deceit is direction preserving if the actual sender is within the sequence of chiefs a message from the virtual sender to the receiver had to take.

#### System calls

The above mentioned seven syscalls, ipc, fpage\_unmap, task\_new, id\_nearest, lthread\_ex\_regs, thread\_switch, and thread\_schedule comprise the full set of L4 system calls.

#### Interrupts

Interrupts are modelled as threads sending empty messages spontaneously. Each interrupt has a TID, and a single user thread can be *associated* with each interrupt, thus becoming a handler for that interrupt. If an interrupt has an associated hander, the kernel will convert an occurance of that interrupt into a message to the handler thread.

#### **Initial address space**

Mapping IPC (particularly in combination with pagers) can be used to build up an address space from others, but somewhere the recursion must bottom out. For that reason, L4 provides a (somewhat magical) *initial address space* called  $\sigma_0$ . It is created at system initialisation time with an address space containing a one-to-one image of physical memory (other than the parts reserved for kernel use).

L4's boot protocol also contains a notion of *initial servers*, which are started up by  $\sigma_0$  once the kernel has booted.  $\sigma_0$  is the pager of all initial servers.  $\sigma_0$  will satisfy any faults within the range of its own initialised address space by mapping the corresponding page, and ignores faults outside its valid address space range (leading to the server becoming blocked). Pages are only mapped to one initial server, thus ensuring protection. Special protocols exist to request mappings for device regions.

#### **Initial tasks**

Tasks other than  $\sigma_0$  and initial servers remain inactive and owner-less, until someone claims them. A task is claimed by performing a deactivating form of the task\_new syscall, specifying oneself as the new chief.

# 2.2 Relevant Features of the MIPS R4x00 Processor

### 2.2.1 Target systems

The kernel code described in this document is for a uniprocessor R4600/R4700 system. There are a number of minor differences between various processors of the R4x00 family. For the purpose of kernel code, no significant differences exist between the R4600 and the R4700, and we will use the term "R4600" to represent both processor models. Similarly, the differences between the R4000 [Hei93] and the R4400 are very minimal, and we will use the term "R4000" to refer to both. For most of our purposes there is no need to distinguish between processors of the family, and we will use the generic term "R4x00" to refer to any of them.

Other related processors, such as the R5000 and the R10000 will probably run L4/MIPS without major changes. Particularly the R5000's MMU seems to be similar enough to the R4x00 to allow the code to run virtually unchanged. However, the R5000 and R10000 are multi-issue CPUs, and no attempt has been made in the kernel to schedule instructions for multiple issue.

### 2.2.2 R4x00 general features

The R4x00 processor family is a 64-bit architecture which supports full compatibility with the 32-bit MIPS CPUs R2000 and R3000. This is achieved by supporting a 32-bit execution mode.

Implementation choice: 32-bit execution is not supported by L4/MIPS and is therefore not covered here.

The processor is a RISC design which issues one instruction per clock cycle. The only addressing mode is base-register plus 16-bit, signed immediate offset. Most instructions execute in a single cycle.

On the R4600, which has a 5 stage pipeline, jump and branch instructions have an additional one cycle delay, and load instructions also have a one cycle delay. On the R4000, which has a 8 stage pipeline, the branch delay is 3 cycles and the load delay 2 cycles. On all R4x00 processors, the instruction immediately following a jump or branch (the *load/branch delay slot*) is always executed while the target instruction is being fetched.

The pipeline will stall in the case of an attempted access to the result of a load before it is available. Hence scheduling instructions in a load delay slot will hide the delay but is not necessary for correct execution.

Multiplication and division instructions require between 10 and 133 cycles to complete. They leave their results in two special registers, HI and LO, and the pipeline stalls until the result is available.

The processor can be configured to operate little-endian or big-endian, and can also switch endianess between user and kernel mode.

Implementation choice: L4/MIPS uses big-endian only.

MIPS instructions support four data types: *byte* (b, 8 bits), *half word* (h, 16 bits), *word* (w, 32 bits), and *double word*, or *dword* (d, 64 bits). Load and store instructions support all four sizes, but data must be aligned to size.<sup>3</sup>

The processor features 32 general-purpose registers, r0–r31, all 64 bits wide. Assembler programs use symbolic names based on compilers' usage conventions. These are summarised in Table 2.1. Register r0 reads as zero and ignores writes. Register r31 is implicitly used by the *jump-and-link* (jal) instruction.

The following register conventions are important to observe when writing kernel code:

• The AT register is used by the assembler to store intermediate results of pseudo-instruction macros. If used for any other purpose the appropriate instructions must be surrounded by .set at and .set noat directives to prevent interference from assembler macros.

$<sup>^{3}</sup>$ A special instruction is lui, which loads the specified immediate value into the second-least significant byte, zeroing the least significant byte, and sign extending.

• The k0 and k1 registers are used as temporary registers by the kernel's exception handlers. As various exceptions can occur in kernel mode, these must not be used except in situations where it is certain that no exceptions can occur. This means that interrupts must be disabled. It also means that no mapped addresses may be used, or it must be ensured that any virtual pages used are already mapped.

| register | menmonic | convention                             |  |

|----------|----------|----------------------------------------|--|

| r0       | zero     | always zero                            |  |

| rl       | AT       | assembler temporary                    |  |

| r2-r3    | v0-v1    | integer function results               |  |

| r4-r11   | a0–a7    | first eight integer function arguments |  |

| r12-r15  | t0-t3    | temporary (callee saved)               |  |

| r16-r23  | s0-s7    | caller-saved                           |  |

| r24–r25  | t8-t9    | temporary (callee saved)               |  |

| r26-r27  | k0-k1    | kernel reserved                        |  |

| r28      | gp       | global (data segment) pointer          |  |

| r29      | sp       | stack pointer                          |  |

| r30      | s8/fp    | frame pointer (caller saved)           |  |

| r31      | ra       | return address                         |  |

Table 2.1: R4x00 general purpose register set, mnemonic names and usage conventions (for 64-bit API).

In addition to the general-purpose registers, the processor has three special purpose registers:

- the program counter register, PC;

- the multiplication and division result registers, HI and LO. These registers can only be accessed via special instructions, mfhi, mflo, mthi, and mtlo. The first two read the and the last two write the respective register.

MIPS assembly code general uses the format

#### op dst, src, trgt

where *dst* is the register receiving the result of the operation, and *src*, *trgt* are the operands. If only two registers are specified, the *src* is taken to be the same as *dst*. One exception to the general scheme is the *store* instructions, where *dst* designates the register whose contents are to be stored to memory.

The processor has a number of *co-processors*, which have their own register sets. Co-processor zero (CP0) is the *system coprocessor*, which contains the the memory-management unit (MMU) as well as the status register and a number of other registers relevant to exception handling. Co-processor 1 (CP1) is the optional floating-point unit (FPU). Further co-processors are optional.

The processor has separate primary instruction and data caches on chip and accessible in parallel. For the R4600 these are both 16kB big, are two-way associative and feature a 32B line size (8 instructions in the case of the I-cache). Best case cache miss penalty on a system with 80ns DRAM and no secondary cache is 13–14 cycles for the I-cache and 15–16 cycles for the D-cache.

#### 2.2.3 Memory management unit

The MMU is part of the CP0. Virtual addresses are translated in one of two ways:

- mapped VM addresses are translated by the translation lookaside buffer (TLB),

- unmapped VM addresses are translated by masking out the most significant bits of the address.

Which mechanism is used depends on the address, as explained in Section 2.2.4 below. Here we summarise the translation of mapped addresses.

The R4x00 TLB is fully associative and holds 48 entries, each mapping a pair of 4kB pages. TLB entries are *tagged* with an *address-space identifier* (ASID), an 8-bit number. The TLB is *software loaded*, a translation miss raises a TLB miss exception. The miss handler uses the tlbwi or tlbwr instruction to load a TLB entry. The former instruction loads the entry indicated by the C0\_INDEX register, while for the latter instruction the target entry is indicated by the C0\_RANDOM register. The C0\_RANDOM register is decremented at each instruction execution. The C0\_WIRED register can be used to define a lower limit of C0\_RANDOM register values, and is used to protect some TLB entries from "random" replacement.

**Implementation choice:** L4/MIPS only uses random replacement (except to update an existing entry) and does not wire down any entries.

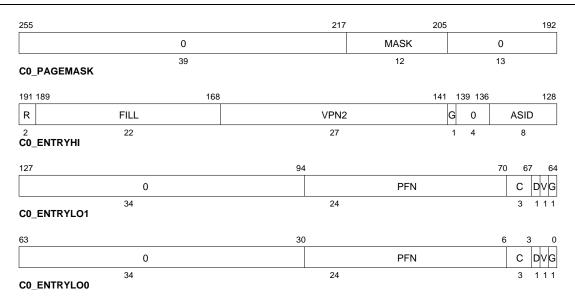

Figure 2.1: The format of R4x00 TLB entries and of the corresponding coprocessor registers.

Figure 2.1 shows the format of a TLB entry and the corresponding coprocessor registers from which the tlbwi or tlbwr load the entry. There is one minor difference between the format of a TLB entry and the coprocessor registers: The G (global) bit shown in the EntryHi word exists in the TLB entry but must be zero in the CO\_ENTRYHI register. Conversely, the G bit in the EntryLo words is settable in the CO\_ENTRYLO0, CO\_ENTRYLO1 registers but is zero in the TLB entry. When a TLB entry is loaded its G bit is set to the logical AND of the G bits in CO\_ENTRYLO0 and CO\_ENTRYLO1. The ASID field of CO\_ENTRYHI is also used during address translation to match the ASID value of a TLB entry.

The meaning of the fields are:

MASK: Defines the page size. Valid page sizes vary from 4kB (MASK=0) to 16MB (MASK=0xfff) in powers of 4.

Implementation criticism: L4/MIPS presently only uses the smallest page size, 4kB.

- **R:** Indicates that the mapping is valid in kernel mode only (R=11), in kernel or supervisor mode (R=01) or always (R=00). During address translation the R field is matched against bits 63:62 of the virtual address (except for CKSEG addresses) which ensures that the processor is in the reight mode.

- FILL: In CO\_ENTRYHI must have all bits equal to the MSB of R. Zero in the TLB entry.

- **VPN2:** Virtual page number (in units of the page size defined by the MASK field) divided by two.

- G: If set the ASID is ignored when the TLB is looked up.

ASID: Used to distinguish mapping for the same page belonging to different processes. If the G is unset on a

TLB entry, it will only match if the ASID field matches the ASID value presently set in the CO\_ENTRYHI register. If the TLB entry's G bit is set the ASID is ignored.

**PFN:** Physical frame number (in units of the page size defined by the MASK field).

**C:** Cacheability and cache coherency setting (see Table 2.2).

**D:** Dirty bit — iff set (and the V bit is set also) the page is writable.

v: Valid bit — iff unset a TLBL or TLBS exception occurs when accessing the page mappede by this entry.

| С  | Cacheability and coherency                                | XKPHYS starting address |

|----|-----------------------------------------------------------|-------------------------|

| 0† | Cacheable, non-coherent, write-through, no write allocate | 8000 0000 0000 0000     |

| 1† | Cacheable, non-coherent, write-through, write allocate    | 8800 0000 0000 0000     |

| 2  | Uncached                                                  | 9000 0000 0000 0000     |

| 3  | Cacheable, noncoherent, write back                        | 9800 0000 0000 0000     |

| 4‡ | Cacheable, coherent exclusive                             | A000 0000 0000 0000     |

| 5‡ | Cacheable, coherent exclusive on write                    | A800 0000 0000 0000     |

| 6‡ | Cacheable, coherent update on write                       | в000 0000 0000 0000     |

| 7  | Reserved                                                  | B800 0000 0000 0000     |

Table 2.2: Memory cacheability and coherency attributes on the R4x00. "C" represents the cacheability field of a TLB entry (bits 5:3 of EntryLo) for mapped accesses, or the K0 field (bits 2:0) of the C0\_CONFIG register, or bits 61:59 of a XKPHYS address for unmapped accesses. Attributes marked † are R4600 only and are unavailable ("reserved") on the R4000. Attributes marked ‡ are R4000 only and are unavailable ("reserved") on the R4600/R4700.

## 2.2.4 Address space layout

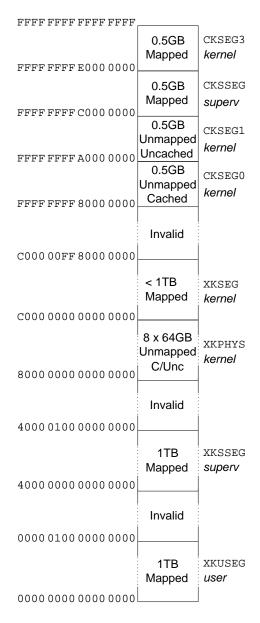

The MIPS R4x00 features a 64-bit address space. The processor can run in three different modes: *user*, *supervisor* and *kernel*. In each of these modes some regions of the address space are accessible while others lead to addressing exceptions. The valid address range in supervisor mode is a subset of the user mode address range, and the kernel address range is a superset of the supervisor address range. Figure 2.2 shows the address map, indicating for each address-space region the minimum privilege (kernel, supervisor or user) required.

As the figure shows, the MIPS' virtual address range is 1TB (40 bits). Address-space regions denoted as *mapped* are translated by the TLB, whereas regions denoted as *unmapped* are translated by masking out the most significant bits of the address.

The processor supports up to 64GB of physical memory, all of which can be addressed unmapped via the various XKPHYS segments. When using XKPHYS addresses, address bits 61:59 are interpreted as the *cacheability* bits. Their interpretation is the same as the corresponding bits in a TLB entry (see Figure 2.2.3). Table 2.2 summarises cacheability and coherency attributes selected by bits 61:59 of a XKPHYS address.

The CKSEG regions (top 2GB of the address space) are called *compatibility spaces*, as they correspond, via sign extension of the address, to kernel and supervisor regions in 32-bit mode.

**Implementation choice:** L4/MIPS does not make use of supervisor mode. The supervisor address space XKSSEG is used, but only as another kernel mapped area (for temporary mappings). Supervisor mode does not provide sufficient privilege to be useful inside the kernel. The design of L4 does not seem to make it necessary to use supervisor privilege outside the kernel.

Figure 2.2: MIPS R4x00 address space.

**Implementation choice:** L4/MIPS only uses the compatibility spaces CKSEG0, CKSEG1 in kernel mode. The reason is that these addresses allow the kernel to use 32-bit address constants, which are faster to load than 64-bit constants. In some cases, in particular, page tables, pointers are also stored in 32-bit form, resulting in more compact data structures. Furthermore, 0.5GB is more than enough memory for kernel use.

Note, however, that the kernel presently only supports 0.5GB as the maximum RAM size. Addressing based on CKSEG0, CKSEG1 means that on a machine with more than 0.5GB of RAM the kernel's dynamic memory pool could no longer reside at the high end of physical memory. The necessary changes to the kernel's startup code would be straightforward.

One drawback of the use of CKSEG0 for unmapped cached memory accesses is that there is no control over the cache coherency protocol via the address. This is not an issue on the R4600/R4700, which does not offer a choice of coherency protocols. On other processors the cacheability of CKSEG0 accesses is defined via the K0 field (bits

2:0) of the *config register* CO\_CONFIG.

#### 2.2.5 Exception processing

*Exceptions* are events which disrupt the normal flow of instruction execution. On the R4x00 this includes the synchronous events of TLB miss, arithmetic overflow and system calls as well as asynchronous interrupts.

When an exception occurs, the CPU enters kernel mode, saves some context in CPO registers and jumps to the appropriate exception handler. The architecture defines four different exception handlers:

TLB at PA 0x000: Used during 32-bit execution for primary TLB refill exceptions.

**Implementation choice:** The 32-bit TLB miss handler is not used by L4.

XTLB at PA 0x080: Used during 64-bit execution for primary TLB refill exceptions.

CACHE at PA 0x100: Used for cache errors.

Implementation choice: L4/MIPS Version 79 handles cache errors by panicking.

GENERAL PA 0x180: Used for all other exceptions (overflow, system call, interrupt, or nested TLB miss).

Exception handlers are addressed via CKSEG0 during normal operation, except cache errors which use CKSEG1 (for uncached access). During boot time the exception vector base address is shifted up to 0xfff ffff bfc0 0200 (a ROM address), but this is only of relevance when writing ROM monitors.

The relevant CP0 registers are:

**CO\_BADVADDR:** Contains the virtual address causing a TLB or cache exception.

CO\_STATUS: Contains the processor status, see below.

- **C0\_CAUSE:** Contains, among others, a field indicating the cause of the exception and a mask indicating pending interrupts.

- **CO\_EPC:** Contains the saved PC value during exception processing. The eret instruction will reload the PC from this register, if it finds the C\_STATUS.EXL bit set and the C\_STATUS.ERL bit unset.

- **CO\_ErrPC:** Contains the saved PC value during error processing. The eret instruction will reload the PC from this register, if it finds the C\_STATUS.ERL bit set.

In addition there is a CO\_COUNT register which is decremented on every second clock cycle, and the CO\_COMPARE register, which triggers a timer interrupt when it matches the contents of the CO\_COUNT register.

| 31 | 28 27 26 25 |     |    |    | 16 8 |    |    | 6  | 5  | 5 3 | 2               | 1   | 0  |

|----|-------------|-----|----|----|------|----|----|----|----|-----|-----------------|-----|----|

| CU | RF          | > F | FR | RE | DS   | IM | κх | sx | υx | KSU | E <sub>RL</sub> | ΕxL | IE |

| 4  | 1           |     | 1  | 1  | 9    | 8  | 1  | 1  | 1  | 2   | 1               | 1   | 1  |

Figure 2.3: R4x00 status register format.

Figure 2.3 shows the contents of the status register, CO\_STATUS. The relevant fields are:

**IM:** Interrupt mask; a bit, if set, enables the corresponding interrupt, providing that the IE bit is set.

KX, SX, UX: If set turns on 64-bit addressing in kernel, supervisor and user modes, respectively.

- KSU: Processor mode values of 00, 01, 10 for kernel, supervisor and user mode, respectively.

- **ERL:** Error level if set, the CPU is executing in *error mode*, which implies kernel mode irrespective of the setting of the KSU field.

- **EXL:** Exception level if set, the CPU is executing in *exception mode*, which implies kernel mode irrespective of the setting of the KSU field.

- **IE:** Interrupt enable if set, interrupts are enabled or disabled according to the setting of IM; if unset, interrupts are disabled irrespective of the setting of IM.

# **Chapter 3**

# L4/MIPS Organisation and Data Structures

# 3.1 L4/MIPS Source Structure

The directory structure of the L4/MIPS distribution is relatively simple:

| example/      | a simple example program                                     |  |  |  |  |  |  |  |

|---------------|--------------------------------------------------------------|--|--|--|--|--|--|--|

| doc/          | Ref man, User man, C inferface man pages                     |  |  |  |  |  |  |  |

| src/          | source tree                                                  |  |  |  |  |  |  |  |

| Makefile.conf | master configuration file                                    |  |  |  |  |  |  |  |

| include/      | header files                                                 |  |  |  |  |  |  |  |

| *.h           | rudimentary C library                                        |  |  |  |  |  |  |  |

| kernel/       | kernel-internal header files                                 |  |  |  |  |  |  |  |

| 14/           | C bindings for L4 syscalls                                   |  |  |  |  |  |  |  |

| lib/          | rudimentary C library                                        |  |  |  |  |  |  |  |

| tools/dit     | Boot file builder                                            |  |  |  |  |  |  |  |

| kernel/       | kernel source                                                |  |  |  |  |  |  |  |

| vm/*/         | various versions of page table code                          |  |  |  |  |  |  |  |

| drivers/      | user-level device drivers (shouldn't be in kernel directory) |  |  |  |  |  |  |  |

| indy/         | Indy-specific kernel code                                    |  |  |  |  |  |  |  |

| p4000i/       | code for Algorithmics board                                  |  |  |  |  |  |  |  |

| u4600/        | code for UNSW R4700 board                                    |  |  |  |  |  |  |  |

| libkern/      | minimal libraries for kernel code                            |  |  |  |  |  |  |  |

| test/         | a number of test programs                                    |  |  |  |  |  |  |  |

Most directories contain a Makefile which contains generic rules and include src/Makefile.conf for parameterisation.

In the reminder of this document, unless there is an explicit statement to the contrary, we will denote file path names relative to the src/ directory.

Two header files should be mentioned at this stage: include/regdef.h defines the mnemonic register names. include/r4kc0.h defines architecture-dependent constants defining the address-space layout of Figure 3.1, the exception vectors, CP0 register names and status, cause and TLB register fields. It also defines constants for setting the caching C field and cache instructions.

## 3.2 Kernel Data Structures

#### 3.2.1 Kernel memory allocation

The kernel is loaded across an ethernet interface by the resident boot monitor, PMON. The boot image is built from the kernel executable (in ELF format) via a tool called DIT. The kernel must be linked to start at virtual memory address 0xffff ffff 8005 0000, the CKSEG0 address corresponding to physical address 0x50000. (This is for the P4000i and U4600 systems, on the Indy the addresses are shifted but the layout is the same.) This address is defined as Makefile.conf:LINKADDR.

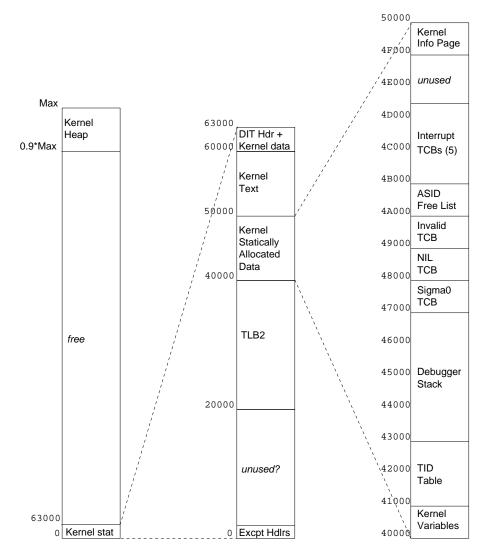

Figure 3.1: Kernel physical memory map.

At boot time the kernel sets up physical memory as shown in Figure 3.1. The region from 0x1000-0x20000 (124kB) seems presently unused. Possibly this is used by the resident boot monitor on either the U4600 or the Indy.

**Implementation criticism:** There is to be no reason why this memory is not used once L4 has booted up. It should be added to the kernel's memory pool.

The region marked as "TLB2" is used for the software TLB, it supports an STLB of up to 128kB.

**Implementation criticism:** Ideally, the STLB size should be determined as a function of physical memory size. This would imply allocating it at a dynamically determined location, but that could be done without slowing down the TLB miss handler.

The memory layout is defined by constants in include/kernel.h.

### 3.2.2 Miscellaneous kernel data: kernel\_vars

Page 0x40 contains a structure, called kernel\_vars, defined in include/kernel/kernel.h. It contains global kernel data, mostly simple types. It also contains the jump tables for the system call despatcher and general exception handler, and the array of pointers to the ready queues for each of the 256 scheduling priorities. Its fields are (somewhat out of order for the purpose of grouping related ones):

**stack\_bottom:** the kernel stack for the current thread (top of the current TCB);

- **s0\_save-s4\_save:** place for exception handlers to save s0-s4 as long as no kernel stack is set up;

- soon\_wakeup\_list, wakeup\_list, late\_wakeup\_list: pointer to the heads of the three wakeup lists of threads blocked with a timeout. The thread is inserted into the "soon" wakeup list if its timeout is at most 16ms, into the medium-term wakeup list if its timeout is not more than 1024ms, and the "late" wakeup list if it has a finite timeout of more than 1024ms. The three lists are used to reduce the amount of list processing required at each 1ms clock tick;

present\_list: list of all valid TCBs, grouped by task;

int\_list: list of threads preempted by interrupts;

clock: system clock, mirrored in KIP;

- timeslice: remaining current time slice (i.e., time until next preemption);

- **priority:** current priority (as assigned by last scheduler invocation);

memory\_size: total RAM size;

- **trace\_reg\_save:** place where instrumentation code may save a register;

- tlb\_t0\_save-tlb\_t8\_save: place for TLB miss handlers to save t0-t8;

- **gpt\_pointer:** root of running thread's page table;

- profile\_addr: when kernel profiling is enabled, this is used to store the address where execution was interrupted by the timer;

- tcb\_gpt\_pointer, tcb\_gpt\_guard: root and root guard of kernel page tables (mapping TCBs) apparently unused;

- **frame\_list:** pointer to head of list of free kernel heap frames (i.e., high physical memory);

- free\_asid\_list, gpt\_free\_list, gpt\_leaf\_free\_list, mt\_free\_list: pointer to head of free lists

for: ASIDs, GPT internal nodes, GPT leaf nodes, mapping tree nodes, respectively. A separate free list

is maintained for each data structure of (potentially) different size. The ASID free list is in static kernel

memory, all others are on the kernel heap;

break\_on: used for setting kernel break points for debugging;

sigz\_tcb: TCB of  $\sigma_0$

asid\_fifo\_count: pointer to next ASID due for FIFO preemption;

int0\_thread\_int4\_thread: TID of handler thread of user-visible interrupts 0-4;

**fp\_thread:** TID of thread "owning" the FPU;

tlb\_miss,tlb\_miss\_time,tlb2\_miss: used in instrumented TLB miss handler to store miss counts and handling times;

syscall\_jmp\_table[8]: jump table used by syscall dispatcher;

exc\_jmp\_table[16]: jump table used by exception handler dispatcher;

prio\_busy\_list[MAX\_PRIORITY+1]: pointers to each priority's circular list of runnable threads, null if a

particular list is empty. The array entries actually point to the *tail* of the list, which is the TCB of the thread

that was last scheduled (and on whose time slice the present thread, whoever it might be, is executing). If

prio\_busy\_list[p] is non-null, then prio\_busy\_list[p]->busy\_link is the TCB at the head

of the list;

frame\_table\_base, frame\_table\_size, frame\_table\_pointer: unused.

### 3.2.3 TCBs

TCBs are allocated as a large array in virtual memory (CKSEG). The structure of a TCB is defined in include/kernel/kernel. Each TCB is half a page (2kB) in size. Only about 0.5kB of this is needed for various data structures describing a thread, the reminder is used as the stack during execution in kernel mode.

TCBs are allocated on demand: When a thread with no previously allocated TCB is created, a frame on the kernel heap is allocated and mapped to the appropriate entry in the TCB array. If an unmapped TCB of a non-existing thread is touched (e.g., when someone attempts to IPC to that thread), the Invalid TCB is mapped (by the TLB miss handler).

The individual fields of the TCB are listed here (again somewhat reordered). Entries marked "†" are task attributes which are only defined for  $l_0$ 's TCB; all others are defined for any active thread (even though some are logically task attributes):

sndq\_start, sndq\_end: head and tail pointers for the doubly linked FIFO??? queue of send operations

pending for this thread;

**sndq\_next**, **sndq\_prev**: link fields for send queue, only relevant if thread's state is PENDING;

soon\_wakeup\_link, wakeup\_link, late\_wakeup\_link: link field for short term, medium term, long

term wakeup lists, respectively;

wakeup: time at which the thread's timeout expires (defined for threads presently linked in a wakeup list);

**busy\_link:** link field for busy list (prioritised ready queue), zero if thread is not in the busy list;

int\_link: link field for list of interrupted threads;

present\_next: link field for TCB present list. This links all allocated TCBs of a task to allow efficient cleanup on task destruction;

wfor: TID of partner this thread is waiting to receive from;

stack\_pointer: top of thread's kernel stack;

asid: ASID value of task, -1 if task has no ASID allocated at present;

gpt\_pointer: root of task's page table;

myself: this thread's ID (TID);

**coarse\_state:** state of this TCB: *unused, used, invalid*. The latter is used to identify TCBs which are presently mapped to the shared *Invalid TCB*;

fine\_state: thread state. Set of:

BUSY: ready to run or running,

WAITING: blocked on a receive,

POLLING: blocked on a send; also called *pending*,

WAKEUP: waiting or polling thread with a finite timeout; is in a wakeup queue,

LOCKS: in long IPC, sending,

LOCKR: in long IPC, receiving,

DYING: task being killed (during task\_new),

INACTIVE: not activated but has a TLB allocated anyway (because it's the buddy of an active thread).

Only WAKEUP can occur in combination with other state values; CHECK!

timeout: timeout value in L4 timeout format (only some fields still relevant by the time it gets stored here...);

recv\_desc: receive descriptor for receive phase of IPC, stored here during send and while blocked on receive;

child\_task<sup>†</sup>: pointer to TCB of first child task (or NULL);

sister\_task†: pointer to TCB of next task in same clan (or NULL);

rem\_timeslice: remaining time slice of preempted thread;

timeslice: thread's time slice length;

**mcp**<sup>†</sup>: maximum controlled priority (MCP) as defined by the task\_new system call;

**bpad1:** byte padding (should never be accessed);

- tsp: scheduling priority of current thread;

- **ctsp:** scheduling priority under which the current thread is presently executing. This can be different from tsp due to *time-slice donation* and *priority inheritance*;

pager\_tid: TID of thread's pager;

**excpt\_tid:** TID of this thread's exception handler;

**comm\_partner:** pointer to TCP of thread we are waiting (or polling) for or are presently communicating with;

- wdw\_map\_addr: the base address, in the receiver's address space, of the temporary mapping area. This is used during long IPC to allow mapping a page fault address inside the temporary mapping area back to an address in the receiver's address space;

- **interrupt\_mask:** if thread is associated with an interrupt, this holds the corresponding interrupt mask. It has a single bit set which corresponds to the interrupt the thread is associated with;

fp\_regs[32], fp\_control: thread's FPU context;

pt\_size, pt\_number: page table space usage and number of mappings, used by instrumentation code;

**cpu\_time:** thread's accumulated CPU time.

### 3.2.4 Other kernel data structures

Other statically allocated data are:

TID Table: Array of task version numbers indexed by task ID. The format of a (32-bit wide) entry is:

| i | 0 (3) | chief (11) | 0 (2) | 0 | vers (14) |

|---|-------|------------|-------|---|-----------|

|---|-------|------------|-------|---|-----------|

Here *chief* is the present owner (chief) of the task, *vers* is the present task version number, *i*, if set, indicates that the task is inactive, and *o* indicates version overflow (task activated too many times). Note that the *chief* field is at the same position as in the upper word of a thread ID, and can therefore be matched without additional shift operations.

Debugger stack: Used as kernel stack during boot time, later as the stack for the kernel debugger.

**Sigma0 TCB:** Thread control block for  $\sigma_0$ . Only first half of page is used.

- NIL TCB: TCB of NIL thread what is it used for???.

- **Invalid TCB:** Page of two TCBs whose course\_state is marked invalid. Mapped on demand to TCB of non-existing thread (when faulting on an unmapped TCB).

- ASID Table: Array, indexed by ASID. For each ASID presently in use the entry contains the task ID it is associated with. For unused ASIDs it contains a pointer to the next free one, zero indicates the end of the list. The list head (pointer to first free entry) is in kernel\_vars.free\_asid\_list.

- **Interrupt TCBs:** TCBs of virtual threads representing interrupts. Inherit scheduling parameters from their respective interrupt handler threads (if associated).

Page tables are dynamically allocated on the kernel heap. Their structure is discussed with the miss handling code in Section 4.1.2 below. *Still TO DO: mapping database.*

# **Chapter 4**

# **Exception Processing**

## 4.1 TLB Miss Handling

TLB miss handling is, together with "short" IPC, the kernel operation most critical to performance of systems built on top of L4.

The L4/MIPS distribution contains a number of page table implementations, each in a separate subdirectory of kernel/vm/: multi-level page table (vm-mpt/), inverted page table (vm-ipt/), clustered page table (vm-cpt/), and guarded page table (vm-gpt/). The guarded page table (GPT) structure is also implemented in combination with two versions of a software TLB (STLB, vm-tlbcache-gpt/ and vm-tlbcache-gpt-pair/). The version to be built is specified by Makefile.conf:VM\_CODE. The kernel-internal API for the page tables is defined in include/kernel/vm.h.

**Implementation choice:** Elphinstone [Elp99b] showed that vm-tlbcache-gpt-pair/ is, of the ones implemented, the most appropriate version for L4. We will therefore not consider any of the other implementations.

The page table implementation in vm-tlbcache-gpt-pair/ supports four different implementation of the STLB: tlb2-1way-8.S, tlb2-1way-128.S, tlb2-2way-128.S, and tlb2-2way-8.S. The one used is selected by Makefile.conf/TLB2\_OBJ.

**Implementation choice:** Again, the study has shown that the most appropriate version is tlb2-lway-l28.S and only it will considered in this report. See Elphinstone's PhD thesis [Elp99b] for details on the various page table implementation and their analysis.

In summary, the kernel's page tables consist of a global, direct-mapped STLB of 128kB size, tagged with VPN and ASID. It contains 8k entries, each mapping two pages. Hence the total coverage of the STLB is 16k pages, or 64MB best case. Note that equals times the physical memory size for which the configuration was optimised. This results in reasonably high STLB hit rates.

On a miss the STLB is reloaded from a per-address-space GPT. Given that the STLB is configured for high hit rates, the GPT lookup costs are not very critical. However, GPTs can potentially grow rather deep (7–10 levels are not extraordinary), the GPT lookup code is therefore highly optimised.

## 4.1.1 Fast miss handler