# Verification of Programs in Virtual Memory Using Separation Logic

Rafal Kolanski

Ph.D.

2011

# **Originality Statement**

'I hereby declare that this submission is my own work and to the best of my knowledge it contains no materials previously published or written by another person, or substantial proportions of material which have been accepted for the award of any other degree or diploma at UNSW or any other educational institution, except where due acknowledgement is made in the thesis. Any contribution made to the research by others, with whom I have worked at UNSW or elsewhere, is explicitly acknowledged in the thesis. I also declare that the intellectual content of this thesis is the product of my own work, except to the extent that assistance from others in the project's design and conception or in style, presentation, and linguistic expression is acknowledged.'

| Signed |  |

|--------|--|

| Date   |  |

# **Copyright Statement**

'I hereby grant the University of New South Wales or its agents the right to archive and to make available my thesis or dissertation in whole or part in the University libraries in all forms of media, now or here after known, subject to the provisions of the Copyright Act 1968. I retain all proprietary rights, such as patent rights. I also retain the right to use in future works (such as articles or books) all or part of this thesis or dissertation. I also authorise University Microfilms to use the 350 word abstract of my thesis in Dissertation Abstract International (this is applicable to doctoral theses only). I have either used no substantial portions of copyright material in my thesis or I have obtained permission to use copyright material; where permission has not been granted I have applied/will apply for a partial restriction of the digital copy of my thesis or dissertation.'

| Signed |  |

|--------|--|

| Date   |  |

# **Authenticity Statement**

'I certify that the Library deposit digital copy is a direct equivalent of the final officially approved version of my thesis. No emendation of content has occurred and if there are any minor variations in formatting, they are the result of the conversion to digital format.'

| Signed |  |

|--------|--|

| Date   |  |

# **Abstract**

Formal reasoning about programs executing in virtual memory is a difficult problem, as it is an environment in which writing to memory can change its layout. At the same time, correctly reasoning about virtual memory is essential to operating system verification, a field we are very much interested in. Current approaches rely on entering special modes or making high-level assertions about the nature of virtual memory which may or may not be correct.

In this thesis, we examine the problems created by virtual memory and develop a unified view of memory, both physical and virtual, based on separation logic. We first develop this model for a simple programming language on a simplified architecture with a one-level page table, taking care to prove it constitutes a separation logic. We then extend the framework to deal with low-level C programs executing in a virtual memory environment of the ARMv6 architecture with a two-level page table. We perform two case studies involving mapping in of a new page into the current address space: first for the simple version of our logic, and finally for our full framework. The case studies demonstrate that separation logic style modular reasoning via the frame rule can be used in a unified model which encompasses virtual memory, even in the presence of page table writes.

To our knowledge, we present the first model offering a unified view of virtual and physical memory, the first separation logic involving an address translation mechanism, as well as the first published model of a functional subset of ARM memory management unit. Our memory models, framework, proofs and all results are formalised in the Isabelle/HOL interactive theorem prover.

# Acknowledgements

First and foremost, I wish to thank my supervisor, Gerwin Klein, for his continued advice, encouragement and support over the years. His friendly nature, Zen-like calmness and amazing work ethic have been a source of inspiration to me, and this work definitely could not have happened without him.

I would also like to thank the ERTOS and L4.verified teams at NICTA for the best work atmosphere one could wish for and all the good advice. In particular, I wish to thank June Andronick for her heroic efforts of proofreading this thesis, Thomas Sewell for always being willing to assist me in pushing the Isabelle theorem prover to the cutting edge, Michael Norrish for developing and assisting with the C parser I use in this thesis, and of course Harvey Tuch, from whose initial ideas about separation logic and C semantics sprouted my then far-fetched idea of marrying separation logic and virtual memory.

I also thank my parents for their continued support and patience during all the years of my thesis, as well as the years leading up to it.

Finally, I wish to say a thank you to my first Hapkido teacher, Master Scott Wetherell. While he had no direct involvement in this thesis, his strength and confidence contributed significantly to my being the person I am today. I hope that through me, part of his legacy lives on. May he rest in peace.

# **Contents**

| 1 | Intr       | oductio | on                                      | 1        |

|---|------------|---------|-----------------------------------------|----------|

|   | 1.1        | Overv   | riew                                    | 1        |

|   |            | 1.1.1   | Theorem Proving and Isabelle/HOL        | 1        |

|   |            | 1.1.2   | Operating Systems                       | 2        |

|   |            | 1.1.3   | Virtual Memory                          | 3        |

|   |            | 1.1.4   | Separation Logic                        | 3        |

|   | 1.2        | Contr   | ibutions                                | 3        |

|   | 1.3        | Relate  | ed Work                                 | 4        |

|   |            | 1.3.1   | Separation Logic                        | 4        |

|   |            | 1.3.2   | Operating System Verification           | 5        |

|   |            | 1.3.3   | Low-level Verification                  | 6        |

|   | 1.4        | Layou   | it of the Rest of the Document          | 8        |

| 2 | Not        | ation   |                                         | 9        |

| _ | 2.1        |         | le                                      | 9        |

|   | 2.2        | HOL     |                                         | 9        |

|   | 2.3        |         | al Notation in This Work                | 13       |

| 2 | <b>17:</b> | ual Ma  |                                         | 15       |

| 3 | 3.1        | ual Me  |                                         | 15       |

|   | 3.2        | -       | rtance of Virtual Memory                | 16       |

|   | 3.2        | 3.2.1   | al Memory Overview                      | 17       |

|   |            |         | Page Tables                             | 17<br>19 |

|   |            | 3.2.2   | Multi-level Page Tables                 | 21       |

|   |            | 3.2.3   | Translation Lookaside Buffer            | 21       |

|   |            | 3.2.4   | Caching                                 | 23       |

|   | 2.2        | 3.2.5   | Devices                                 |          |

|   | 3.3        |         | view of ARMv6 Address Translation       | 24<br>26 |

|   | 3.4        |         | view of Other Page Table Mechanisms     |          |

|   |            | 3.4.1   | Software-loaded TLB                     | 26       |

|   |            | 3.4.2   | Virtualised Page Table                  | 27       |

|   |            | 3.4.3   | Guarded Page Table                      | 27       |

|   | ٥. ٦       | 3.4.4   | Inverted Page Table                     | 28       |

|   | 3.5        | Sumn    | nary                                    | 30       |

| 4 | Sep        | aration | Logic                                   | 31       |

|   | 4.1        | An In   | formal Introduction to Separation Logic | 31       |

|   |            | 4.1.1   | The Factory                             | 31       |

|   |            | 4.1.2   | Pointer Aliasing                        | 33       |

xii CONTENTS

|   |          | 4.1.3   | Local Reasoning and Memory Safety                       | 36        |

|---|----------|---------|---------------------------------------------------------|-----------|

|   | 4.2      | Requi   | rements of Being a Separation Logic                     | 38        |

|   | 4.3      | Summ    | nary                                                    | 40        |

| 5 | Maj      | pped Se | eparation Logic                                         | 41        |

|   | 5.1      | Machi   | ine Architecture                                        | 41        |

|   |          | 5.1.1   | Pointers, Addresses and Values                          | 41        |

|   |          | 5.1.2   | Memory                                                  | 42        |

|   |          | 5.1.3   | A Page Table                                            | 42        |

|   | 5.2      | Separa  | ation Logic Assertions on Virtual Memory                | 43        |

|   |          | 5.2.1   | The Problem                                             | 44        |

|   |          | 5.2.2   | Slices and the Fractional Heap                          | 44        |

|   |          | 5.2.3   | Assertions                                              | 47        |

|   | 5.3      | The Lo  | ogic                                                    | 48        |

|   | 5.4      |         | Study                                                   | 53        |

|   | 5.5      |         | usion                                                   | 56        |

| _ | _        |         |                                                         |           |

| 6 | <i>-</i> | -       | pped Separation Logic                                   | <b>57</b> |

|   | 6.1      |         | tecture Setup                                           | 58        |

|   |          | 6.1.1   | Pointers and Addresses                                  | 58        |

|   | 6.2      | -       | Tables                                                  | 59        |

|   |          | 6.2.1   | A Page Table Abstraction                                | 59        |

|   |          | 6.2.2   | ARMv6 Page Table Formalisation                          | 61        |

|   | 6.3      | _       | ge of Values in Memory                                  | 66        |

|   |          | 6.3.1   | The Class of Memory-Storable Types                      | 67        |

|   |          | 6.3.2   | Loading Memory-Storable Types                           | 68        |

|   |          | 6.3.3   | Memory-Storable Words                                   | 69        |

|   |          | 6.3.4   | Memory-Storable Structures without Padding              | 70        |

|   |          | 6.3.5   | Memory-Storable Arrays                                  | 72        |

|   | 6.4      | Separa  | ation Logic Constructs at the Byte Level                | 73        |

|   |          | 6.4.1   | The Fractional Heap and Memory Views                    | 73        |

|   |          | 6.4.2   | Maps-to Predicates                                      | 75        |

|   | 6.5      | Type-l  | level Separation Logic Maps-to Predicates               | 76        |

|   | 6.6      | Slice A | Accounting and Read-only Maps-to Predicates             | 77        |

|   | 6.7      | Interfa | ace to the C Programming Language                       | 78        |

|   |          | 6.7.1   | Loading Values from the Fractional Heap                 | 79        |

|   |          | 6.7.2   | Updating the Fractional Heap                            | 80        |

|   |          | 6.7.3   | Reading and Updating Memory from C                      | 81        |

|   |          | 6.7.4   | A Simple Example: Swapping the Contents of Two Pointers | 83        |

|   | 6.8      | Case S  | Study                                                   | 85        |

|   |          | 6.8.1   | The Code                                                | 85        |

|   |          | 6.8.2   | The Code as Seen by Isabelle                            | 87        |

|   |          | 6.8.3   | Proof Stage 1: The Function as a Heap Update            | 88        |

|   |          | 6.8.4   | Proof Stage 2: A Heap that Contains a Mapping           | 90        |

|   |          | 6.8.5   | Final Proof: A Function that Maps                       | 92        |

CONTENTS xiii

| 7 | Disc | cussion | and Conclusion                               | 95  |

|---|------|---------|----------------------------------------------|-----|

|   | 7.1  | Summ    | nary                                         | 95  |

|   | 7.2  | Discus  | ssion                                        | 95  |

|   | 7.3  | Future  | e Work                                       | 98  |

|   |      | 7.3.1   | Translation Lookaside Buffer                 | 98  |

|   |      | 7.3.2   | Caching                                      | 99  |

|   |      | 7.3.3   | Devices and IOMMUs                           | 99  |

|   |      | 7.3.4   | Reasoning About Multiple Page Tables at Once | 100 |

|   |      | 7.3.5   | Larger Case Study                            | 100 |

|   | 7.4  | Concl   | uding Remarks                                | 101 |

*xiv* CONTENTS

# **List of Figures**

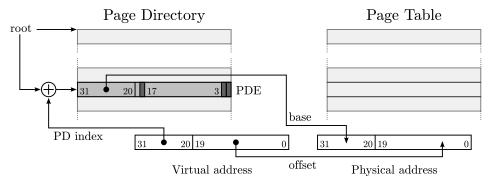

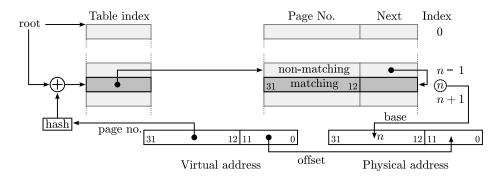

| 3.1   | A 32-bit virtual address on an architecture with 4KB page sizes                          | 18         |

|-------|------------------------------------------------------------------------------------------|------------|

| 3.2   | A lookup in a one-level page table on a 32-bit machine with a page                       |            |

|       | size of 4KB                                                                              | 18         |

| 3.3   | A lookup in a two-level page table on a 32-bit machine with a 4KB                        |            |

|       | page size with a 10-10 split on the page number                                          | 19         |

| 3.4   | A lookup in a multi-level page table. Intermediate levels not to scale.                  | 20         |

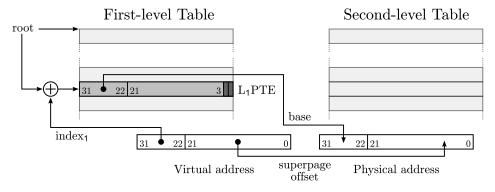

| 3.5   | A lookup in a two-level page table completing early due to a "don't                      |            |

|       | look further" flag in the first-level table, resolving to a superpage.                   | 20         |

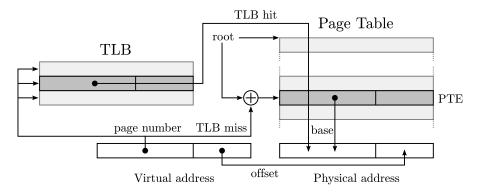

| 3.6   | Involvement of the Translation Lookaside Buffer (TLB) in the virtual                     |            |

|       | memory resolution process. If the page number is in the TLB, the                         |            |

|       | base address in the matching TLB entry is used. Otherwise, the page                      | 21         |

| 2.7   | table is consulted                                                                       | 21         |

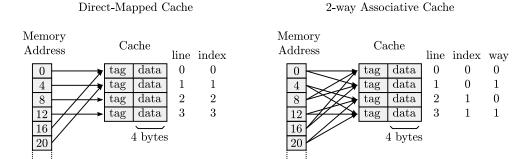

| 3.7   | Mapping memory addresses to cache lines for a 4-line cache with                          |            |

|       | 4-byte lines, in the case of 1-way associativity (direct-mapped) and 2-way associativity | 22         |

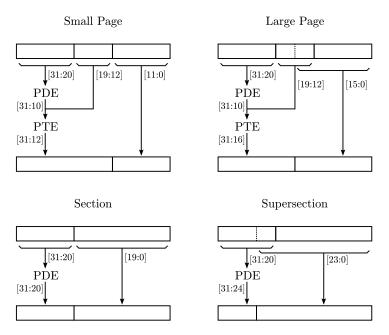

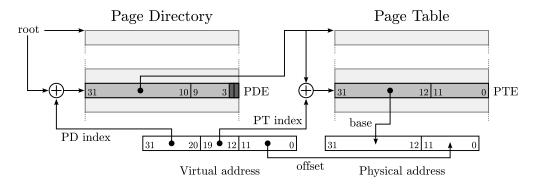

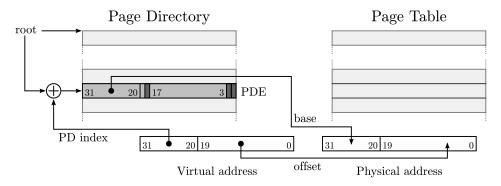

| 3.8   | Page table lookup for a 4KB small page on ARMv6                                          | 24         |

| 3.9   | Page table lookup for a 1MB section on ARMv6                                             | 24         |

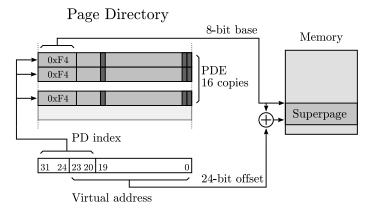

| 3.10  | The usage of bits in looking up a virtual address and resolving it to a                  | <b>_</b> 1 |

| 0.10  | physical one in ARMv6                                                                    | 25         |

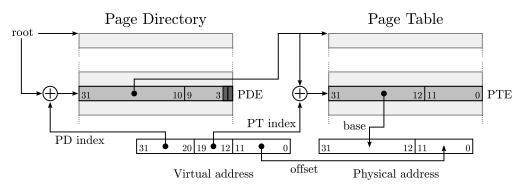

| 3.11  | A virtual address lookup in the page directory resolving to a super-                     |            |

| 0.11  | page. Note that bits [31:20] are used as an index into the PDE, but                      |            |

|       | only bits [31:24] of the PDE are used as the base address of the super-                  |            |

|       | page. This requires 16 identical PDEs in the page directory. The offset                  |            |

|       | within the superpage comes from virtual address bits [23:0]. A base                      |            |

|       | of 0xF4 indicates the 16MB superpage at physical address 0xF4000000.                     | 26         |

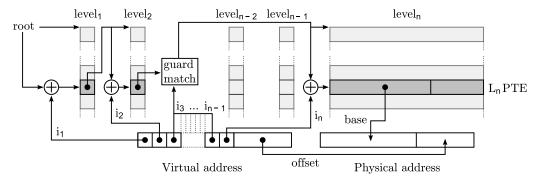

| 3.12  | A lookup in a guarded multi-level page table with a guard match at                       |            |

|       | level 2 resulting in a skip to level n                                                   | 27         |

| 3.13  | Looking up 0x123456000 in a guarded page table via a PTE requesting                      |            |

|       | 10 guard bits equal to 0x56                                                              | 28         |

| 3.14  | A lookup in an inverted page table. A hashing function is applied                        |            |

|       | to the page number of the virtual address and resolves to an index                       |            |

|       | via an index table. After resolving a collision chain of length one the                  |            |

|       | lookup successfully finds a table entry whose index forms the base                       | 20         |

| 0 1 5 | physical address. Process identifiers omitted                                            | 29         |

| 3.15  |                                                                                          |            |

|       | identical to the IPT it is based on, though there is no intermediate                     | 20         |

|       | table of indices                                                                         | 29         |

xvi LIST OF FIGURES

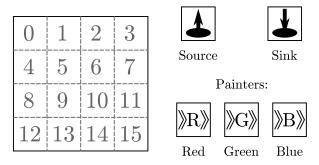

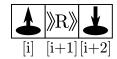

| 4.1         | Empty factory floor; factory components                                                                  | 32         |

|-------------|----------------------------------------------------------------------------------------------------------|------------|

| 4.2         | A working production unit for painting objects red                                                       | 32         |

| 4.3         | Factory operational semantics for the naïve model                                                        | 33         |

| 4.4         | Two production units pointed to by $p$ and $q$                                                           | 34         |

| 4.5         | Separating conjunction                                                                                   | 35         |

| 4.6         | Basic maps-to predicate of separation logic                                                              | 36         |

| 4.7         | Updated assignment rule                                                                                  | 37         |

| 4.8         | The frame rule                                                                                           | 37         |

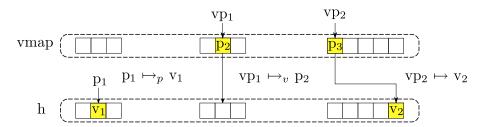

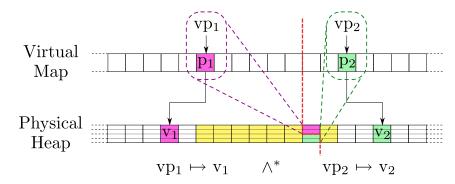

| 5.1         | Maps-to assertions on the heap, virtual map and address space                                            | 44         |

| 5.2         | The concept of two virtual-to-value mappings being separate in our                                       |            |

|             | framework despite being mapped through the same page table entry                                         |            |

|             | by virtue of using separate slices of the page table entry (the contested                                |            |

|             | region in the middle)                                                                                    | 46         |

| 5.3         | Syntax of the heap based WHILE language                                                                  | 49         |

| 5.4         | Semantics of arithmetic and boolean expressions                                                          | 50         |

| 5.5         | Big-step semantics of commands                                                                           | 51         |

| 5.6         | The proof rules for Mapped Separation Logic.                                                             | 52         |

| 5.7         | The page table interface                                                                                 | 53         |

| 5.8         | A simple page table manipulating program                                                                 | 54         |

| 5.9         | Specification of the program in Figure 5.8                                                               | 54         |

| 5.10        | The page_mapped predicate and associated definitions; page_mapped indi-                                  |            |

|             | cates that a page at a given virtual address is fully accessible                                         | 55         |

| 6.1         | Abstract page table interface                                                                            | 60         |

| 6.2         | Page table lookup for a 4KB small page on ARMv6                                                          | 63         |

| 6.3         | Page table lookup for a 1MB section on ARMv6                                                             | 64         |

| 6.4         | Memory-storable type class mem_type axioms for a type 'a                                                 | 67         |

| 6.5         | Addition and subtraction of offsets to pointers. "Raw" manipulation                                      |            |

|             | has byte granularity. Manipulation of pointers to type $'t$ , where $'t$ is                              |            |

|             | memory-storable has size_of $TYPE('t)$ . Sequences of pointers                                           | 68         |

| 6.6         | The memory-storable interface instantiated to words                                                      | 69         |

| 6.7         | An example of a structure in C                                                                           | 70         |

| 6.8         | Address of structure field operator for the <code>example_c</code> structure ( $_{\&}\rightarrow_{-}$ ). | 72         |

| 6.9         | Instantiation of arrays to the memory-storable type for an element                                       | =-         |

|             | type 'a and an index type 'b                                                                             | 73         |

| 6.10        | Basic constructs of mapped separation logic: separating conjunction,                                     |            |

|             | the empty heap and universal <i>True</i>                                                                 | 74         |

| 6.11        | Non-fractional views of the fractional heap for physical memory as                                       | 7.4        |

| <i>(</i> 10 | well as a program's address space (virtual memory)                                                       | 74         |

| 6.12        | Automatically generated variants of maps-to predicates, shown here                                       | <b>7</b> . |

| <i>(</i> 10 | for the virtual-to-value maps-to predicate                                                               | 76         |

|             | Type-level separation logic maps-to predicates                                                           | 77         |

| 6.14        | Automatically generated variants of typed maps-to predicates, shown                                      |            |

| (15         | here for the typed virtual-to-value maps-to predicate                                                    | 77         |

|             | Physical byte-level and type-level mappings with precise slice control.                                  | 78<br>70   |

|             | Read-only byte-level and type-level address space maps-to predicates.                                    | 79         |

| 0.1/        | Loading a memory-storable object from a fractional heap state given                                      | 70         |

|             | a virtual or physical pointer                                                                            | 79         |

LIST OF FIGURES xvii

| 6.18  | Rules of byte-level updates to physical memory and virtual memory                 |    |

|-------|-----------------------------------------------------------------------------------|----|

|       | addresses, as well as typed updates to pointers in virtual memory                 | 81 |

| 6.19  | The C pointer guard requiring alignment to the size of the pointed to             |    |

|       | object, as well as the zero address not being present in the range of             |    |

|       | addresses occupied by the object                                                  | 82 |

| 6.20  | Exported C semantics of loading and storing a value                               | 82 |

| 6.21  | The rules linking loading and storing of values in virtual memory                 |    |

|       | with the address spaces maps-to predicate                                         | 82 |

| 6.22  | A simple C function swapping the contents of two int pointers                     | 83 |

| 6.23  | Definition produced by the C parser for the function in Figure 6.22               | 83 |

| 6.24  | Specification and frame rule for program in Figure 6.22                           | 84 |

| 6.25  | The seL4 type definitions used in our case study                                  | 86 |

| 6.26  | The seL4 page mapping function code used in our case study                        | 87 |

| 6.27  | Definition of performPageInvocationMapPTE from Figure 6.26 pro-                   |    |

|       | duced by the C parser                                                             | 87 |

| 6.28  | Deriving an address space mapping from virtual and physical map-                  |    |

|       | pings                                                                             | 88 |

| 6.29  | $The  specification  of  {\tt performPageInvocationMapPTE}  in  terms  of  heap $ |    |

|       | updates                                                                           | 89 |

|       | Loop invariant used in the proof of the specification in Figure 6.29.             | 90 |

| 6.31  | The correspondence theorem between a page table entry (PTE) and                   |    |

|       | the page of virtual addresses it maps to physical ones                            | 91 |

| 6.32  | The consequence rule of SIMPL. It allows strengthening the precondi-              |    |

|       | tion and weakening the postcondition of an existing specification                 | 92 |

| 6.33  | Splitting a physical maps-to predicate into two read-only maps-to                 |    |

|       | predicates with complementary slice sets                                          | 92 |

| 6.34  | The specification of performPageInvocationMapPTE as a page table                  |    |

|       | mapping function.                                                                 | 93 |

| 7.1   | Lines of code and proof script in the different components of our work.           | 96 |

| / · I | thres of code and proof script in the different components of our work.           | 70 |

xviii LIST OF FIGURES

# **Chapter 1**

# Introduction

When planes fall out of the sky or ships collide, it would be really nice to know it was not a software problem. Mechanical parts wear out and fail, human pilots and captains make mistakes, while weather is unpredictable and can be often be dangerous and erratic. Software, on the other hand, does not wear out. It follows a set of prescribed instructions precisely, never wavering even in the face of overwhelming odds. As for weather, it can certainly interfere with the hardware that software runs on, but we have not yet heard of any weather phenomenon which interferes with software directly.

Software controls an ever-increasing amount of machines and devices around us. As we become more dependent on it, it simultaneously becomes more important that the software correctly implements the tasks it is meant to do. We can perform tests, but it is intractable to cover all possible cases in this manner. If we desire a higher level of assurance, we can create mathematical models of the software and prove things about them. We thus enter the world of *formal verification*. The question then becomes one of depth: the more in-depth the model, the higher our level of assurance as to the correctness of the software implementation conforming to that model, at the price of time required to verify it. A very simple model can be checked on paper. A simple model can be given to another piece of software and checked automatically, as is the case in model checking. More complex models require both human and machine input into the checking process, and a significant investment of time by both. If we go too deep, the high assurance may arrive after the software is declared obsolete.

The goal of our work is to move the world of operating system verification one step in the direction of realism, by providing a memory model which contains both physical and virtual memory in the same framework, with a single view of memory. We believe our fusion of virtual memory and separation logic constitutes such a step.

# 1.1 Overview

# 1.1.1 Theorem Proving and Isabelle/HOL

First, we believe it is important to define what we mean by "verified" and "correctness". A system cannot be verified in a vacuum, and there is no such thing as correctness as an absolute concept. When we say that a system is *verified*, we mean

a proof of that the effects of a system correspond a particular specification. This is known as functional correctness. Properties of systems can also be verified, by which we mean a proof that a particular model of the system exhibits a particular property.

In order to raise the confidence in our proofs beyond the level of paper and pencil, humans have enlisted the use of machines, leading to machine-checked proofs. There exist many frameworks, systems and procedures for providing such proofs. Our weapon of choice is Isabelle/HOL [42].

The Isabelle theorem prover is an interactive theorem proving framework built upon a minimal proof kernel. The kernel is based on LCF, or Logic for Computable Functions [25]. These types of kernels follow the approach of a small core capable of deriving and manipulating theorems, with all other functionality of the theorem prover having to go through this core's interface. The interface in turn is enforced by the type system of a strongly-typed language. Isabelle uses Standard ML [40]. Both the size of the core, since it can be rigorously checked, and the strongly-typed implementation result in a highly reliable proof system. If further reassurance is needed, Isabelle can also export "proof terms" which can be checked by a different, even simpler, theorem prover.

HOL, or Higher-Order Logic, extends first-order logic by introducing types and the ability to quantify over functions. Isabelle/HOL is an instantiation of HOL in Isabelle, along with a large body of structures and proofs about them, creating a rich theorem proving environment.

Every theorem proving environment comes with its own notation and idioms. We will cover those of Isabelle/HOL in Chapter 2.

# 1.1.2 Operating Systems

The operating system of a device is a software component which abstracts away the direct hardware interface. It provides an alternative high-level interface, upon which other software components can be executed. Operating systems on simple devices may only provide this interface and task scheduling. Modern operating systems running on more capable hardware must handle scheduling and execution of multiple user programs at the same time, while preventing their unauthorised access to hardware, protecting the operating system itself from corruption by user programs, and also protect the user programs from each other. This includes managing access to shared resources and inter-process communication. The operating system *kernel* is the part of the system that runs in privileged mode with direct hardware access. By setting up the hardware, the kernel constructs a restricted environment in which client programs can run. We call this restricted environment *user* mode. The boundary between user and kernel mode is enforced by the hardware.

The responsibilities of an operating system kernel and its direct access to hard-ware make it a critical component of the system. If it is not reliable, all programs running on the system may be unreliable. If it freezes, the entire system will be unresponsive. No matter how efficient it is, an operating system's usefulness is limited if its kernel doesn't reliably perform what it was designed to do.

It therefore makes sense to aim every weapon in our computer science arsenal at increasing the reliability and security of operating system kernels: beyond testing, beyond checking of simplified models and into the territory of proving something

about what an implementation actually does.

# 1.1.3 Virtual Memory

Virtual memory is a hardware-enforced abstraction providing running processes with their own "view" of memory (RAM). It is used in most modern operating systems capable of supporting multiple executing processes. All access attempts to virtual memory are intercepted by translation hardware which either resolves to a real memory access or to a violation reported to the operating system. The translation hardware uses a translation table called a page table, stored in real memory, meaning that writing to memory can change the layout of memory.

When used correctly, the virtual memory subsystem allows for process isolation, dynamic allocation, sharing data between processes and controlling access rights to memory regions. When used incorrectly, the system allows security leaks and mysterious crashes in programs whose functioning might otherwise be considered correct.

We will cover virtual memory in more depth in Chapter 3.

# 1.1.4 Separation Logic

Separation logic is an extension of Hoare Logic [28]. It was first presented by Reynolds [48] as a method for reasoning about imperative programs dealing directly with manipulation of memory. It focuses on local reasoning: separating out and defining rigidly the region of memory involved in access operations. This allows inferring the regions of memory which do not change, eliminating artifacts such as pointer aliasing. We introduce it in more detail in Chapter 4.

# 1.2 Contributions

We claim the following technical contributions:

- A novel approach to modelling behaviour of programs executing in the presence of virtual memory, based on separation logic. We model virtual and physical memory accesses in a single, unified view, without the need to enter special "modes". To our knowledge, we are the first to do this.

- Development of a separation logic which allows convenient, abstract reasoning about both the virtual and physical layers of memory, supporting the frame rule for arbitrary writes to memory (including the page table). The logic includes a separating conjunction extending to virtually shared memory.

- An abstract framework which makes the core logic independent of the machine architecture and page table implementation.

- An instantiation of our framework developed for demonstration purposes, using a simple machine architecture with a one-level page table, combined with a simple, deeply embedded imperative programming language with arbitrary pointer arithmetic. We prove this instantiation constitutes a separation logic according to the requirements of Calcagno et al. [13], and demonstrate that it can be applied in practice in a simple case study on page allocation.

- A formalisation of the page table subsystem on the ARMv6 architecture in non-legacy mode. We omit some features such as domains, but model a functionality subset sufficient to cover the usage patterns of the seL4 microkernel [31]. To our knowledge, this is the first formalisation of an ARM memory management subsystem in a theorem prover or otherwise.

- Instantiating our framework to our model of the ARMv6 architecture and a shallow embedding of the C programming language, made practically usable by connecting it with the verification framework based on Schirmer's SIMPL [49] used in the L4.verified project [31].

- A case study demonstrating modular reasoning about a C function which modifies the page table, identifying its precise semantics as a function inserting a new mapping into the page table. The function chosen is a small one from the seL4 microkernel [31], but the concept demonstrated applies in general.

All results presented in this work are formalised in the Isabelle/HOL theorem prover [42]. All definitions, datatypes and rules we present are output by the Isabelle/HOL theorem prover, resulting in this document being an accurate representation of our work.

# 1.3 Related Work

We gave a brief overview of the core topics relevant to our work in Section 1.1. Now we will discuss the relevant work of others.

# 1.3.1 Separation Logic

Since its inception [48], classic separation logic has been mechanised in Isabelle/HOL by Weber [60], HOL4 by Tuerk [58] and Coq by Marti et al. [39]

Further work by Calcagno et al. [13] defined what exactly constitutes a separation logic. By formulating an *abstract* separation logic which, appropriately, abstracts away the specifics of memory model and state, they formulate a class of *separation algebras* suitable for local reasoning. They demonstrate that the original separation logic is one instance of abstract separation logic. They define the properties a logic must have in order to be called a separation logic; properties which we use to demonstrate that our logic is a separation logic in Chapter 5.

Although we do not use them in our work, the local semantics of separation logic allow for reasoning about concurrency [10] [44]. If two regions of memory are separate, it logically follows that updating one does not affect the other. This means if the regions are given out to two processes, those processes can be executed or interleaved in any order. It also means there can be no sharing between them.

In order to enable read-only sharing of resources between concurrent processes while remaining a separation logic, Bornat et al. [10] introduced *permissions*. Instead of treating cells in memory as atomic units, they allow referring to parts of them, e.g. half of the cell at address 5 contains the value 7. The semantics allows memory reads from partial cells, but memory writes still require an entire cell. Our work uses a similar idea in the concept of *slices* introduced in Chapter 5. We compare these ideas in detail in Chapter 7, Section 7.2.

# 1.3.2 Operating System Verification

The first attempts to realise the vision of a verified operating system were PSOS [18] and UCLA Secure Unix [47]. The former had a specification, but no proofs. The latter had a specification and about 20% of proofs refining it to its implementation in Pascal. The first system to be completely verified with respect to a specification was Bevier's KIT [7]. By aiming for a smaller, simpler kernel, Bevier managed to push implementation proofs right down to assembler. Unfortunately, this approach resulted a set of kernel features too small to be used by the industry. Thus, after this achievement, the next challenge was to create a more industry-capable verified operating system.

While this was going on, the operating system world started experimenting with scaling back the size of the kernel, or at least breaking it up into pieces, in order to more closely approach real modularity by having the boundaries between operating system modules enforced by hardware [26]. The most common term for such a system is *microkernel*. There also exist *hypervisors* [11,24] which, while similar in their minimalist spirit to microkernels, are targeted at running multiple guest operating systems rather than programs. While microkernels can act as hypervisors, the latter are tuned to re-expose an interface resembling actual hardware, while the former offer a more generic interface.

Unfortunately, microkernels were hard to get right. The first microkernel, Hydra [61] was never widely used due to poor performance. The Mach [2] kernel, which coined the phrase microkernel, was somewhat large and also had poor performance. As a consequence, migration of features into the kernel to improve speed resulted in a kernel that was anything but micro. These early results suggested a different approach was necessary: moving into user mode anything that does not need to be in the kernel, focusing on appropriate abstractions and fast communication [38]. Some of the new wave of microkernels that resulted from this approach did successfully make it into industry: QNX [51],  $\mu$ -velOSity [50] and OKL4 [35].

The increased viability of microkernel-based operating systems whose kernel size was deserving of the name also contributed to an atmosphere in which attempting verification of operating system kernels made sense [56]. The Verisoft project [4] attempted verification of an entire stack: from user-mode applications down to the logic gates of the processor. Verisoft completed most, but not all of the proofs. Nonetheless, their scope was a narrow slice through all layers, so their kernel was simplified and optimised for verification, not performance. The first kernel with a real claim to the industry-capable verified operating system kernel title turned out to be the seL4 kernel from the L4.verified project [31]. We use some of the source code from this kernel in our case study in Chapter 6.

Due to their direct interface to hardware, as well as the goal of utilising hardware resources as efficiently as possible, operating systems are typically implemented using low-level programming languages such as C [30], even using processor instructions directly where necessary. Since separation logic was developed for reasoning about imperative programs with direct access to memory, that makes it applicable to operating system verification.

### 1.3.3 Low-level Verification

### Assembler

Assembler is the human-readable version of instructions executed by a processor. Given a semantics for those instructions, one can show the exact result of them being executed. At the same time, assembly offers little higher-level information for humans, making it a challenge to reason about. Our work does not include reasoning about programs at the assembly level, even though we do model the bits and bytes in a page table and the lookup procedure used by hardware.

### C

The C programming language [30] is one of the most popular languages used for developing low-level applications, as well as operating systems. Although C++ is also used, the subset of its semantics that has been formalised remains small [59]. Projects attempting verification of C++ code, such as VFiasco [29], have not yet moved past their preliminary stages. It is in our opinion far too complex a language to involve in formal verification.

In fact, although the C programming language appears simple, it is sufficiently complex for it to be tricky to reason about. Various attempts exist at modifying C to be simpler for verification purposes. Examples include C0 in the Verisoft project [36], Cminor [37] and C-light [8] (a "representative subset").

Norrish formulated a formal semantics of the C programming language [43]. He also developed a C to Isabelle/HOL parser [57] which parses a substantial subset of C code. The result is represented inside Isabelle/HOL using the SIMPL [49] environment developed Schirmer for verification of sequential imperative programs. When combined with the memory model of Tuch [54,55], which includes storage of C structures and padding, the combined framework [57] captured a significantly large part of C semantics to be used for the verification of the seL4 microkernel [31].

Tuch's memory model supports both separation logic and typed heaps of Burstall [12] and Bornat [9], and takes into account the presence of padding in C *structs*. It is, however, a flat memory model and does not deal with virtual memory in any way. Our work is inspired by the results of the L4.verified project, but our focus is on virtual memory. We use Norrish's C parser, but plug in an entirely new memory model. We focus on separation logic exclusively. We also don't currently handle padding, since we observed that no C structure in the seL4 kernel has any.

There exist other tools for formal reasoning about C code. Key-C [41] deals only with the type-safe subset of C. VCC and Caduceus both generate proof obligations from annotated C code. VCC [15] tries to discharge them automatically. It additionally supports concurrency. The Verisoft XT project used VCC to successfully perform automated proofs for a very small hypervisor [5]. However, VCC uses a memory model which axiomatises a weaker version of what Tuch proves. Caduceus [20] translates C code into the functional language of the Why [19] tool, which then generates verification conditions that can be proved by other tools. Like Norrish's C parser, Caduceus covers a substantial subset of C. Caduceus is now part of the Frama-C framework [1]. None of memory models in these frameworks have virtual memory built in.

Gast [23] describes a way of reasoning about some of C's more complicated

7

features, such as pointers to local variables, which don't typically appear in formalised C semantics such as those used in the L4.verified project or Caduceus. To our knowledge, a larger framework incorporating such features does not yet exist.

# **Architectures and Virtual Memory**

Reasoning about the interaction between software and hardware requires a model of the hardware. Our work involves reasoning about virtual memory on the ARMv6 architecture. While thorough models of the ARMv6 [21] and ARMv7 [22] instruction set semantics exist, they do not include the memory management unit. Tews et al. include some virtual memory characteristics in their model of the IA32 architecture [53]. Our work contains a model of the page table behaviour of the ARMv6 in *non-legacy* mode, as described in Chapter 3 and Chapter 6. To our knowledge, it is the first such model.

When it comes to reasoning about programs executing in virtual memory, especially the operating system itself, we have seen two approaches used.

The first approach is to set up a rigid page table structure, abstract it away and from that point on act like it isn't there. This approach was used in the Verisoft project [3]: a simple one-level page table for user programs, direct physical access for the kernel (no translation), limited functionality for mapping, unmapping and remapping. The simplicity, however, allowed for verifying a paging mechanism. The L4.verified [31] project sets up a semi-rigid structure: a range of addresses at the top of virtual memory in any page table is accessible by the kernel only and maps directly, one-to-one, to physical memory. The lower addresses of virtual memory can be used by user-level tasks, but the kernel never touches it; it only manipulates memory through the top section of virtual memory. The L4.verified project proved invariants which state that even though the kernel page table is in the one-to-one virtual memory region, all writes to this region do not affect its mappings in virtual memory. However, since virtual memory is not part of the core memory model, the invariants do not *follow* from the model, but rather are forced onto the model by human hand.

The other approach we have encountered is a "magic mode" abstraction. In normal mode, we expect virtual memory to behave much like normal memory, and the set of mappings from virtual to physical memory cannot be modified. To modify the contents of page tables and, as a result, the mappings, one has to enter a special mode. In this special mode one can modify the memory however one wishes, and any invariants about the memory state have to be reestablished upon returning to normal mode. This approach is used in the Robin project [52,53]: there is a subset of addresses which is *blessed* and can be accessed normally as *plain* memory. Writing to outside blessed regions violates the plain memory property and requires that the property be reestablished.

In our work, we acknowledge the fact that writing to a page table entry necessarily invalidates the regions of virtual memory that are resolved through that entry, but we also observe that it isn't the end of the world. Writing to the second level of a two-level page table with 4KB sizes only affects 4KB of virtual memory addresses, and the rest remain unaffected. This means we can apply local reasoning, and hence separation logic, to specify exactly what changes. When we know *exactly* what changes, we can derive what does not change via the frame rule. Additionally,

by using a single memory model, we do not enter or exit any special modes. Our rules are standard separation logic Hoare-style triple reasoning.

# 1.4 Layout of the Rest of the Document

Chapter 2 introduces the basics of Isabelle/HOL notation as well as the more common structures we use in our formalisation and proofs. Although this is mostly standard and can be skipped by a reader experienced in Isabelle/HOL, we do use some variants of standard notation for presentation purposes.

Chapter 3 contains an in-depth discussion of virtual memory, address translation, issues involved and different page table types. A reader experienced with operating systems and virtual memory may wish to skip directly to Section 3.3 where we discuss the ARMv6 page table which we will use in instantiating our framework in Chapter 6.

Chapter 4 contains an introduction to separation logic, beginning with an informal. A reader well-versed in separation logic may wish to skip this chapter entirely.

In Chapter 5 we present the core idea of our work, mapped separation logic. We instantiate it to a simplified machine architecture supporting virtual memory. We also perform a small case study using a simple programming language to show it is indeed a separation logic. This chapter is based on our paper by the same name [33].

Chapter 6 describes our improved and extended version of mapped separation logic. We instantiate it to an ARMv6 architecture and page table and add pointers to objects in memory. We create an interface to the C programming language and the Norrish's C parser [57], along with a simple demonstration of this functionality. Section 6.8 of Chapter 6 contains our case study, in which we verifying the semantics of a function from the seL4 microkernel [31] which writes to the page table.

# Chapter 2

# **Notation**

In this chapter we will give an overview of Isabelle/HOL [42] idioms and notations. As we mentioned in Chapter 1, Isabelle/HOL is a Higher-Order Logic implementation on top of the Isabelle theorem prover.

# 2.1 Isabelle

Isabelle has its own "meta" logic, in which other logics, such as HOL can be implemented. For theorems in the metalogic, there are zero or more assumptions, as well as one goal. We write these using meta-implication, denoted by  $\implies$  \_. It has multiple syntax variants. The following are all equivalent:

$$A \implies B \implies A \wedge B \qquad \qquad \llbracket P; \ \mathcal{Q} \rrbracket \implies P \wedge \mathcal{Q} \qquad \qquad \frac{P \quad \mathcal{Q}}{P \wedge \mathcal{Q}}$$

The rightmost variant mimics standard logical notation, thus we use it for presentation of rules. There is also meta-equality, written as  $_{-}\equiv_{-}$ . These mostly appear in definitions. For the purposes of reading this document, it is safe to assume that meta-equality is the same as normal equality.

Isabelle also supports a type system. We write x :: 't to indicate that x has type 't. Type variables have an apostrophe in front, e.g. 't, 'zft. By convention, type names are usually lowercase.

Functions in Isabelle are total. Their types are written using  $\Rightarrow$ , e.g.  $'d \Rightarrow 'r$ . Application of a function f to arguments x, y and z is written as f x y z, which yields three function applications, resulting in functions at each stage, i.e. ((f x)) y) z). One can construct functions on the fly using lambda notation, e.g.  $\lambda x$ . x = y.

Isabelle supports custom syntax for constants. When dealing with the syntax of *infix* operators, we refer to the operator itself using op. For example, a + b is identical to op + a b.

### 2.2 **HOL**

We will now cover the standard components of the HOL instantiation in Isabelle. We will refer to this as "HOL" throughout.

# **Basic Logic**

HOL defines the standard boolean operations of first-order logic, as well as standard quantification operators:

| negation               | ¬ P                   |

|------------------------|-----------------------|

| conjunction            | $P \wedge Q$          |

| disjunction            | P V Q                 |

| implication            | $P \longrightarrow Q$ |

| universal quantifier   | ∀x. P x               |

| existential quantifier | ∃x. P x               |

### **Functions**

Functions in HOL are defined using a set of equations. The simplest of these are definitions, which only have one equation and can neither recurse nor have any constructors on the left-hand side. For example, the definition of the identity function is:  $id = (\lambda x. x)$

HOL provides several ways of constructing functions from sets of equations with different tradeoffs between ease of specifying the equations compared to reasoning about them later. Since functions in HOL are total, recursive function definitions must be accompanied by a potentially automatic termination proof. For the purposes of this work, we will simply state the function types and their corresponding equations.

The function composition operator is defined as follows:

$$f \circ g = (\lambda x. \ f \ (g \ x))$$

The term f(x := y) represents a function derived from f, but updated such that f(x = y).

### Let

The let construct allows writing a term such as:

let

$$a = f x$$

;

$b = g a$

in  $h a b$

instead of:

We use it to improve readability of complicated statements.

# **Datatypes**

Datatypes are types which can have different kinds of contents, each tagged by a *constructor*. The constructor is also a function that will construct a particular kind of content. A simple datatype is that of bool, which has the constructors True and False:

2.2. HOL 11

```

datatype bool = True / False

```

By convention, datatype constructors start with a capital letter.

We can differentiate values of a datatype based on the constructor used to make them with case, for example:

```

case is_magic of True \Rightarrow 42 / False \Rightarrow 0

```

### **Pairs**

Pairs are denoted by (a, b) where a and b are the two members. The first can be accessed with fst, the second with snd.

Multi-member tuples are actually a left-associative construct of pairs. For example, (a, b, c, d) has the type 'a  $\times$  'b  $\times$  'c  $\times$  'd, which is internally represented by 'a  $\times$  ('b  $\times$  ('c  $\times$  'd)).

# Option

The 'a option datatype is a simple container type with two constructors:

```

datatype 'a \ option = \lfloor 'a \rfloor \ / \ None

```

As its name suggests, it has the option of containing the value of that type, or None. By using an option type as the range of a function, we can create partial functions. HOL even has special syntax for such functions, thus the following types are identical:

```

bool => bool option

bool → bool

```

Given |x|, we can get x directly using the:

```

the :: 'a option \Rightarrow 'a

```

Note that the None returns undefined, which is a HOL constant representing "any value of a given type". Another name for this constant is arbitrary.

Applying a function to the contents of an option type is done using Option.map:

```

Option.map :: ('a \Rightarrow 'b) \Rightarrow 'a \ option \rightharpoonup 'b

```

As one would expect, Option.map f None is None and Option.map f [x] is [f x].

# Type Declarations and Type Introspection

The typedecl keyword declares a new type in Isabelle without any extra information. We use this in Chapter 6 to declare tags for our two types of pointers: virtual and physical.

Isabelle allows limited type introspection. We can create functions which work on types: rather than working on values of 'a, such functions work on 'a itself.

TYPE allows capturing types to pass as values to such functions, i.e. the type of TYPE('a) is 'a itself.

Types in the finite type class have a finite number of members (cardinality). This number can be queried using CARD, e.g. CARD ('a).

### Sets

In HOL, sets are represented as functions from the type of element to bool. The empty set is denoted by  $\emptyset$ , the universal set by UNIV.

HOL set notation is otherwise standard:

| set of elements   | {e1, e2, e3}                    |

|-------------------|---------------------------------|

| membership        | $x \in S$ , $x \notin S$        |

| union             | $S \cup T$                      |

| intersection      | $S \cap T$                      |

| difference        | S - T                           |

| product           | $S \times T$                    |

| subset            | $S \subset T$ , $S \subseteq T$ |

| set comprehension | {x   P x}                       |

### Lists

The *list* datatype features the empty list as well as a list constructor for prepending an element to an existing list:

```

datatype 'a list = [] | 'a · 'a list

```

HOL contains the usual operations on lists: hd gets the first element, tl gets the rest, length calculates the list length, set constructs a set from the lists's elements, map applies a function to all list elements, zip creates a list of pairs from two lists, and fold reduces a list to one element by applying a folding function from left to right. We list their type signatures here for reference:

```

hd :: 'a list \Rightarrow 'a

tl :: 'a list \Rightarrow 'a list

length :: 'a list \Rightarrow nat

set :: 'a list \Rightarrow 'a \Rightarrow bool

map :: ('a \Rightarrow 'b) \Rightarrow 'a list \Rightarrow 'b list

zip :: 'a list \Rightarrow 'b list \Rightarrow ('a \times 'b) list

foldl :: ('a \Rightarrow 'b \Rightarrow 'a) \Rightarrow 'a \Rightarrow 'b list \Rightarrow 'a

```

The nth element of a list is obtained using -[n]. Taking and dropping n elements from a list is done using take n and drop n respectively, while concat concatenates a list of lists into one list.

### Numbers

Apart from words, which we will cover shortly, the other type of number which appears in our work is the type of natural numbers. Natural numbers are also a datatype, built around zero and the successor function Suc:

```

datatype nat = 0 / Suc nat

```

The min and max functions respectively find the minimum and maximum of two comparable quantities.

Division is performed by \_ div \_, and when x divides y, we write x dvd y.

### **N-bit Words**

HOL provides a library of n-bit words. These can be considered to be an n-length vector of bits, or a ring modulo  $2^n$ . They can be constructed from a natural number using of\_nat, while unat performs an unsigned conversion to a natural number.

The word library provides standard bitwise word operations:

| bitwise not       | NOT _   |

|-------------------|---------|

| bitwise and       | _ AND _ |

| bitwise or        | _ OR _  |

| shift left        | _ << _  |

| shift right       | _ >> _  |

| nth bit as a bool | _ !! n  |

The mask function creates a word whose lowest n bits are set. The size function takes an n bit value and returns n as a natural number, e.g.

$$size (w :: 32 word) = 32$$

# Maps

In HOL, a map is a partial function, i.e. function with the type:

These are the operations we use on maps:

```

empty map domain m = \{a \mid m \mid a \neq N \text{ None}\} merge \text{ (right-override)} f + + g = (\lambda x. \text{ case } g \text{ } x \text{ of None} \Rightarrow f \text{ } x \text{ } \lfloor y \rfloor \Rightarrow \lfloor y \rfloor) restrict domain m \upharpoonright_A = (\lambda x. \text{ if } x \in A \text{ then } m \text{ } x \text{ else None}) [d1 \mapsto r1, d2 \mapsto r2]

```

# 2.3 Special Notation in This Work

In this work, we differentiate all constants, such as datatype constructors by using a different font. For example, when stating that x is True, one can clearly see which is a constant already defined in the current theory, and which is the variable: x = True. Some existing constants define their own syntax, and their writers chose their own notation. In such cases we do not interfere, even if the notation chosen is a normal word. An example of such notation is the integral division operator:  $_{-}$   $_{div}$   $_{-}$ .

**Lifted conjunction** We define a conjunction predicate which works on predicates taking one parameter and returning bool:

**K combinator** We state the functional K combinator in HOL:

$$K :: 'a \Rightarrow 'b \Rightarrow 'a$$

$K \equiv \lambda x \ y. \ x$

**Map disjunction** We define two maps to be disjoint if their domains are disjoint:

We will explain the constants and their notation as we define them. We may repeat some of the definitions shown in this chapter for reader convenience.

# Chapter 3

# **Virtual Memory**

Virtual memory is a hardware-supported abstraction over physical memory. It is used in most modern operating systems. Virtual memory allows isolation of programs, dynamic allocation, permission control over memory access and sharing of memory between programs. Although the term "physical memory" is sometimes extended to encompass all physical media such as disk, we consider only the main system memory to be physical memory. This is nearly always RAM.

In this chapter, we introduce virtual memory, its relevance, fundamental concepts and mechanisms. In Section 3.2 we introduce page tables, and in particular, in Section 3.2.2 we discuss the most common setup for 32-bit machines: the two-level page table with optional superpages. Section 3.3 documents an implementation of this on a real architecture, ARMv6. We conclude with a discussion of some of the less popular page table models, which we do not formalise in our work.

We will present a formalisation of a one-level page table in Chapter 5, and a two-level page table of the ARMv6 architecture in Chapter 6. While our formalisation does not presently cover other page table types, caches or the translation lookaside buffer (TLB), we nonetheless discuss these concepts in this chapter, in order to give an impression of the diversity of the underlying mechanisms our framework may later be applied or extended to.

# 3.1 Importance of Virtual Memory

An operating system executing highly specialised tasks on limited hardware may depend on a priori knowledge about the nature and requirements of those tasks. However, an operating system claiming to be *general purpose* cannot, by its very nature, know what tasks executing on it will try to do. In particular, it cannot know how much memory a task will require.

A task is supplied by a user in the form of a program. To run the program, an operating system creates a process. Since programs are user-supplied, their memory requirements are initially unknown. Allocating "enough" memory beforehand makes no sense, as it may be too little (task cannot complete) or too much (memory wasted on this process cannot be given to other processes). Trusting the user to supply this information likewise makes no sense, as the user may be wrong, their program may be buggy or even malicious.

The virtual memory mechanism involves hardware-level monitoring of every memory access attempt performed by a process and checking it against a table of valid memory locations for the process. This allows allocation of physical memory on an as-needed basis, while restricting access to memory the process is not authorised to access. The operating system sets up these tables and is invoked whenever there is a problem.

An operating system running user-supplied programs should minimise the possibility of those programs being able to interfere with each other, whether accidentally or intentionally. This means that programs must not be able to access each other's memory unless *specifically permitted to do so* by first asking the operating system for permission. Permission granted need not be absolute; access to memory may place restrictions on execution, reading or writing. The virtual memory mechanism is enforced by hardware, and the operating system controls the mechanism, which allows memory isolation between programs.

Work performed by a process at any time tends to centre around a set of resources relevant to the task at hand. This set of resources that the process is currently working with and accessing in quick succession is called the process' working set. It changes over time. The implication of this is that to perform its task successfully, a process does not need all of the memory allocated to it all of the time. Physical memory not in use by a process can be backed up onto another physical medium, such as disk, and made available to whichever process needs it next. Since the virtual memory mechanism monitors all memory access, the operating system can request that it be invoked when the process tries to access its "missing" memory, in order to load it from disk. This process is known as demand paging or swapping. Since the focus of swapping is keeping the working set of processes in memory, it allows execution of processes with resident sizes exceeding the size of physical memory. There is a limit to the benefits of swapping: when the sum of working sets of all processes on the system exceeds the size of physical memory, however, the system will spend most of its time juggling memory between processes and disk, resulting in performance degradation.

We omit any discussion of segmented memory architectures. While the rather popular x86 architecture is segmented, the segments are typically set up to be identical. Actual use of segmentation is rare; e.g. using a segment for thread-local storage on Windows and some versions of Linux.

In the remainder of the chapter, we will describe the mechanism by which virtual memory can allow the behaviours mentioned in this section. We will omit discussion of swapping, as it is a matter of operating system policy rather than the mechanism itself.

# 3.2 Virtual Memory Overview

The basic idea behind virtual memory is that a process cannot access physical memory directly. Instead, a process accesses *virtual memory addresses*, which are resolved to physical addresses by a hardware-supported translation mechanism controlled by the operating system.

From the point of view of the user process, it has access to a large, contiguous address space. Reading and writing to "allocated memory" works. Execution proceeds normally. It is as if the process was the only one on the system. In reality, this address space *does not exist*. This is where virtual memory gets its name. Only

physical memory exists. Virtual memory accesses are treated as requests. They can be:

- denied e.g. invalid address, attempt to write to a read-only area; usually results in the process being killed.

- delayed the value viewable at a virtual address by a given process is not currently available; for instance, it has been placed on disk.

- granted the virtual address is translated to a physical one and the access is performed on the physical address.

In the first two cases, a hardware-enforced virtual memory abstraction invokes the operating system with information on what went wrong.

# 3.2.1 Page Tables

So far, we have been talking about virtual memory in terms of individually mapping each virtual address to a physical one. The virtual-to-physical memory map is many-to-one (the same physical address may appear at multiple virtual addresses), partial (some virtual addresses are not mapped), and annotated with permission flags supported by the hardware (e.g. read/write/execute). In order to perform the per-process access control and translation necessary for virtual memory to work, these mappings have to be stored somewhere. Typically, they are stored in physical memory where the hardware can access them to perform lookups. The encoded form of the set of virtual-to-physical mappings, stored in physical memory, is known as a *page table*.

Access to and manipulation of page tables is the domain of the operating system kernel. The kernel needs to set up its address space in order to access the entirety of physical memory and also set up the address spaces of user-level programs. Conversely, a user-level program should never have access to its own page table. If it can access its page table for any reason, it can modify its memory layout to allow access to data in other programs and in the operating system itself. This circumvents the point of virtual memory in the first place.

Let us examine the case of a 32-bit machine, i.e. a machine with 32-bit registers. Since memory pointers need to fit in registers, the machine will have a 32-bit virtual address space. Typically, the physical address space will also be 32-bit, though hardware specifics will dictate how much of it is accessible. This means there are  $2^{32}$  virtual addresses to keep track of per process. Each mapping is 32-bits in size, i.e. 4 bytes. Storing one physical address per virtual address in the mapping would hence require  $4*2^{32}$  bytes (16GB) of memory for the entire set of mappings, *per process*. Clearly, this is not a viable solution.

One way to approach this problem is by decreasing the *granularity* of the mappings, from bytes to larger-sized *pages*. In each entry, we store the physical address a page is mapped to. A typical page size is 4KB ( $2^{12}$  bytes). If we store one physical address per page, we now need  $2^{20}$  mappings per process for a 32-bit machine.

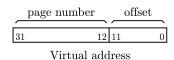

In this setup, the virtual address can be broken down as in Figure 3.1. The highest 20 bits of the virtual address indicate which page it lies in – the *page number*. This can be used as an index into the table of mappings, to obtain the physical address of where the page is mapped to. The lowest 12 bits of the virtual address

**Figure 3.1:** A 32-bit virtual address on an architecture with 4KB page sizes.

are the *offset* within the page. By adding them to the physical address the page is at, we resolve the virtual address to a physical one.

With 32-bit physical addresses, this means our table needs to be  $4*2^{20}$  bytes per process, or 4MB, already a significant improvement. The downside to a decrease in granularity is imperfect use of allocated memory. If a process uses only one byte in a page, the operating system needs to allocate it the entire page anyway. This is called *internal fragmentation*. Per-byte granularity has no internal fragmentation, but is effectively impossible. Some hardware supports variable-sized pages, shifting the responsibility for the most efficient choice to the operating system designer, which we discuss starting with Section 3.2.2.

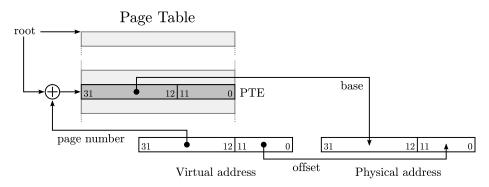

**Figure 3.2:** A lookup in a one-level page table on a 32-bit machine with a page size of 4KB.

One more aspect of our mapping table to consider is the physical equivalent of pages: *frames*. In the previous paragraph, we allowed a page to map to any physical address. Real hardware does not allow this due to efficiency considerations. Instead of performing addition, the hardware takes a 32-bit virtual address, translates the first 20 bits as in our example, and leaves the last 12 unchanged. The first 20 bits before the translation we call the *page number*, while after the translation they become the *frame number*. Taking this into consideration, when we store the frame's address in our table, we know the last 12 bits will always be zero, since the last 12 bits of any page are zero. Therefore rather than wasting 12 bits per entry, one can place any extra flags (e.g. read/write/execute permission flags) there. A special value, typically 0, is used for entries to indicate that a page is not mapped, i.e. does not have a corresponding physical frame.

There exist many ways of encoding the virtual-to-physical mappings. The table of entries we described in this section is among the simplest available: the *one-level page table*. We will discuss other encodings later in the chapter. The procedure we described for using the page table to resolve a virtual address into a physical one we refer to as a *page table lookup*. Figure 3.2 shows this process for our one-level page table. We refer to the location at which the page table can be found as the page table *root*.

In Chapter 5, we will discuss our formalisation of a simple 32-bit machine

with a one-level page table, as a simple test case for our mapped separation logic framework.

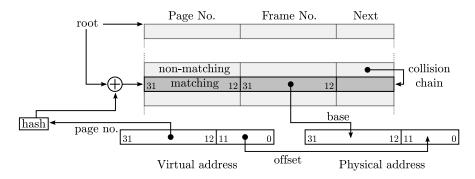

#### 3.2.2 Multi-level Page Tables

In Section 3.2.1 we explained the origins of the single-level page table. Though a single-level page table can store the mappings for the entire virtual address space, it cannot store any fewer. It turns out that in practice, a process usually does not use the entire address space. At 4MB, the single-level page table we described would use up 200MB of memory for 50 processes, regardless of how sparse their use of the virtual address space actually is. This is a waste of memory. What we need is a structure that can map sparse address spaces efficiently. The per-process solution to this problem is use of a *multi-level* page table.

In our single-level page table example, we divided a virtual address into a 20-bit page number and a 12-bit offset within that page. We used the page number as an offset into a table of addresses of corresponding frames.

The concept of the *multi-level* page table is to simply divide the page number further, using each part as an index into a table of indices to subsequent tables.

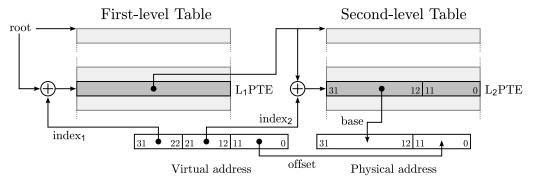

#### Two-level Page Table

To convert our one-level page table example from Section 3.2.1 into a two-level page table, we can divide the 20-bit page number into two 10-bit indices. Figure 3.3 shows the resulting lookup pattern: we use the first 10 bits as an index into the first-level table, obtaining an entry which may contain the address of the second-level table (or an indication that the corresponding memory area contains no mappings – typically an address of 0). Once we have the address of the second-level table, we use the second 10-bits of the page number as an index into that table to obtain the same kind of page table entry as we had in the single-level page table (frame number + flags).

**Figure 3.3:** A lookup in a two-level page table on a 32-bit machine with a 4KB page size with a 10-10 split on the page number.

The minimal memory use of such a page table is the size of first-level page table  $-2^{10}$  32-bit pointers to second-level tables, 4KB. Should all second-level tables be created, their combined size is identical to the size of a one-level page table. Thus, when fully populated, the overhead of a two-level page table over a one-level page table is the size of the first-level table, i.e. 4KB. As virtual memory usage is typically sparse, the two-level table yields a significant improvement in efficiency.

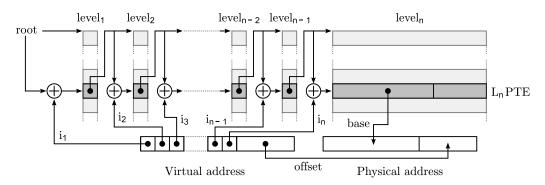

#### Many-level Page Table

For 32-bit systems a two-level page table is typical. Due to the efficiency issues we outlined, 64-bit systems require use of more levels.

**Figure 3.4:** A lookup in a multi-level page table. Intermediate levels not to scale.

By "many-level" we refer to page tables with more levels than the two-level ARMv6 page table which we formalise in Chapter 6. For 32-bit systems, two levels are sufficient. For 64-bit systems, four or even five-level tables may be used. Figure 3.4 shows how the extra levels are just a variation on a normal two-level page table, but with the page-number bits split into multiple page-table indices rather than just two.

#### Superpages

The two-level page table in Section 3.2.2 maps one 4KB page at a time. A first-level entry can point to a second-level table, which contains 1024 entries, each corresponding to a 4KB page. Thus, in total, one first-level entry is responsible for a 4MB block of virtual memory. By extracting a physical address and a "don't look further" tag at the first-level entry, we can map a 4MB block of virtual memory to a 4MB block of physical memory without the use of a second-level table. In general, we refer to such areas of memory, mapped using a larger-than-page granularity as *superpages*.