# An Analysis of the Effectiveness of Energy Management

### on Modern Computer Processors

# THE UNIVERSITY OF NEW SOUTH WALES

## SYDNEY·AUSTRALIA

### Master of Science

School of Computer Science and Engineering The University of New South Wales

Etienne Le Sueur

June 22, 2011

# Abstract

Managing energy consumption has become a critical issue for computer system designers. End-users are forced to charge battery-powered devices on a daily basis because battery technology has not kept pace with the demands of the power-hungry processors and peripherals used in today's mobile devices. Thousands of servers in data-centres also use power-hungry processors which result in huge costs for power and cooling. This is impacting our environment by accelerating global climate-change.

To help mitigate these problems, processor manufacturers have implemented various powermanagement mechanisms, including *dynamic voltage and frequency scaling* (DVFS) and low-power idle modes, to reduce and manage the power consumption of their processors. These mechanisms are controlled by the *operating system* (OS) and in the past, their use could result in significant improvements in energy efficiency. However, changes in semiconductor technology are altering the effectiveness of these mechanisms.

This thesis shows that on recent platforms, using DVFS results in only marginal reductions in systemlevel energy consumption for realistic workloads such as MPEG video playback. However, we find that the system-level energy consumption of lightly loaded web-servers can be reduced without impacting throughput or response latency. This results in an improvement in energy efficiency.

However, several trends exist which are leading to diminishing returns from traditional powermanagement mechanisms. We analyse these trends to determine their impact on the effectiveness of the energy-management techniques used in systems today, and look into the future to see what might help to reduce the energy consumption of the computer systems of tomorrow.

# Acknowledgements

Throughout the time spent working on this thesis I have had the opportunity to work with and learn from many of the brightest and most intelligent people I have ever known. My supervisor and the leader of the lab in which I spent most of my time, Gernot Heiser, deserves my utmost appreciation and thanks. Without his constant guidance and support, I would not have been able to complete this work. Furthermore, as the leader of the ERTOS group, I am constantly impressed at the level of enthusiasm and support that he gives to the group as a whole. My co-supervisor Peter Chubb also deserves my thanks for always being available to bounce ideas off.

I began as a research assistant working under Dave Snowdon on his PhD research. Much of the work in this thesis builds on the knowledge that I gathered during my time working with him. I take this opportunity to thank him for passing on some of his vast knowledge to me.

My fellow graduate students Aaron Carroll, Bernard Blackham and Godfrey van der Linden were also very much involved in my work and were always available to help me when I had a problem I didn't know how to solve.

My fiancé Romany was always willing to proof my writing before looming deadlines, which I greatly appreciate.

Numerous other people in the ERTOS lab have helped me over the last few years and I will take this opportunity to thank them as well.

# **Originality Statement**

I hereby declare that this submission is my own work and to the best of my knowledge it contains no materials previously published or written by another person, or substantial proportions of material which have been accepted for the award of any other degree or diploma at UNSW or any other educational institution, except where due acknowledgement is made in the thesis. Any contribution made to the research by others, with whom I have worked at UNSW or elsewhere, is explicitly acknowledged in the thesis. I also declare that the intellectual content of this thesis is the product of my own work, except to the extent that assistance from others in the project's design and conception or in style, presentation and linguistic expression is acknowledged.

Etienne Le Sueur, June 22, 2011

# Publications

**Slow Down or Sleep, That is the Question** Etienne Le Sueur and Gernot Heiser, *Proceedings of the 2011 Usenix Annual Technical Conference, Portland, Oregon, USA, June, 2011.*

**Dynamic Voltage and Frequency Scaling: The Laws of Diminishing Returns** Etienne Le Sueur and Gernot Heiser Proceedings of the 2010 Workshop on Power Aware Computing, HotPower'10, Vancouver, Canada, October, 2010

Koala: A Platform for OS-level Power Management David C. Snowdon, Etienne Le Sueur, Stefan M. Petters and Gernot Heiser *Proceedings of the 4th EuroSys Conference, Nuremberg, Germany, April, 2009*

viii

# Contents

| Ał | bstrac  | t       |                                              | i   |

|----|---------|---------|----------------------------------------------|-----|

| Ac | cknov   | vledger | nents                                        | iii |

| Pι | ıblica  | tions   |                                              | vii |

| Co | onten   | ts      |                                              | xi  |

| Li | st of I | Figures |                                              | xv  |

| Li | st of ' | Tables  |                                              | 0   |

| 1  | Intr    | oductio | on and Motivation                            | 2   |

|    | 1.1     | Resear  | rch Questions                                | 4   |

|    | 1.2     | Contri  | ibution                                      | 4   |

|    | 1.3     | Thesis  | Overview                                     | 4   |

| 2  | Bac     | kgroun  | d and Related Work                           | 6   |

|    | 2.1     | Introd  | luction                                      | 6   |

|    | 2.2     | Power   | Consumption Characteristics of Transistors   | 6   |

|    |         | 2.2.1   | Transistor scaling                           | 7   |

|    |         | 2.2.2   | Dynamic power dissipation in CMOS circuits   | 7   |

|    |         | 2.2.3   | Static power dissipation in CMOS circuits    | 9   |

|    | 2.3     | CPU P   | Power-management Mechanisms                  | 9   |

|    |         | 2.3.1   | Dynamic voltage and frequency scaling        | 10  |

|    |         | 2.3.2   | Idle states (C states)                       | 10  |

|    |         | 2.3.3   | Intel's power-management unit and TurboBoost | 12  |

|    |         | 2.3.4   | Dynamic cache resizing                       | 12  |

|    |         | 2.3.5   | Adaptive voltage scaling                     | 13  |

|    |         | 2.3.6   | Discussion                                   | 14  |

|    | 2.4     | Evalua  | ating Energy-management Techniques           | 14  |

|    |         | 2.4.1   | Measurement and run-time profiling           | 14  |

|    |         | 2.4.2   | Simulation and trace analysis                | 15  |

|   |     | 2.4.3 Modelling and accounting                                | 17 |

|---|-----|---------------------------------------------------------------|----|

|   |     | 2.4.4 System-level analysis                                   | 21 |

|   |     | 2.4.5 Scheduling on multi-core systems                        | 22 |

|   |     | 2.4.6 Discussion                                              | 23 |

|   | 2.5 | OS Energy Management                                          | 23 |

|   |     | 2.5.1 Research frameworks                                     | 23 |

|   |     | 2.5.2 Linux                                                   | 25 |

|   |     | 2.5.3 Discussion                                              | 27 |

| 3 | The | Impact of Memory Throughput                                   | 28 |

|   | 3.1 |                                                               | 28 |

|   | 3.2 | The Effects of Aggressive Prefetching                         | 30 |

|   | 3.3 | Modelling Workload Performance Under Varying CPU Frequency    | 31 |

|   |     | 3.3.1 Model characterisation                                  | 32 |

|   |     | 3.3.2 Developing a synthetic characterisation workload        | 34 |

|   |     | 3.3.3 Prefetching effects                                     | 35 |

|   | 3.4 | Memory Throughput and DVFS                                    | 39 |

|   | 3.5 | Conclusions                                                   | 40 |

|   | 5.5 |                                                               | 70 |

| 4 |     |                                                               | 42 |

|   |     | Introduction                                                  | 42 |

|   | 4.2 | Compute-intensive Workloads                                   | 43 |

|   |     | 4.2.1 Methodology                                             | 44 |

|   |     | 4.2.2 Results                                                 | 45 |

|   |     | 4.2.3 Discussion                                              | 45 |

|   | 4.3 | Padding with Idle-energy                                      | 46 |

|   |     | 4.3.1 Energy-delay product                                    | 46 |

|   |     | 4.3.2 C state overview                                        | 47 |

|   |     | 4.3.3 Padding with different C states                         | 51 |

|   |     | 4.3.4 Discussion                                              | 52 |

|   | 4.4 | Bursty/Periodic Workloads                                     | 52 |

|   |     | 4.4.1 Artificially introducing slack-time into SPEC workloads | 53 |

|   |     | 4.4.2 MPEG playback workload                                  | 56 |

|   |     | 4.4.3 Hardware acceleration of MPEG decode                    | 59 |

|   |     | 4.4.4 Web-server workload                                     | 59 |

|   |     | 4.4.5 Discussion                                              | 64 |

|   | 4.5 | Conclusions                                                   | 65 |

| 5 | The | Laws of Diminishing Returns                                   | 68 |

|   | 5.1 | Transistor Scaling                                            | 68 |

|   | 5.2 | Memory Performance                                            | 69 |

|   | 5.3 | Improved Idle Modes                                           | 70 |

|   | 5.4 | Asynchronously Clocked Caches                                 | 70 |

|    | 5.5          | Multi-core Processors                                      | 71 |  |

|----|--------------|------------------------------------------------------------|----|--|

|    | 5.6          | Conclusions                                                | 72 |  |

| 6  | Con          | clusions                                                   | 74 |  |

|    | 6.1          | Summary                                                    | 74 |  |

|    | 6.2          | The Future of CPU Power Management                         | 76 |  |

|    | 6.3          | Future Work                                                | 76 |  |

|    |              | 6.3.1 DVFS on hardware acceleration units                  | 76 |  |

|    |              | 6.3.2 Per-core DVFS                                        | 77 |  |

|    |              | 6.3.3 Modelling with improved performance counters         | 77 |  |

|    |              | 6.3.4 OS scheduler optimisation for improved C state usage | 77 |  |

|    | 6.4          | Conclusion                                                 | 78 |  |

| Gl | Glossary 8   |                                                            |    |  |

| Re | References 8 |                                                            |    |  |

# List of Figures

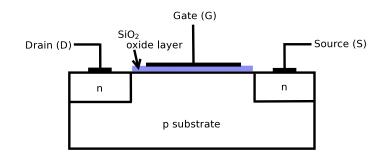

| 2.1 | High-level components forming an n-channel MOSFET                                                                                                                                                                                                                                                                            | 7  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

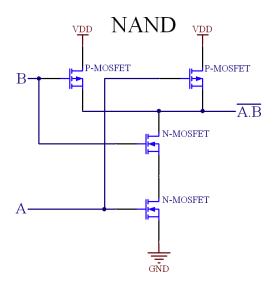

| 2.2 | Construction of a NAND gate from MOSFET devices.                                                                                                                                                                                                                                                                             | 8  |

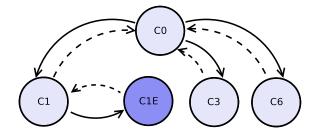

| 2.3 | Possible C state transitions for an Intel Core i7 processor. All transitions must go through C0, except to the special C1E state, entered when all cores enter C1                                                                                                                                                            | 11 |

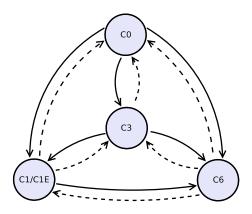

| 2.4 | Future generations of Intel processors will have automatic promotion/demotion of idle states, thus removing the requirement to transition through CO, minimising the number of wake-ups. Current generations are restricted to the state transitions shown in Figure 2.3.                                                    | 11 |

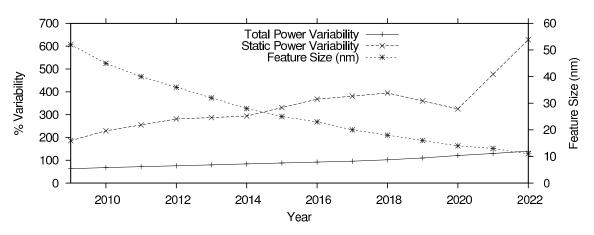

| 2.5 | Variability in semiconductor power consumption, as predicted by the ITRS                                                                                                                                                                                                                                                     | 13 |

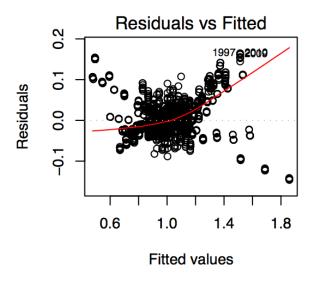

| 2.6 | Plot of model residuals against measured value for an execution time model with four parameters [R, 2011].                                                                                                                                                                                                                   | 20 |

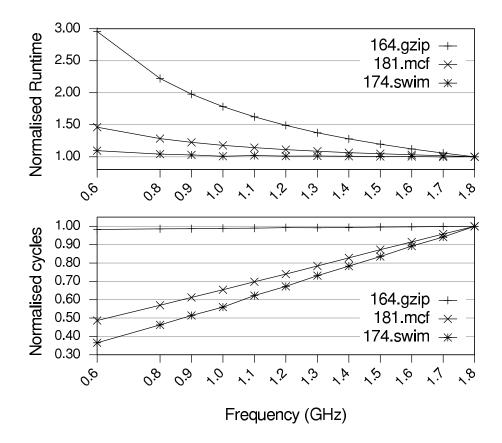

| 3.1 | Runtime vs. frequency (top) and CPU cycles vs. frequency (bottom) for several SPEC CPU2000 benchmarks on a Pentium-M. All values are normalised to the maximum frequency, 1.8 GHz.                                                                                                                                           | 29 |

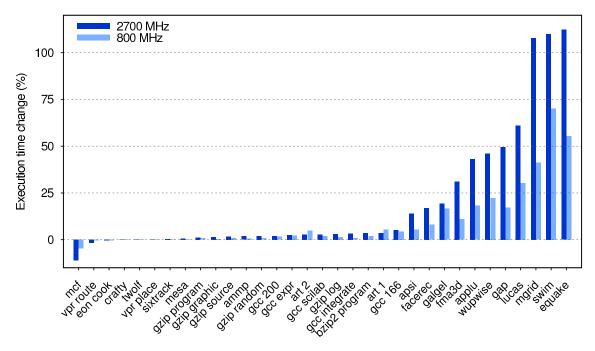

| 3.2 | Change in execution time of the SPEC CPU 2000 workloads on a recent AMD Opteron with prefetching <b>disabled</b> . Note that the performance of 181.mcf actually improves with prefetching disabled.                                                                                                                         | 30 |

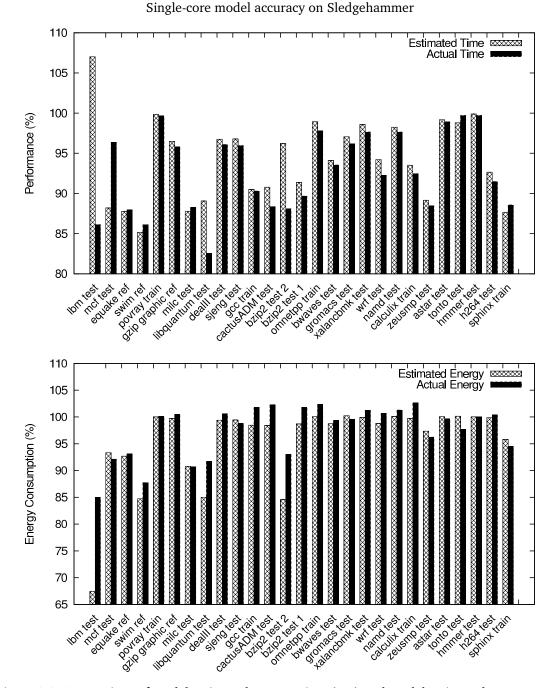

| 3.3 | Comparison of model estimated execute time (top) and model estimated energy consumption (bottom) on the Sledgehammer platform with a four-parameter model. Model accuracy is good for most benchmarks in the set, however <b>lbm_test</b> and <b>mcf_test</b> on the left have huge over- and under-estimations respectively | 33 |

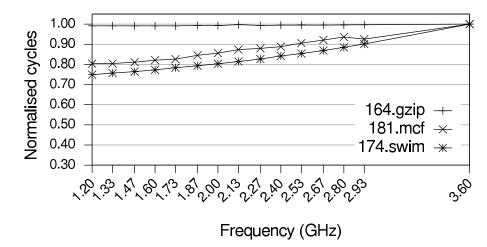

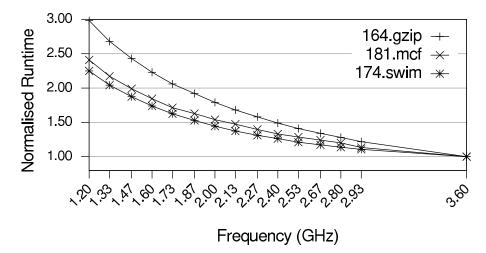

| 3.4 | Comparison of normalised cycle count vs. CPU frequency for several SPEC CPU2000 benchmarks on a more recent Core i7. 3.60 GHz represents a TurboBoost frequency, all values are normalised to this. Both <i>swim</i> and <i>mcf</i> show a non-linear relationship that is caused by hardware prefetching.                   | 35 |

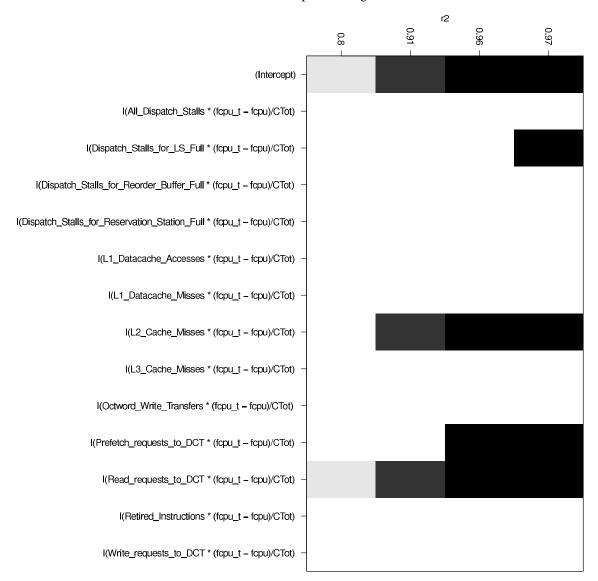

| 3.5 | This figure shows which parameters are selected for the time model when prefetching is <b>enabled</b> and their correlation coefficients. Each column represents a model with one more parameter included up to a maximum of 4 parameters. Y axis is $R^2$                                                                   | 36 |

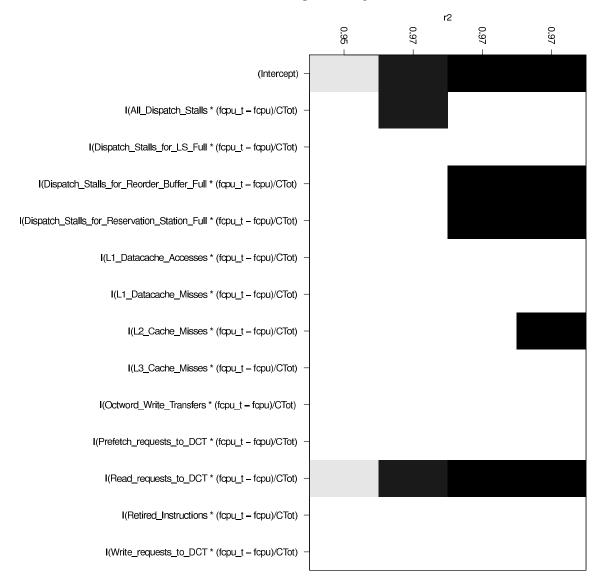

| 3.6  | This figure shows which parameters are selected for the time model when prefetching is <b>disabled</b> and their correlation coefficients. Each column represents a model with one more parameter included up to a maximum of 4 parameters. Y axis is $R^2$                                                                                                                                                                                    | 37 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.7  | Comparison of normalised runtime vs. CPU frequency for several SPEC CPU2000 benchmarks on the Core i7. 3.60 GHz represents a TurboBoost frequency, all values are normalised to this.                                                                                                                                                                                                                                                          | 39 |

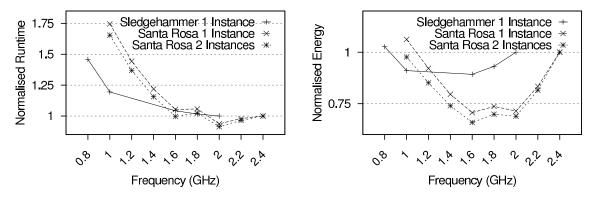

| 4.1  | Runtime (left) and energy consumption (right) of <i>mcf</i> on the Sledgehammer and Santa Rosa systems.                                                                                                                                                                                                                                                                                                                                        | 44 |

| 4.2  | Runtime (left) and energy consumption (right) of <i>mcf</i> on the Shanghai system                                                                                                                                                                                                                                                                                                                                                             | 45 |

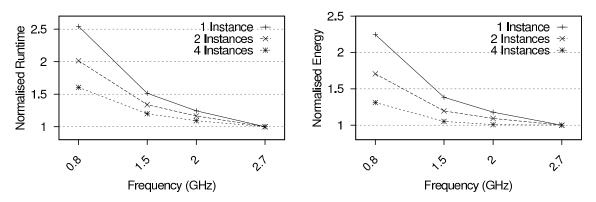

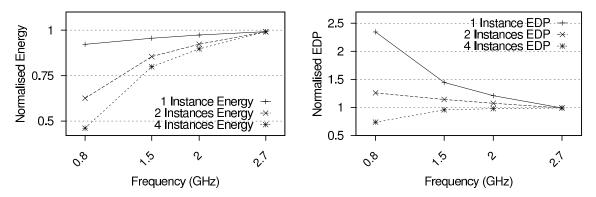

| 4.3  | Padded energy consumption for one, two and four instances of <i>mcf</i> on Shanghai (left) and padded energy-delay product (EDP) (right). All values are normalised to the maximum CPU frequency.                                                                                                                                                                                                                                              | 46 |

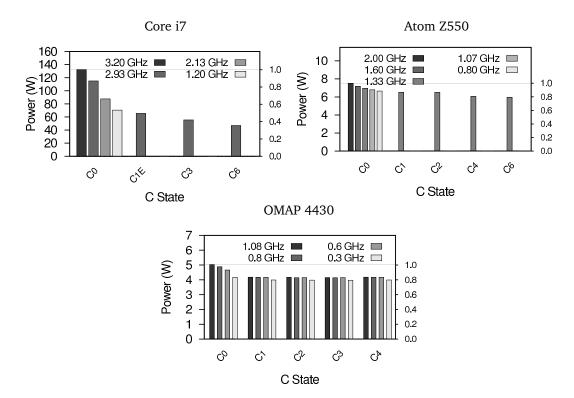

| 4.4  | Idle power consumption for the Core i7 (top left), Atom Z550 (top right) and OMAP 4430 (bottom middle) when all cores are put in the same state.                                                                                                                                                                                                                                                                                               | 49 |

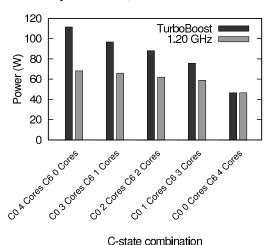

| 4.5  | Power draw of the Dell Vostro when only some of the cores of the Core i7 area placed<br>in C6. When all cores enter C6, the processor enters the <i>package</i> C6 state, achieving<br>even lower power draw.                                                                                                                                                                                                                                  | 50 |

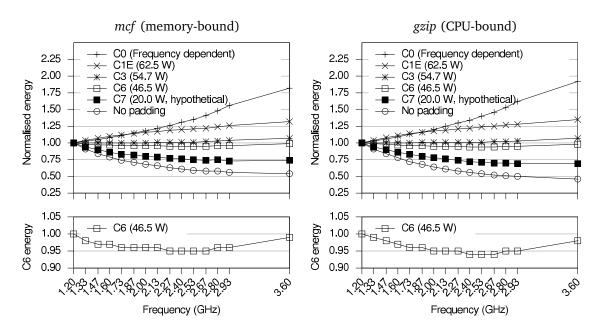

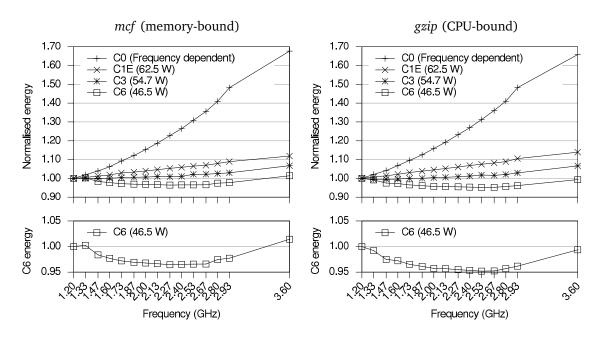

| 4.6  | Energy consumption for <i>mcf</i> (left) and <i>gzip</i> (right) when padded for idle energy with various C states for <i>mcf</i> on the Core i7. This approach assumes a single idle state transition at benchmark completion. Data shown is normalised to the minimum frequency. 3.60 GHz is a TurboBoost frequency. The zoomed section shows that using C6, energy efficiency can be improved by up to 5 % if the CPU frequency is reduced. | 51 |

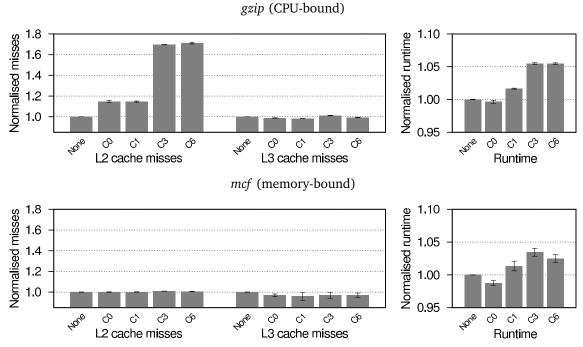

| 4.7  | Costs associated with transition between C0 and deeper C states every 10 ms for two SPEC workloads, <i>mcf</i> (memory-bound, bottom) and <i>gzip</i> (CPU-bound, top) on the Core i7.                                                                                                                                                                                                                                                         | 53 |

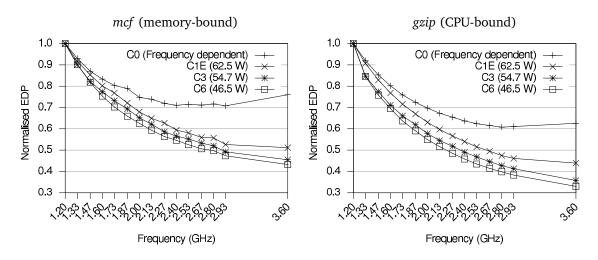

| 4.8  | Energy consumption for <i>mcf</i> (left) and <i>gzip</i> (right) on the Core i7. In contrast to Figure 4.6, this data includes costs for idle state transitions every 10 ms. Data shown has been normalised to the minimum frequency. 3.60 GHz is a TurboBoost frequency. The zoomed section shows that using C6, energy efficiency can be improved by up to 5 % if the CPU frequency is reduced.                                              | 55 |

| 4.9  | EDP for <i>mcf</i> (left) and <i>gzip</i> (right) on the Core i7 when slack time is introduced at 10 ms intervals. Data shown has been normalised to the minimum frequency. 3.60 GHz is a TurboBoost frequency.                                                                                                                                                                                                                                | 56 |

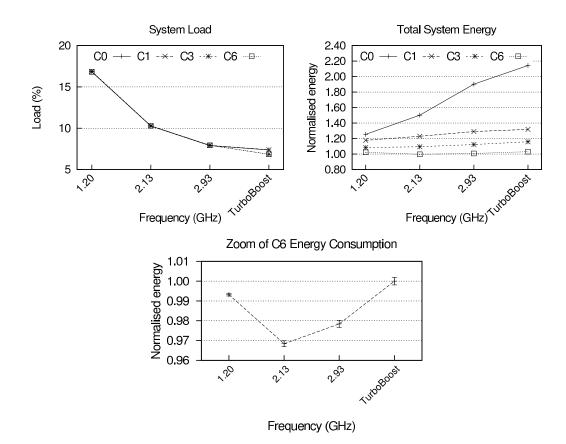

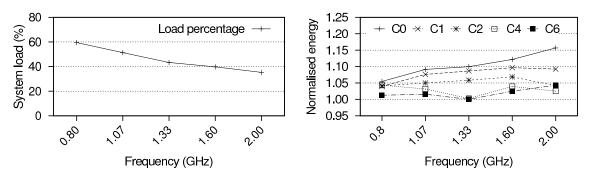

| 4.10 | System load (top left) and normalised energy consumption (top right) for playback<br>of a high-definition MPEG video stream on the Core i7 under various frequencies.<br>Energy data has been normalised to 2.13 GHz using C6, which was the case where<br>minimum energy consumption was observed. The bottom graph shows a zoomed<br>version of the C6 line in which the data has been normalised to the TurboBoost point.                   | 57 |

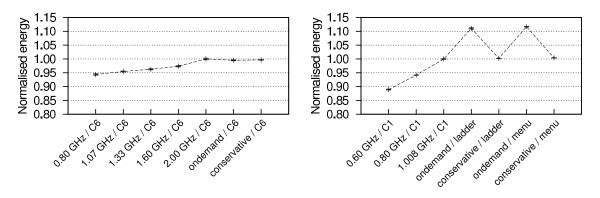

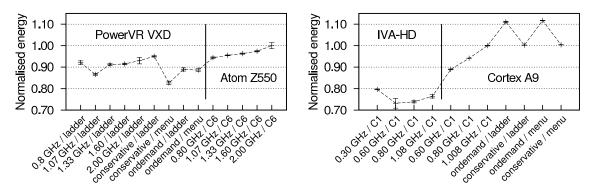

| 4.11 | 1 Left: Energy consumption for playback of an MPEG video stream on the <b>fitPC</b> (Atom) |    |

|------|--------------------------------------------------------------------------------------------|----|

|      | when the C6 C state is used. Values are normalised to the 2.00 GHz / C6 point. Right:      |    |

|      | Energy consumption for playback of an MPEG video stream on the Pandaboard                  |    |

|      | (OMAP4430). Values are normalised to the 1.008 GHz / C1 point                              | 58 |

| 4.12 | 2 Left: Energy consumption for playback of an MPEG video stream on the fitPC               |    |

|      | (Atom Z550) when the PowerVR VXD MPEG decode unit is leveraged. Right: Energy              |    |

|      | consumption for playback of an MPEG video stream on the <b>Pandaboard</b> (OMAP4430)       |    |

|      | when the IVA-HD MPEG decode unit is leveraged                                              | 59 |

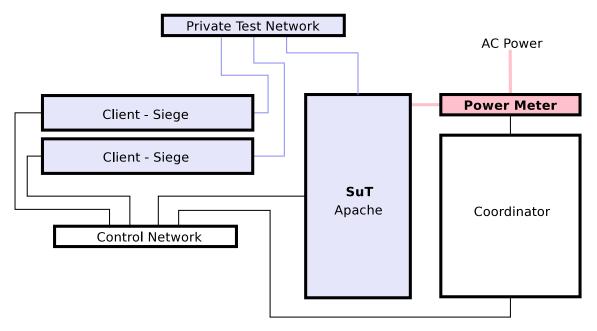

| 4.13 | 3 Topology of systems and network for the web-server benchmarks                            | 60 |

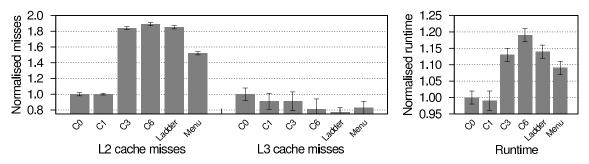

| 4.14 | 4 Overhead in L2 and L3 misses and runtime for different C states for the Apache           |    |

|      | web-server workload on the Core i7 at 2.93 GHz. All values are normalised to the CO        |    |

|      | C state.                                                                                   | 61 |

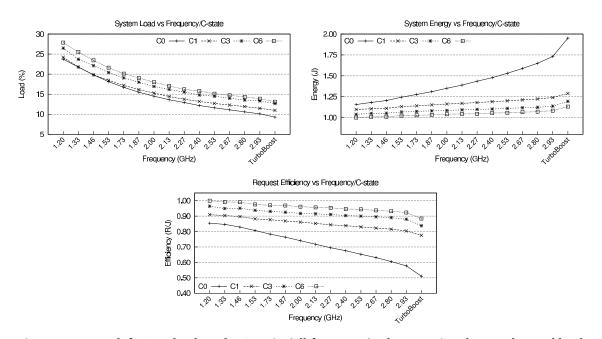

| 4.15 | 5 Top left: CPU load on the Core i7 (all four cores) when running the Apache workload      |    |

|      | under DVFS. Top right: System-level energy consumption of the Core i7 running              |    |

|      | the Apache web-server workload. All energy values are normalised to the lowest             |    |

|      | observed energy consumption at 1.20 GHz / C6. Since Apache is a multi-threaded             |    |

|      | workload, the TurboBoost frequency varies between 2.93-3.60 GHz. Bottom centre:            |    |

|      | request efficiency in requests per unit energy, normalised to again to 1.20 GHz / C6.      | 62 |

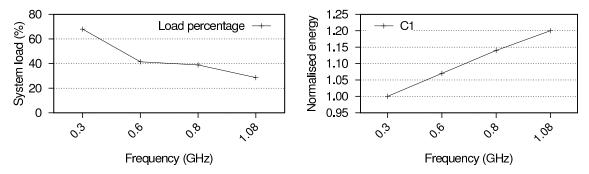

| 4.16 | 5 System load (left) and energy consumption (right) of the fitPC (Atom) when running       |    |

|      | the Apache web-server workload. Energy consumption values have been normalised             |    |

|      | to the minimum value observed at 1.33 GHz with C6                                          | 63 |

| 4.17 | 7 System load (left) and energy consumption (right) for the Pandaboard (OMAP4430)          |    |

|      | when running the Apache web-server workload. Energy consumption values have                |    |

|      | been normalised to the minimum value observed at 0.3 GHz                                   | 64 |

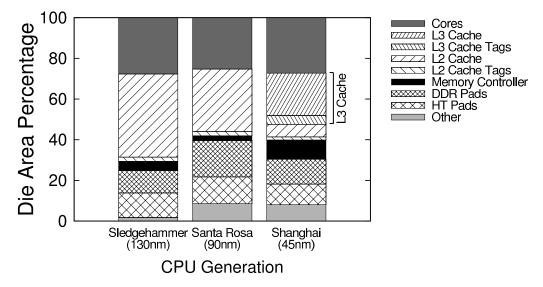

| 5.1  | Die area breakdown of three generations of Opteron processors                              | 71 |

|      |                                                                                            |    |

# List of Tables

| 3.1 | Specifications of the two systems we analyse for the impact of memory throughput.     | 40 |

|-----|---------------------------------------------------------------------------------------|----|

| 4.1 | Specifications of the three AMD Opteron processors and systems we analyse for the     |    |

|     | compute-intensive workloads. All systems have a single CPU package                    | 43 |

| 4.2 | Specifications of the three processors and systems we analyse for the idling workload |    |

|     | scenarios                                                                             | 47 |

| 4.3 | Characteristics of the different C states on the three test systems. On the OMAP,     |    |

|     | C states greater than C1 could only be used if the second core was disabled           | 48 |

# Chapter 1

# Introduction and Motivation

Energy consumption has become a critical issue for most computing platforms. Previously, efficient use of energy resources was a concern only for battery-powered devices, such as mobile phones and laptops. However, it has now become a critical design constraint for *all* classes of systems. For example, a report to the California Energy Commission found that the power required for cooling and infrastructure in California data-centres can be over 50 % of the total electrical load [Tschudi et al., 2004].

A large proportion of the energy consumed by computer systems is spent powering the *central processing-unit* (CPU). In a data-centre, the heat generated by the CPU must be removed by air-conditioning requiring even more energy. To help to reduce CPU energy consumption, manufacturers have implemented various mechanisms for managing the power consumption of their processors. Some of these mechanisms allow the *operating system* (OS) to trade performance for lower power use, while others allow the OS to place the processor in various deep *sleep states* with increasingly reduced power consumption coupled with longer latencies to wake up from sleep.

One such mechanism, *dynamic voltage and frequency scaling* (DVFS), allows the OS to reduce the frequency (and performance) of the CPU and thereby lower its power consumption. Much prior research on improving the energy efficiency of computing systems has focused on DVFS, producing a number of techniques that can be employed by the OS [Weiser et al., 1994].

Data-centres contain thousands of servers which consume vast amounts of electricity for supply and cooling. However, studies performed by Google show that many of those servers spend most of the time significantly under-utilised [Barroso and Hölzle, 2007]. Hence, some studies suggest that reducing the CPU's frequency may improve energy efficiency.

Furthermore, as battery-constrained embedded systems continue to grow in performance and ubiquity, the issue of energy efficiency is becoming even more important. As a result, new powermanagement mechanisms, such as low-power idle modes and specialised hardware acceleration units, are being introduced into embedded processors in order to help improve their energy efficiency and prolong battery life.

The energy efficiency of computer systems can be optimised using DVFS and sleep states. However, they are competing mechanisms. On the one hand, the CPU can be run at its highest frequency (with high power consumption) in order to complete work in the shortest time. Once the work is completed, the CPU can then go into a deep sleep state, reducing power consumption. This approach is referred to as *race-to-halt*. On the other hand, the CPU can be slowed down using DVFS, spend a longer time active, but have its power consumption reduced during this period. This approach reduces the time the processor can spend in deep sleep states.

To determine which of these approaches is best for a particular system, it is necessary to understand how the performance of the CPU's *workload* is going to respond to a change in CPU frequency. Prior research has addressed this issue by applying mathematical modelling techniques to try to predict how much performance will be lost when the CPU frequency is decreased [Snowdon, 2010]. These modelling techniques have also been used to predict the power drawn by a processor at different frequencies. When these two predictions are combined, the energy used by a processor executing some workload at different frequencies can be estimated and a decision can be made about which frequency should be used to provide optimal energy efficiency.

In the mid 1990s, Mark Weiser performed trace-based simulations of OS scheduler invocations in order to determine whether a CPU could be slowed down to reduce its energy consumption when the system was not fully utilised. His conclusion was:

To put it simply, the tortoise is more efficient than the hare: it is better to spread work out by reducing cycle time (and voltage) than to run the CPU at full speed for short bursts and then idle [Weiser et al., 1994].

More recently, Snowdon et al. and others, have shown that systems based on processors such as the Intel XScale PXA255 and Intel Pentium-M could achieve higher energy efficiency by reducing the CPU's frequency with DVFS when certain workloads were detected [Snowdon et al., 2009; Weissel and Bellosa, 2002].

However, our research suggests that several trends, such as:

- the scaling of silicon transistor feature sizes,

- increasing memory performance,

- improved sleep/idle modes,

- asynchronously clocked caches and memory-controllers, and

- the complexity of multi-core processors

are reducing the effectiveness of traditional power-management mechanisms such as DVFS in all classes of platforms.

This thesis shows that the above trends are indeed causing DVFS to become less effective and, in some cases, even reducing energy efficiency instead of improving it. However, the effectiveness of DVFS is critically workload dependent. Therefore, we aim to cover a wide range of workload and platform classes to determine if this finding is recurrent.

### 1.1 Research Questions

In short, we aim to answer the following questions:

- 1. Are Mark Weiser's claims set in stone—can energy efficiency still be improved by using DVFS to slow down the processor?

- 2. What factors influence the effectiveness of DVFS?

- 3. How much energy can be saved by using hardware acceleration units instead of the standard, general-purpose applications processor?

### 1.2 Contribution

Past studies have leveraged the DVFS mechanism to improve the energy efficiency of computer systems, however few have acknowledged the trends that contribute to its decreasing effectiveness. This thesis critically analyses the effectiveness of DVFS on recent computer systems, ranging from server- to mobile-class systems and shows that use of DVFS has become questionable. We introduce and analyse five trends which we believe are the root causes of the diminishing returns from DVFS.

### 1.3 Thesis Overview

This thesis is structured as follows:

**Chapter 2** provides an overview of power-management mechanisms on modern processors and an analysis of prior work in the research area.

**Chapter 3** discusses the impact of memory throughput on the effectiveness of DVFS and our attempt to model the performance of a recent multi-core processor under DVFS.

**Chapter 4** addresses the question: *slow down or go to sleep*? by looking at several workload types on a range of platforms.

Chapter 5 outlines the trends that are contributing to the diminishing returns of DVFS; and

Chapter 6 suggests future directions for power-management research.

# Chapter 2

# Background and Related Work

### 2.1 Introduction

This chapter begins by briefly discussing basic transistor theory to enable the reader to better understand the analyses in the following chapters. Section 2.3 provides an overview of power-management mechanisms that are available on modern CPUs. Section 2.4 discusses how power-management mechanisms are used and evaluates several software techniques that make use of these mechanisms. Section 2.5 provides an overview of several frameworks that have been developed for OSes, including those that *Linux* currently uses to leverage the mechanisms available on modern CPUs.

### 2.2 Power Consumption Characteristics of Transistors

Transistors form the basis of all modern digital systems based on integrated circuits. Today, a computer processor can be made up of millions, or even billions of transistors.

Contemporary CPUs are implemented with a technology called *complementary metal-oxide semiconductor* (CMOS) which uses transistors called metal-oxide semiconductor field-effect transistors (MOSFETs). There are two types of MOSFET, n-channel and p-channel. Their construction is differentiated by using different types of semiconductor material for the transistor's features. MOSFETs are composed of two silicon junctions on a substrate, as shown in Figure 2.1. The *gate* (G) forms a capacitor which, when a voltage is applied, will charge. It is insulated from the substrate by an oxide layer, which means that very little current will flow through the gate. Upon charging, a conduction channel will form between the *source* (S) and the *drain* (D) due to electric fields induced in the substrate. If the voltage is above the *threshold voltage*,  $V_t$ , current can flow from source to drain.

Figure 2.1: High-level components forming an n-channel MOSFET. [see Floyd, 1984, Chapter 9, Section 9-3]

The power dissipation of CMOS integrated circuits is composed of both static and dynamic components. Static power dissipation arises from leakage and transistor bias currents, while dynamic power dissipation is due to the charge/discharge of capacitances and other switching activity in the circuit.

#### 2.2.1 Transistor scaling

The size of the components in a transistor (e.g. the gate, source and drain), called the *feature size*, is determined by the manufacturing process. This is essentially a measure of the distance between the source and drain. In the early 1990's, the feature size was approximately  $250 \mu$ m. However, over time, processor manufacturers have worked to build smaller transistors because they can switch at a faster rate, and consume less power. Following *Moore's Law*, which dictates how often processors are released with a smaller feature size, this has lead to recent processors being manufactured from transistors with a feature-size of 32 nm. The *international technology roadmap for semiconductors* (ITRS) working group predicts that transistor feature-size will be as small as 9 nm within the next twelve years [ITRS, 2009].

Feature size is a critical characteristic for energy consumption for several reasons. Firstly, smaller transistors can operate at lower voltages and have reduced gate capacitance, which reduces dynamic power dissipation (explained in the next section). Secondly, as feature-size is scaled down, static leakage power *rises* exponentially (explained in Section 2.2.3).

#### 2.2.2 Dynamic power dissipation in CMOS circuits

CMOS logic gates, such as the NAND gate shown in Figure 2.2, are constructed from complementary pairs of n-channel and p-channel MOSFETs. The combination is such that in a steady state, one of the pair is in the off state, meaning that no current flows other than leakage current (explained in the next section). When one of the gate's inputs (A or B) switches, some time later, the output of the gate will settle on the result, and the next logic gate in the circuit may then transition based on its new inputs. A processor is made up of thousands of these logic gates which form functional units

Figure 2.2: Construction of a NAND gate from MOSFET devices. [see Mano and Kime, 1997, Chapter 2, Section 9]

such as integer or floating point units. These functional units are synchronised with a global clock, operating at the frequency of the processor.

The dynamic power drawn by a processor is made up of two components. Firstly, when switching occurs on a gate input, the two complementary MOSFETs are momentarily in a partial conduction mode, allowing *short-circuit* current to flow. Secondly, as the gates of MOSFETs form capacitors, there are energy costs associated with their charge and discharge due to

$$E = \frac{1}{2}CV^2 \tag{2.1}$$

where E is the energy stored in the capacitor, C is the capacitance in Farads, and V is the voltage that is applied to the FET's gate. As a transistor is scaled to a smaller feature size, the physical size of the gate is reduced, resulting in a reduction in its capacitance. Furthermore, as a smaller feature size allows reduced supply voltage, short-circuit current is also reduced. Hence, the total *dynamic* power drawn by a CMOS device is related to these characteristics:

$$P = \alpha C f V^2, \tag{2.2}$$

where P is the dynamic power consumption of the circuit (or processor), C is sum of the capacitance of the transistor gates (determined by the feature size), V is the supply voltage and f is the frequency at which the circuit is being clocked. The  $\alpha$  value represents the level of switching activity in the circuit, because not all transistors will switch every clock cycle. For stable operation at a particular frequency, the supply voltage must be high enough such that the gate of each transistor in the circuit has enough time to charge to above the threshold voltage. Hence, if the frequency is reduced, the voltage can also be reduced, resulting in a reduction in the power drawn.

### 2.2.3 Static power dissipation in CMOS circuits

Several factors contribute to the total static power consumption of a processor. Of these, the most substantial is *weak-inversion* (or sub-threshold) leakage current that flows from the drain to the source of each transistor, regardless of the state of the transistor. As feature size gets smaller, through the process of transistor scaling, the weak-inversion leakage current increases exponentially as

$$I_D \approx I_{D0} e^{\frac{V_{GS} - V_{th}}{nV_T}} \tag{2.3}$$

where  $I_D$  is the leakage current of a single transistor,  $V_{GS}$  is the gate–source voltage,  $I_{D0}$  is the leakage current when  $V_{GS} = V_{th}$ , n is a factor determined by feature-size and  $V_T$  is the *thermal* voltage, which depends on the temperature of the transistor.

Because of the exponential relationship between sub-threshold leakage and feature-size, in recent processors, static power dissipation contributes significantly to the total power consumption.

In the past, static power consumption has been small in comparison to dynamic power [Burd and Brodersen, 1995]. However, other factors contributing to leakage, including quantum effects such as gate-oxide layer tunnelling, are becoming increasingly important with shrinking feature size. Roy et al. discuss these and techniques for their mitigation [Roy et al., 2003].

Scaling of silicon transistor technology will slow at some point in the future due to the constraints of atomic dimensions. However, this will not happen before static power consumption (due to leakage current) rises well above dynamic switching power.

### 2.3 CPU Power-management Mechanisms

With the increasing importance of managed power consumption, modern CPUs have evolved to include numerous power-management mechanisms, some of which allow the OS to trade performance for reduced power consumption. Here, we describe the most common mechanisms and how they have been used in prior research.

### 2.3.1 Dynamic voltage and frequency scaling

DVFS is a mechanism that is available on most modern processors. It allows the core operating frequency of the CPU to be decreased allowing a corresponding reduction in the supply voltage, as per the relationship in Equation 2.2. This reduces the power drawn due to both dynamic and static components. Furthermore, temperature variation (due to varying heat dissipation or ambient temperature) can cause static power consumption to vary due to the dependence of sub-threshold leakage current on temperature as shown in Equation 2.3.

DVFS has the potential to not only reduce power draw, but also to improve energy efficiency. As will be explained in Chapter 3, some workloads respond differently to changes in CPU frequency. For some, performance scales linearly with frequency, while for others, performance scales sub-linearly and energy efficiency may improve with reduced CPU frequency.

A frequency change is not instantaneous—two steps are required, their order depending on whether the frequency is being increased or decreased. For stable operation, supply voltage must be increased to run at a higher frequency. Therefore, if a frequency increase is requested, the supply voltage must be *ramped* up to the value required to run at the requested frequency. After the supply voltage settles, the *phase-locked loop* (PLL) that generates the clock signal can be *relocked* to the new frequency. If a frequency decrease is requested, the PLL is relocked first, and then the supply voltage is ramped down. The combined latency for these steps is of the order of  $10-100 \mu$ s, depending mostly on the supply voltage change that is required.

This mechanism has been studied at length in the literature, and, in the past, its use has achieved significant improvements in energy efficiency, allowing battery-powered devices to last longer. Its use has been less pervasive in the data-centre mostly due to the perceived increase in latencies and reduction in *quality-of-service* (QoS) resulting from frequency changes.

Studies using DVFS are discussed in more detail in Section 2.4. In Chapter 3 and 4, we show that DVFS is becoming much less effective at improving energy efficiency. Indeed, we show that its use sometimes negatively impacts energy usage.

### 2.3.2 Idle states (C states)

A CPU can be thought of in terms of a *package*, *cores* and *threads*. A package can consist of multiple cores and a core can have one or two thread *contexts* which Intel has called *HyperThreads*.

When the OS has no tasks to schedule on a core, it will usually invoke the *idle thread* and parts of processor can be put into an *idle state* (or C state). As this thread does no useful work, it makes sense to put the CPU to sleep.

Modern CPUs tend to offer multiple C states, denoted by Cx where x is a number from 0 to some maximum. Higher x values yield a *deeper* idle state, resulting in lower power consumption, but

Figure 2.3: Possible C state transitions for an Intel Core i7 processor. All transitions must go through C0, except to the special C1E state, entered when all cores enter C1.

Figure 2.4: Future generations of Intel processors will have automatic promotion/demotion of idle states, thus removing the requirement to transition through C0, minimising the number of wake-ups. Current generations are restricted to the state transitions shown in Figure 2.3.

higher entry and exit latencies. Intel defines C states at the thread, core and package level, with C0 being the operating state in which a core is executing instructions. However, other manufacturers do not provide specifications for C states, allowing OS designers to choose the steps taken when entering different C states.

Because a single processor can have multiple cores and multiple hardware thread contexts (Hyper-Threads), constraints exist between thread, core and package idle states, for example, a *package* C state will not be entered unless all *cores* enter the same C state. There are also constraints on state transitions, as shown in Figure 2.3 for the Core i7 processor, where all transitions between C states must go through the active state, C0. The C1E state is a special exception, which is entered automatically when all cores enter C1.

Some C states are entered automatically, by the processor *promoting* an OS request to transition from a particular C state to a deeper C state. This includes the C1E state on Intel processors, and the C5 state on the Atom Z550, which are described in Section 4.3.2.

Future generations of Intel processors will also include a feature called C state *auto-demotion* where, depending on C state residency history (recorded by the processor), a request by the OS to enter an idle state will be automatically demoted to a lower level (lighter sleep) to minimise the negative effects of high-frequency C state transitions, resulting from naïve use. This is shown in Figure 2.4.

C states are discussed in greater detail in Chapter 4.

#### 2.3.3 Intel's power-management unit and TurboBoost

Intel's power-management unit, not to be confused with the performance-monitoring unit, was introduced with the Nehalem architecture in 2008. This unit monitors the temperature and power requirements of the processor and determines when TurboBoost (described below) is initiated and when idle state requests can be promoted and should be demoted. This requires that the processor be instrumented with current, voltage and temperature sensors at various points on the die. Unfortunately, the measurements taken using these sensors are not accessible by the OS. Snowdon and Esmaeilzadeh et al. suggest that manufacturers should expose these measurements to the OS. This way, software developers can benefit from the knowledge and insight that they provide about how energy is consumed in computer systems [Snowdon, 2010; Esmaeilzadeh et al., 2011].

Recent Intel processors based on both the Nehalem and Sandy Bridge micro-architectures have a feature called *TurboBoost*. If one or more of a processors' cores are powered down into a deep idle state, the clock frequency of other active cores can be boosted above the rated nominal frequency. For example, the Intel Core i7 870 has a nominal rated frequency of 2.93 GHz. However, if one or more cores are sleeping, the frequency of the remaining active cores can be increased. If multiple cores are active, their frequencies may be increased to up to 3.2 GHz, depending on power draw and thermal load. If only one core is active, its frequency can be increased to 3.6 GHz. This can give performance improvements for single-threaded workloads.

Charles et al. perform an analysis of this feature using SPEC CPU2006 on a 3.2 GHz Core i7-based system and find that TurboBoost provides, on average, a 6% improvement in performance [Charles et al., 2009]. However, they predict that this would be coupled with an average 16% increase in energy consumption by the CPU. This increase in energy consumption is predicted using a simple model for the *dynamic* power consumption of their processor based on Equation 2.2, hence it does not account for energy consumed because of static leakage power in the processor or energy consumed by the rest of the system.

Unfortunately, the TurboBoost feature is controlled entirely in hardware by the power-management unit. The OS has only the ability to enable or disable it. Scheduling policies could be developed to allow single-threaded workloads to take advantage of TurboBoost at the cost of forcing other cores to sleep, however this is not the focus of this thesis.

#### 2.3.4 Dynamic cache resizing

Caches contribute a large proportion of total processor power, as they require vast amounts of transistors and processor die area, adding to static power draw. To address this issue, some processors implement a dynamically resizable *last-level cache* (LLC). Using this mechanism, static

Figure 2.5: Variability in semiconductor power consumption, as predicted by the ITRS. [ITRS, 2009]

leakage power can be reduced when the entire cache is not required. Intel implements this feature with some of its mobile processors, such as the Atom.

Control of dynamic cache resizing is handled by the processor, however the OS can influence some decisions by changing thresholds, such as the CPU frequency below which cache resizing will be applied. Additionally, the OS can give *hints* to the processor when entering deep idle states suggesting that the cache should be resized.

#### 2.3.5 Adaptive voltage scaling

The manufacturing techniques used to create processors cause variability in the transistor threshold voltages across supposedly identical devices. For this reason, at manufacture time, processors are tested to determine the voltage required to run at their rated frequency. The ITRS predicts that variability in static power consumption will increase dramatically over the next decade as feature sizes become smaller, as shown in Figure 2.5. Wanner et al. perform a study to measure how sleep (static) power varies in embedded processors which are supposed to be identical parts. They find that the variation in static power at room temperature can be as much as 500 % [Wanner et al., 2010].

At run time, temperature variation (due to power dissipation and external effects) causes the threshold voltage of the transistors to change. Adaptive voltage scaling (AVS) tunes the supply voltage to improve energy efficiency under this temperature variation. The OMAP 4430 processor (which is analysed in Chapter 4) implements AVS by the way of its SmartReflex mechanism [Brian Carlson and Bill Giolma, 2008]. However, like TurboBoost, the OS has little control over this feature. As a result we have not analysed it in detail.

### 2.3.6 Discussion

Manufacturers have implemented numerous mechanisms both to reduce processor power consumption when compute resources are not needed and allow to OS developers to design algorithms to trade power for performance. However, it is not immediately obvious that using these mechanisms will improve energy efficiency. Therefore, analysis should be undertaken before they are used for a practical purpose. This thesis focuses our analysis on DVFS and idle state usage as these mechanisms create the most interesting dynamic trade-offs. The other mechanisms discussed are usually simply enabled or disabled.

### 2.4 Evaluating Energy-management Techniques

OS developers are able to interact with the low-level hardware and have the ability to use the power-management mechanisms that processor manufacturers implement. In order to evaluate the effectiveness of a software power-management technique, the system being tested needs to be instrumented or modeled in some way. Because computers are complex systems, it is often difficult to analyse exactly where and how energy is used. This section discusses some methods that have been developed to use the available power-management mechanisms described above and evaluates their effectiveness.

#### 2.4.1 Measurement and run-time profiling

Power consumption can be measured at various points in the system, resulting in measurements with different meanings. For example, the power lines leading directly into the CPU package can be instrumented, giving the power consumed only by the CPU [Esmaeilzadeh et al., 2011]. Alternatively, power consumption can be measured at the power supply, giving the total power consumed by the system and all of its peripherals.

Flinn and Satyanarayanan developed *PowerScope*, a tool to provide feedback to the developer about the energy consumption characteristics of their code [Flinn and Satyanarayanan, 1999]. The *system under test* (SuT) is instrumented with power-measurement apparatus and a separate system is used to record the data. Each time the measurements are sampled, the SuT is interrupted and the interrupt handler routine records the program counter and details of the currently running process. The data can be analysed at a later time to determine the energy efficiency of specific code sequences.

Most modern CPUs have a *performance-monitoring unit* (PMU), which enables online measurement of often hundreds of different events. The PMU consists of several configurable registers which count architectural events, such as cache-misses, unhalted CPU cycles, dispatch stalls, etc. These *performance-counter events* provide information about the performance of code running on the CPU, helping to fine-tune and debug programs. They can also be used as parameters in models for estimation of power consumption and execution time.

Isci and Martonosi instrumented a Pentium-4-based system with a power meter and used the processor's PMU to determine the power consumed by individual functional-units within the processor [Isci and Martonosi, 2003]. The Pentium 4's *Netburst* architecture provides 18 hardware performance-counter registers allowing simultaneous measurement of up to 18 events. In contrast, processors based on Intel's more recent Pentium M, Core and Nehalem architectures can measure only two events simultaneously. Isci and Martonosi validate their model using SPEC CPU2000 benchmarks and report an average absolute error of 2 W, and a maximum error of 5.8 W. After interpreting the figures, this would seem to be about 4 % and 12 % error respectively. They also perform several real-world desktop workload benchmarks such as browsing web-pages and using a spreadsheet, but do not report specific results from these.

Measurement at run time is a concrete method to ensure that accurate data is obtained, however the situations in which most systems are deployed limit the feasibility of this approach. Profiling is useful to obtain accurate results while software systems are in development and testing phases, but when they are deployed on systems that differ from those used during testing, accurate results cannot be ensured. Processor manufacturers are starting to include power-measurement apparatus on the processor die, for example Intel's power-management unit includes current, temperature and voltage measurement sensors. However, at this point in time, these measurements are not made available to the user. If designing custom hardware, as is often the case for embedded systems, including power-measurement sensors is not difficult. The OpenMoko Freerunner, analysed by Carroll and Heiser, has component locations for sense-resistors on the main PCB, allowing individual sub-components, such as CPU and memory to be measured individually [Carroll and Heiser, 2010]. However, to achieve this, external data acquisition hardware was required. The *PLEB2*, a custom-designed, education oriented, embedded system included a separate micro-controller and sense-resistors to allow power measurement of several subsystems at run time and thereby enable energy-use profiling and online optimisation [Snowdon and Johnson, 2003].

#### 2.4.2 Simulation and trace analysis

Simulation is a technique where a model of a system is developed and used to determine how a real system would react to changes in certain characteristics. Often to achieve this, a *trace* of a real system is recorded and then used (or *played back*) within the simulator to ensure that it remains coupled to reality. This technique can also allow comparison to ideal situations in which the real system lacks some information that a trace-based simulation can access (usually because that information is the result of a future decision). However, this can lead to the development of systems that rely too much on unrealistic, ideal models.

Brooks et al. modify *Turandot*, a cycle-accurate simulator for IBM POWER 4 processors to integrate *PowerTimer*, which provides a model for the power consumption of low-level functional units within

the CPU [Brooks et al., 2003]. They use the simulator and models to predict the effects of various architectural modifications on energy efficiency, for example, they find that when increasing the size of the L1 data cache, the performance improvements from lower miss rates are shadowed by a large increase in power consumption. Simulation at this level can be used to make informed decisions about which architectural features are important when designing new processors.

Isci et al. use Brooks' PowerTimer framework to analyse the effects of global versus per-core DVFS on a *chip multi-processor* (CMP) for SPEC CPU workloads. They found that with a global view of the tasks running on a CMP, they could better constrain the power consumption of the chip as a whole, while maintaining performance at a suitable level [Isci et al., 2006].

In 1994, Weiser et al. introduced the idea of varying the CPU frequency using DVFS based on the system load to optimise energy efficiency [Weiser et al., 1994]. He used a trace-based simulation to analyse the effects of changing CPU frequency at OS scheduler invocations on system energy consumption. A variant of this technique is now widely used, including in mainstream Linux which we described in Section 2.5.2.

Grunwald et al. performed an analysis technique developed by Weiser et el. to determine if it could be applied to real devices and workloads [Grunwald et al., 2000]. They used workloads such as MPEG playback and serving web-pages on a device with a Strong ARM SA-1100 processor. However, they were disappointed by the lack of energy savings that DVFS could realise in the realistic scenarios they tested. They also showed that the algorithms used by Weiser et al. were impractical because they require future knowledge only available during the trace-based simulation run.

Lorch and Smith describe a methodology called *PACE* designed to optimise such algorithms for realtime tasks with soft deadlines [Lorch and Smith, 2001]. PACE predicts the probability distribution of a tasks work requirement (i.e. the number of cycles it will take to execute) by looking at past instantiations of the same task. It can then estimate a frequency that will minimise energy consumption while keeping the execution to the real-time schedule.

Simulation can allow theories to be tested, usually without significant implementation overhead. For example, simulating the effects of increasing L1 cache size before manufacturing a new processor design. However, care must be taken to understand the limitations of simulation, for example, during a simulation, the system being developed can use information that it would otherwise not have a priori, such as knowing how long a task is going to take to execute. Furthermore, simulators often make use of simplified system models in order to limit implementation complexity. This makes them less accurate than testing on real systems. For example, Snowdon found that the efficiency of the CPU's voltage regulator on a Dell laptop changed when it switched between modes depending on CPU power requirements [Snowdon, 2010]. Without looking at the real system, the simulator would be unable to account for this change in efficiency.

For these reasons, we find that actual measurements of real systems give more reliable results for

our analyses. The use of actual measurements ensures that all the idiosyncrasies of the system are accounted for when measuring total system power at the *power-supply unit* (PSU).

#### 2.4.3 Modelling and accounting

Modelling is a technique where some measurable characteristics of a system can be used to predict some other unmeasurable characteristic. In the scope of this thesis, modelling power consumption has been attempted numerous times in the literature, usually because computer systems do not have the ability to measure their own power consumption.

#### 2.4.3.1 Modelling power consumption

Bellosa was the first to propose using performance-counter events to model processor power consumption [Bellosa, 2000]. Bellosa showed that a relatively simple linear model can accurately predict the power drawn by a processor when executing a piece of code. For the *process cruise-control* framework (described in Section 2.5.1) Weissel and Bellosa hand-picked several performance-counter events for use in their models.

Pusukuri et al. show that simple models for power consumption can be developed using a small number of performance-counter events as predictors [Pusukuri et al., 2009]. Their models are shown to be robust over a range of workloads from the SPEC CPU 2006 suite, however they find that some benchmarks have a high prediction error. Their model is frequency agnostic, however by using the SPEC CPU suites, they limit the generality of the model because the benchmarks are single-threaded and do not exercise a multi-core system to its' full extent. This is shown in the validation where the SPECjbb 2005 benchmark (a multi-threaded benchmark) has a high prediction error.

Snowdon et al.'s early work looked at several simple embedded systems such as the PLEB2, based on the Intel XScale PXA255 processor [Snowdon and Johnson, 2003; Snowdon et al., 2007]. This is the same processor used in Weissel and Bellosa's *process cruise-control* framework described in Section 2.5.1. The models developed for this simple processor were highly accurate and relatively easy to characterise. This is because the PXA255 has only 15 different performance-counter events which may be measured. Furthermore, the PXA255 lacks complex architectural features such as hardware prefetching [see Intel Corporation, 2003, Section 6.1.1, page 55]. Complex features, as we will show, can cause effects that are difficult to predict from measurements of performance-counter events.

#### 2.4.3.2 Modelling energy consumption

For power-management, an important aspect of modelling *energy* (as opposed to just *power consumption*) is predicting the **execution time** of a piece of code at various CPU frequencies, since:

$$Energy = Time \times Power \tag{2.4}$$

The execution time of a piece of code, T, can be broken down into the number of cycles spent in various frequency domains:

$$T = \frac{C_1}{f_1} + \frac{C_2}{f_2} + \frac{C_3}{f_3} \dots$$

(2.5)

These frequency domains ( $f_1$ ,  $f_2$  and  $f_3$ ) may be made up of the CPU itself, the L3 cache which runs at a different frequency and main memory which operates at yet another frequency. Each component in Equation 2.5 has a coefficient that represents the amount of time that the system spends waiting for that component. An example of such a topology is the AMD *Shanghai* Opteron processor, where the CPU cores, L3 cache and main-memory all operate at different frequencies.

Equation 2.5 then becomes:

$$T = \frac{C_{CPU}}{f_{CPU}} + \frac{C_{L3}}{f_{L3}} + \frac{C_{mem}}{f_{mem}} + \frac{C_{coherency}}{f_{coherency\,link}}$$

(2.6)

The Opteron architecture is also an example of a *cache-coherent non-uniform memory access* (cc-NUMA) system with multiple CPU packages, each connected to its own bank of memory. The *nodes* are connected over a high-speed bus, such as *hyper-transport* (HT) as is the case with the AMD Opteron system. For workloads which share data, cache coherency traffic between nodes can be substantial and as a result the model must accommodate for the CPU cycles spent waiting for the coherency frequency domain.

Using the PMU, we can estimate the number of cycles spent in each frequency domain using a model such as

$$C_{L3} = \alpha L2\_cache\_misses$$

$$C_{mem} = \beta L3\_cache\_misses$$

$$C_{coherency} = \gamma Remote\_requests$$

(2.7)

where  $\alpha$ ,  $\beta$  and  $\gamma$  are platform-dependent coefficients determined through a process called *model characterisation*.

Modern processors have a *cycle counter* which can be used to measure total CPU cycles during execution,  $C_{total}$ . In that case, Equation 2.6 can be rewritten as:

$$C_{CPU} = C_{total} - \frac{f_{CPU}}{f_{L3}}C_{L3} - \frac{f_{CPU}}{f_{mem}}C_{mem} - \frac{f_{CPU}}{f_{coherency}}C_{coherency}$$

(2.8)

The model in Equation 2.8 contains what may seem like obvious parameters (from Equation 2.7). However, in reality, parameter selection is not so simple.

Rajamani et al. develop a model for predicting the performance impact of frequency changes on a single-core Pentium M system [Rajamani et al., 2006]. They use a small set of synthetic benchmarks to characterise their model for execution time. They then validate their model with benchmarks from the SPEC CPU 2000 suite showing that it has, on average, 10% prediction error. Like Bellosa, they hand-pick the performance-counter events to use as parameters in their models.

Snowdon improved on Bellosa's and Rajamani's approach by developing a technique to systematically analyse and choose the best parameters for a model from the pool of potentially hundreds of performance-counter events available on recent processors. The outcome is the characterisation of two models, allowing for prediction of execution time and power consumption under varying CPU frequency.

Snowdon's approach has three stages:

- 1. choose a characterisation benchmark set and measure the system exhaustively;

- 2. perform a regression subset-selection to choose performance-counter events and their coefficients; and

- 3. evaluate (validate) the generated models on a different set of workloads.

The first stage involves running each benchmark workload at each available CPU frequency while measuring each of the available performance counter events, as well as the energy consumed by the system during each benchmark run. This requires running multiple iterations, not only for statistical reasons, but also because most recent CPUs can only measure two to four events at once.

The second stage is to use a computational statistics package such as *R* to perform a *regression subset-selection* [R, 2011]. This involves trying each of the performance-counter events measured in stage one in a model to see which ones provide the highest accuracy. This can be time-consuming, depending linearly on the number of benchmarks in the set, the number of frequencies and the maximum number of parameters to try in each model.

Figure 2.6: Plot of model residuals against measured value for an execution time model with four parameters [R, 2011].

Since only a small number of parameters can be measured at once, there are also constraints between the two models. If the execution time model uses four parameters then the power model must contain a subset of those four. Snowdon characterised the execution time model first and then used the parameters chosen in a subset-selection for the power model.

Part of the second stage is to visually inspect the residual plots to determine how the model is performing. Figure 2.6 shows a graph plotting residuals versus measured values. The value being predicted is actually the ratio of CPU cycles at the current frequency and CPU cycles at the target frequency (the frequency we are predicting)—this is shown on the x axis. The y axis shows the residuals, or error, in each prediction. Each circle on the graph represents an iteration of a benchmark workload being run at one frequency and the ratio of cycles being predicted at another possible frequency. From the graph, the maximum percentage error seen is approximately 10% (0.2/1.8).

The third stage involves validating the models generated in stage two. A different set of *validation* benchmarks are chosen (these should be different to those used during the characterisation) and the models are used to predict the energy consumed at run-time. The actual energy consumed is still measured using a power-meter. The predicted energy is compared to the measured energy to determine the accuracy of the models. See Chapter 3 for an example of such a validation.

Bellosa pioneered the performance-counter based modelling approach, which Snowdon improved on. Several others have also used performance-counters to model both execution time and power consumption under varying frequency, resulting in reasonably accurate predictions for older, singlecore processors. Our own work attempts to extends this approach to modern, multi-core processors.

#### 2.4.4 System-level analysis

The work most closely related to our own was done by Miyoshi et al. on a laptop-class system [Miyoshi et al., 2002]. They showed that the decrease in slack-time resulting from running at a lower CPU frequency can offset any energy savings realised by using DVFS. Using a web-server workload they found that it was more energy-efficient to run at a high frequency (i.e. race-to-halt) for both high-utilisation and low-utilisation scenarios. However, the kind of systems available 9 years ago (when their study was performed) are very different to those available today. As discussed in Section 2.3.2, modern CPUs offer many low-power idle states and their usage results in significantly reduced power consumption.

Bircher et al. use performance-counters to develop models of an entire system, as opposed to just the CPU. Their technique uses the relationship between certain CPU performance-counter events and other activity in the system to attribute power consumed by subsystems such as the hard-drive, chipset and memory [Bircher and John, 2007]. They characterise their models with SPEC CPU benchmarks, a Java benchmark and a synthetic disk benchmark. The models they developed were shown to have an average error of less than 9%.

More recently, Bircher et al. have looked at DVFS on CMP systems such as those based on AMD's Opteron processors [Bircher and John, 2008]. Bircher et al. find that reducing the frequency of a single core has a negative effect on the performance of other cores operating at higher frequencies. This was found to be due to the Opteron's shared cache architecture. Cache coherency probes to cores that are running at low frequencies take longer, and as a result, workloads that share memory are affected by DVFS decisions in ways that older systems were not.

Carroll and Heiser analyse the power consumption of several smart-phones, firstly by fine-grained instrumentation of an OpenMoko Freerunner, an open-source mobile hardware platform [Carroll and Heiser, 2010]. They find that most power is consumed by components *other* than the CPU, such as radios and the LCD back-light. These findings are validated by measuring the total power consumption of two more recent smart-phones, the Google G1 (HTC Dream) and Google Nexus 1 (HTC Desire).

System-level analysis provides a complete picture of the power consumption characteristics of a computer system. It gives an indication of which components are the most *power hungry*, and therefore, suggests the best places to look for opportunities to improve energy efficiency. Miyoshi et al. perform a similar study to our own on a much older system [Miyoshi et al., 2002]. However, power-management and computer architecture have moved on since then. Carroll and Heiser's recent study finds that on embedded systems, the processor consumes a small proportion of total power relative to other components, such as LCD back-lights and wireless network radios [Carroll and Heiser, 2010].

Our work looks at the effectiveness of DVFS on more recent systems which have numerous low-

power idle states. In the past, processors either had no idle states or, only a single idle state with relatively high power consumption when compared to the processors of today.

## 2.4.5 Scheduling on multi-core systems

Systems based on multi-core processors present opportunities to choose tasks to *co-schedule*. Merkel and Bellosa study the effects of co-scheduling tasks with different memory-intensity. This is achieved by sorting (by memory-intensity) the run-queues that the OS scheduler maintains for tasks executing on the system. They find that DVFS only saves energy when memory-bound tasks are co-scheduled together [Merkel and Bellosa, 2008]. However, in doing this, the performance of these tasks is severely impacted. Their conclusion is that the optimal scheduling strategy for maximum energy efficiency is to co-schedule memory-intensive tasks together with compute-intensive tasks. This allows the memory-intensive task full use of the memory hierarchy, with minimal impact on the performance of the compute-intensive task, which has a memory-footprint that fits inside the core-local cache.

*Asymmetric multi-processor* (AMP) systems were proposed as a more power-efficient way to design multi-core processors [Kumar et al., 2003, 2004]. Currently, multi-core processors include many cores of the same *instruction-set architecture* (ISA) and design, operating at the same frequency (i.e. *symmetric multi-processor* (SMP) systems). An AMP may contain cores which are *fast* or slow. Fast cores are characterised by deep pipelines and high issue width, out-of-order execution, aggressive branch prediction and high frequency. *Slow* cores, on the other hand, may have shallower pipelines, be in-order, single-issue, etc. The power-performance trade-offs differ greatly between these two core types. Certain workload types are better suited to slow cores, while others are more suited to fast cores. Because workloads may exhibit both compute-intensive and memory-intensive phases, the decision about which core to run on cannot simply be made at the beginning of program execution. Rather, the program must be monitored at run-time and a decision made (by the OS scheduler) about whether to *migrate* a task between cores.

Saez et al. developed a comprehensive scheduler for AMP systems [Saez et al., 2010]. Using hand-picked combinations of SPEC CPU workloads, they established a model which can predict the *speed-up factor* of running a task on a fast core compared to running on a slow core. Their model is shown to be accurate over a wide range of workload types, including those that are multi-threaded. On their test system, fast cores are characterised only by a high frequency. There are many different ways in which fast and slow cores can vary, such as those described above. They conclude that, regardless of the characteristics of the cores, AMP systems are a viable alternative to SMP systems.

As there are currently no commercial AMP systems available, they must be emulated. This can be achieved in various ways. Many have used DVFS to create performance asymmetry. Li et al. also study scheduling on AMP systems. However, instead of using DVFS, they create performance asymmetry by controlling the issue width on an x86 processor [Li et al., 2007]. This is done by putting one or more cores of a CMP into a special '*debug*' mode. They present *AMPS* an OS scheduler

that supports architectures with both SMP and NUMA style performance asymmetry. Using a range of workloads (SPEC OMP, SPECjbb, kernbench and Ogg Vorbis encoding) they show that AMPS is capable of improving performance by up to 44 % compared to the standard Linux 2.6.16 scheduler for some workloads. The focus of this paper is on improving performance rather than energy efficiency.

Scheduling presents many interesting opportunities for power management on multi-core systems. However, constraints between cores, such are operating frequency and shared resources limit the benefits achieved from mechanisms such as DVFS as Merkel and Bellosa show.

AMP systems are an interesting new direction for processor architecture and bring different trade-offs to power-management. Work in this area is mostly unrelated to our own, however our work could influence the design decisions made in these new processors, for example, whether to implement per-core DVFS or provide only chip-wide DVFS.

## 2.4.6 Discussion

Researchers and OS developers have used power-management mechanisms in numerous ways to achieve many different goals. The primary purpose of their work is to improve the energy efficiency of computer systems, allowing increased longevity for battery-powered devices and reduced power/cooling bills for data-centres. Much of the prior work in this area has used DVFS, however, few have analysed how its effectiveness has changed over time.

## 2.5 OS Energy Management

The OS plays a critical role in power management. Many previous researchers have developed novel ways to leverage power-management mechanisms in order to improve energy efficiency or to attribute energy consumption to particular system activities. Power management is an active area of research in academia and in the industry. However, while academia thrives on publication, industry is often secretive about techniques that give a competitive advantage. Battery life is a critical driver for power-management research in the industry, and, often the results of such research are not published. However, the power-management frameworks used in *Linux* are open-source. Firstly, we discuss several research frameworks, and secondly, we discuss those within Linux.

## 2.5.1 Research frameworks

Researchers have studied OS power-management for many years, resulting in the development of many frameworks. The primary goals of these frameworks is to attribute energy consumption to tasks running on a system and allow intelligent power-management decisions to be made.

For example, Weissel and Bellosa developed *process cruise-control*, a framework that is based on modelling the response of workloads to changes in CPU frequency [Weissel and Bellosa, 2002]. This was achieved by correlating hardware performance-counter events (measured by the PMU) with performance and energy consumption measurements. Performance-counter measurements are recorded at run-time for each process running in the system. The expected performance loss is then calculated for each frequency the processor can run at, and a frequency is chosen that will give no more than 10% performance degradation. This system was able to achieve energy savings of up to 22% for memory-intensive applications when frequency *alone* was scaled. It was further claimed that their system would achieve savings at least 37% if the voltage was scaled as well.