# Proving Confidentiality and Its Preservation Under Compilation for Mixed-Sensitivity Concurrent Programs

#### Robert Sison

Submitted in fulfilment of the requirements for the degree of Doctor of Philosophy

School of Computer Science and Engineering Faculty of Engineering

October 2020

## Thesis/Dissertation Sheet

Surname/Family Name : Sison

Given Name/s : Robert Abella

Abbreviation for degree as given in the University calendar : PhD

Faculty : Engineering

School : Computer Science and Engineering

Thesis Title Proving Confidentiality and Its Preservation Under Compilation for

Mixed-Sensitivity Concurrent Programs

#### Abstract 350 words maximum:

Here, I pose the thesis that proving noninterference and its preservation by a compiler is feasible for mixed-sensitivity concurrent programs. Software does not always have the luxury of limiting itself to single-threaded computation with resources statically dedicated to each user to ensure the confidentiality of their data. Prior work therefore presented formal methods for proving and preserving the strictest kind of confidentiality property, noninterference, for mixed-sensitivity concurrent programs: a term I coin to describe those programs that might reuse memory shared between their threads to hold data of different sensitivity levels at different times. Although these methods addressed challenges in formalising the value-dependent coordination of such mixed-sensitivity reuse under the impact of concurrency, their practicality remained unclear: Could they be used to prove noninterference for any nontrivial mixed-sensitivity concurrent program in its entirety? Furthermore, could any compiler be verified to preserve the needed guarantees to the compiled code?

To support this claim, I prove for the first time both (1) noninterference for a nontrivial mixed-sensitivity concurrent program, modelling a real-world use case, and (2) its preservation by a compiler down to an assembly-level model. This main result rests on two major contributions. First, I demonstrate how programming-language designers can make reasoning on each thread sufficient to prove noninterference for such programs, by supplying synchronisation primitives (here, mutex locks for a generic imperative language) and proving they maintain as invariant the necessary requirements. Second, I demonstrate how compiler developers can make confidentiality-preserving refinement a feasible target for verification, by using a decomposition principle to prove that a compiler (here, from that imperative language to a generic RISC-style assembly language) establishes it for mixed-sensitivity concurrent programs. Thus, per-thread reasoning proves noninterference for the case study, and the verified compiler preserves it to assembly automatically. All my results are formalised and proved in the Isabelle/HOL interactive proof assistant.

My work paves the way for more fully featured programming languages and their compilers, in replicating these results, to raise the typical level of assurance readily offered by developers of multithreaded software responsible for data of multiple sensitivity levels.

| Declaration relating to disposition of project thesis/dissertation                                                                                                                                                                                                                                                                                                  |                                                                                                                                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| I hereby grant to the University of New South Wales or its agents a non-exclusive lipublic) my thesis or dissertation in whole or in part in the University libraries in all for all intellectual property rights which subsist in my thesis or dissertation, such as copright to use all or part of my thesis or dissertation in future works (such as articles or | orms of media, now or here after known. I acknowledge that I retain byright and patent rights, subject to applicable law. I also retain the |

| Signature                                                                                                                                                                                                                                                                                                                                                           | Date                                                                                                                                        |

| The University recognises that there may be exceptional circumstances requiring re                                                                                                                                                                                                                                                                                  | estrictions on copying or conditions on use. Requests for restriction                                                                       |

The University recognises that there may be exceptional circumstances requiring restrictions on copying or conditions on use. Requests for restriction for a period of up to 2 years can be made when submitting the final copies of your thesis to the UNSW Library. Requests for a longer period of restriction may be considered in exceptional circumstances and require the approval of the Dean of Graduate Research.

#### **ORIGINALITY STATEMENT**

'I hereby declare that this submission is my own work and to the best of my knowledge it contains no materials previously published or written by another person, or substantial proportions of material which have been accepted for the award of any other degree or diploma at UNSW or any other educational institution, except where due acknowledgement is made in the thesis. Any contribution made to the research by others, with whom I have worked at UNSW or elsewhere, is explicitly acknowledged in the thesis. I also declare that the intellectual content of this thesis is the product of my own work, except to the extent that assistance from others in the project's design and conception or in style, presentation and linguistic expression is acknowledged.'

| Signed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Date                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| COPYRIGHT STATEMENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 'I hereby grant the University of New South Wales or its agents a non-exclusive licence to archive and to make available (including to members of the public) my thesis or dissertation in whole or part in the University libraries in all forms of media, now or here after known. I acknowledge that I retain all intellectual property rights which subsist in my thesis or dissertation, such as copyright and patent rights, subject to applicable law. I also retain the right to use all or part of my thesis or dissertation in future works (such as articles or books).' |

| 'For any substantial portions of copyright material used in this thesis, written permission for use has been obtained, or the copyright material is removed from the final public version of the thesis.'                                                                                                                                                                                                                                                                                                                                                                           |

| Signed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Date                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| AUTHENTICITY STATEMENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 'I certify that the Library deposit digital copy is a direct equivalent of the final officially approved version of my thesis.'                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Signed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Date                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

#### INCLUSION OF PUBLICATIONS STATEMENT

UNSW is supportive of candidates publishing their research results during their candidature as detailed in the UNSW Thesis Examination Procedure.

Publications can be used in your thesis in lieu of a Chapter provided:

- You contributed greater than 50% of the content in the publication and are the "primary author", i.e. you were responsible primarily for the planning, execution and preparation of the work for publication.

- You have approval to include the publication in their thesis in lieu of a Chapter from your Supervisor and Postgraduate Coordinator.

- The publication is not subject to any obligations or contractual agreements with a third party that would constrain its inclusion in the thesis.

Some of the work described in my thesis has been published and it has been documented in the relevant Chapters with acknowledgement.

A short statement on where this work appears in the thesis and how this work is acknowledged within chapter/s:

The formal preliminaries in Chapter 3 expand on a similar presentation I gave in a conference paper of which I was the primary author, published at Interactive Theorem Proving (ITP 2019). This is acknowledged at the beginning of Chapter 3.

The contributions of Chapter 4 led to a conference paper to which I contributed, published at European Symposium on Security and Privacy (EuroS&P 2018), which also first presented the case study of Chapter 6.

The contributions of Chapter 5 were first presented by me at the Workshop on Principles of Secure Compilation (PriSC 2018), then subsequently presented in more detail by me in the ITP 2019 conference paper.

For further discussion of these publications, their relationship with this thesis, and all acknowledgments of the work of others, please see the "Overview of contributions" section in Chapter 1, and the "Publications and acknowledgements" section in each of Chapters 4, 5, and 6.

#### **CANDIDATE'S DECLARATION**

I declare that I have complied with the Thesis Examination Procedure.

| Candidate's Name | Signature | Date (dd/mm/yy) |

|------------------|-----------|-----------------|

|                  |           |                 |

|                  |           |                 |

# Abstract

Here, I pose the thesis that proving noninterference and its preservation by a compiler is feasible for mixed-sensitivity concurrent programs. Software does not always have the luxury of limiting itself to single-threaded computation with resources statically dedicated to each user to ensure the confidentiality of their data. Prior work therefore presented formal methods for proving and preserving the strictest kind of confidentiality property, noninterference, for mixed-sensitivity concurrent programs: a term I coin to describe those programs that might reuse memory shared between their threads to hold data of different sensitivity levels at different times. Although these methods addressed challenges in formalising the value-dependent coordination of such mixed-sensitivity reuse under the impact of concurrency, their practicality remained unclear: Could they be used to prove noninterference for any nontrivial mixed-sensitivity concurrent program in its entirety? Furthermore, could any compiler be verified to preserve the needed guarantees to the compiled code?

To support this claim, I prove for the first time both (1) noninterference for a non-trivial mixed-sensitivity concurrent program, modelling a real-world use case, and (2) its preservation by a compiler down to an assembly-level model. This main result rests on two major contributions. First, I demonstrate how programming-language designers can make reasoning on each thread sufficient to prove noninterference for such programs, by supplying synchronisation primitives (here, mutex locks for a generic imperative language) and proving they maintain as invariant the necessary requirements. Second, I demonstrate how compiler developers can make confidentiality-preserving refinement a feasible target for verification, by using a decomposition principle to prove that a compiler (here, from that imperative language to a generic RISC-style assembly language) establishes it for mixed-sensitivity concurrent programs. Thus, per-thread reasoning proves noninterference for the case study, and the verified compiler preserves it to assembly automatically. All my results are formalised and proved in the Isabelle/HOL interactive proof assistant.

My work paves the way for more fully featured programming languages and their compilers, in replicating these results, to raise the typical level of assurance readily offered by developers of multithreaded software responsible for data of multiple sensitivity levels.

# Acknowledgements

Foremost, I thank my supervisors Carroll Morgan, Toby Murray, and Kai Engelhardt, who taught me how to be a researcher in this field.

For cultivating an excellent working and learning environment, I would like to thank the Trustworthy Systems group at CSIRO's Data61 under the leadership of June Andronick, and all the regular attendees of its reading groups.

For memorable conversations and other inputs and feedback on my work that shaped both its direction over the years of my candidature, and its presentation in this dissertation, I thank also Gerwin Klein, Christine Rizkallah, Edward Pierzchalski, Ramana Kumar, Matthew Brecknell, Johannes Åman Pohjola, Qian Ge, and Gernot Heiser. For their careful evaluation of its merits and shortcomings, I thank Gilles Barthe and David Sands.

Furthermore, I thank Alexander Legg and Anna Lyons for their mentoring and advice, delivered variously over coffee and in the midst of a metal concert.

Finally, I thank my partner Leo and my extended family for their ongoing support, and I dedicate this work to the memory of my grandfather, an architect.

This research was funded by an Australian Government Research Training Program (RTP) Scholarship, and a CSIRO Data61 Research Project Award.

# **Publications**

The contributions of Chapter 4 led to the following conference paper, which also first presented the case study of Chapter 6:

• [68] Toby Murray, Robert Sison, and Kai Engelhardt. Covern: A logic for compositional verification of information flow control. In *European Symposium on Security and Privacy*, pages 16–30, London, United Kingdom, April 2018. IEEE.

The contributions of Chapter 5 led to a workshop presentation and a conference paper, both of which I presented:

- [83] Robert Sison. Per-thread compositional compilation for confidentiality-preserving concurrent programs. In 2nd Workshop on Principles of Secure Compilation, Los Angeles, January 2018. Cătălin Hriţcu.

- [85] Robert Sison and Toby Murray. Verifying that a compiler preserves concurrent value-dependent information-flow security. In 10th International Conference on Interactive Theorem Proving (ITP 2019), volume 141, pages 27:1–27:19, Portland, USA, September 2019. Schloss Dagstuhl Leibniz-Zentrum für Informatik.

For further discussion of these publications and their relationship with this thesis, please see Section 1.3 ("Overview of contributions"), and Sections 4.5, 5.6, and 6.7 ("Publications and acknowledgements").

# List of Figures

| 1.1 | Example of conversion of an internal timing leak into a storage leak            | 4   |

|-----|---------------------------------------------------------------------------------|-----|

| 1.2 | Example of mixed-sensitivity reuse                                              | 6   |

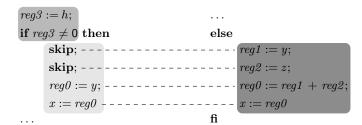

| 3.1 | Excerpts from a CVDNI-preserving refinement example                             | 34  |

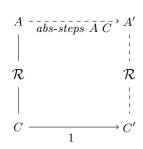

| 3.2 | Definition and graphical depiction of refinement preservation obligation        | 35  |

| 3.3 | Graphical depictions of decomposed refinement preservation obligations $$       | 37  |

| 4.1 | Annotation versus enforcement of assumptions on shared memory access            | 40  |

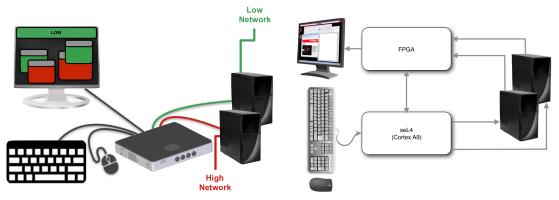

| 6.1 | Functional schematics for Cross Domain Desktop Compositor hardware              | 82  |

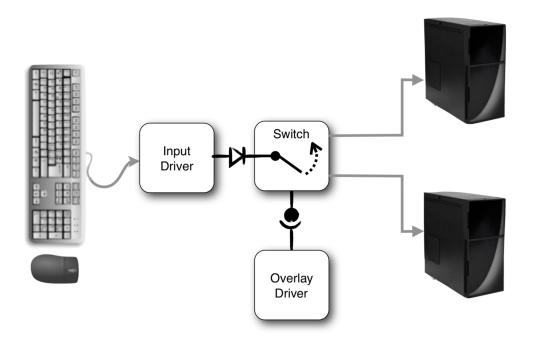

| 6.2 | Functional schematic of seL4 component architecture for CDDC HID switch         | 83  |

| 6.3 | Examples of external device interactions by the CDDC HID switch model $$ .      | 85  |

| 6.4 | Examples of the SWITCH component interfacing with the compositor device         | 87  |

| 6.5 | Remote procedure call abstraction between SWITCH, OVERLAY components            | 88  |

| 6.6 | Examples of the SWITCH component interacting with the input-event buffer.       | 90  |

| 7.1 | Examples of secret-dependent control flow admitted by typing rule IFH           | 98  |

| 7.2 | Example program admitted by typing rule IFH with nested branching               | 108 |

| A.1 | Introduction rule for case $if\_expr$ of refinement relation $\mathcal{R}_{wr}$ | 131 |

| A.2 | Excerpt of wr-compiler implementation: case for if-conditionals                 | 131 |

# Contents

| A            | bstra  | $\mathbf{ct}$ |                                                                          | iii          |

|--------------|--------|---------------|--------------------------------------------------------------------------|--------------|

| $\mathbf{A}$ | ckno   | wledge        | ements                                                                   | $\mathbf{v}$ |

| P            | ublic  | ations        |                                                                          | vii          |

| Li           | ist of | Figur         | es                                                                       | ix           |

| 1            | Cor    | nfident       | iality in the face of scale                                              | 1            |

|              | 1.1    |               | l-sensitivity concurrency and its challenges                             | 2            |

|              |        | 1.1.1         | Concurrency: Scaling with the number of workers                          | 2            |

|              |        | 1.1.2         | Mixed-sensitivity reuse: Scaling with the number of customers            | 5            |

|              |        | 1.1.3         | Compositionality: Scaling with the size of the software project          | 6            |

|              | 1.2    | Appro         | paches taken by this thesis                                              | 7            |

|              |        | 1.2.1         | Assume–guarantee contracts, on worker–resource access                    | 7            |

|              |        | 1.2.2         | Value-dependent classification, for customer–resource dedication         | 8            |

|              |        | 1.2.3         | Confidentiality-preserving refinement, for compiler verification         | 8            |

|              |        | 1.2.4         | Machine-checked formalisation and proof                                  | 8            |

|              | 1.3    | Overv         | iew of contributions                                                     | 8            |

|              |        | 1.3.1         | Completion of a program verification method                              | 9            |

|              |        | 1.3.2         | Demonstration of a compiler verification method                          | 9            |

|              |        | 1.3.3         | Demonstration of program verification, preserved by a compiler           | 10           |

|              |        | 1.3.4         | Program verification extension for secret-dependent control flow $$ . $$ | 10           |

| <b>2</b>     | Rev    | view of       | related formal methods                                                   | 11           |

|              | 2.1    | Defini        | ng noninterference                                                       | 11           |

|              | 2.2    | Progra        | am verification: Proving noninterference                                 | 12           |

|              |        | 2.2.1         | With better precision, through flow sensitivity                          | 12           |

|              |        | 2.2.2         | With mixed-sensitivity reuse, through value dependence                   | 13           |

|              |        | 2.2.3         | With concurrency, done compositionally                                   | 14           |

|              |        | 2.2.4         | With both mixed-sensitivity reuse and concurrency                        | 19           |

|              |        | 2.2.5         | With secret-dependent control flow, despite concurrency                  | 20           |

|              | 2.3    | Comp          | iler verification: Proving property preservation                         | 22           |

|              |        | 2.3.1         | For single-trace properties, like safety and liveness                    | 22           |

|              |        | 2.3.2         | For multiple-trace hyperproperties, like noninterference                 | 23           |

|              |        | 2.3.3         | For noninterference with concurrency                                     | 24           |

| 3 | For | mal preliminaries from background work                            | <b>27</b> |  |  |  |

|---|-----|-------------------------------------------------------------------|-----------|--|--|--|

|   | 3.1 | Concurrent value-dependent noninterference (CVDNI)                | 28        |  |  |  |

|   |     | 3.1.1 Basic elements                                              | 28        |  |  |  |

|   |     | 3.1.2 Parameters for initial conditions and extra requirements    | 31        |  |  |  |

|   |     | 3.1.3 Compositionality requirements                               | 32        |  |  |  |

|   | 3.2 | CVDNI-preserving refinement                                       | 33        |  |  |  |

|   |     | 3.2.1 Original notion with cube-shaped diagram                    | 34        |  |  |  |

|   |     | 3.2.2 Decomposition principle                                     | 36        |  |  |  |

|   | 3.3 | Summary                                                           | 38        |  |  |  |

| 4 | Cor | npositional noninterference for a While language with mutex locks | 39        |  |  |  |

|   | 4.1 | Source language: While with mutex locks                           | 41        |  |  |  |

|   |     | 4.1.1 Locking discipline and its semantics                        | 42        |  |  |  |

|   |     | 4.1.2 Restrictions on locking disciplines                         | 44        |  |  |  |

|   | 4.2 | Local mode compliance check                                       | 45        |  |  |  |

|   |     | 4.2.1 New rules for mutex locks                                   | 46        |  |  |  |

|   |     | 4.2.2 Proof of soundness                                          | 47        |  |  |  |

|   | 4.3 | Global modes compatibility                                        | 48        |  |  |  |

|   |     | 4.3.1 Proof of invariance                                         | 48        |  |  |  |

|   |     | 4.3.2 Initial conditions                                          | 51        |  |  |  |

|   | 4.4 | Security type system                                              | 52        |  |  |  |

|   |     | 4.4.1 New rules for mutex locks                                   | 53        |  |  |  |

|   |     | 4.4.2 Proof of soundness                                          | 55        |  |  |  |

|   | 4.5 | Publications and acknowledgements                                 | 60        |  |  |  |

|   | 4.6 | Summary                                                           |           |  |  |  |

| 5 | Nor | ninterference-preserving compiler for mixed-sensitivity           |           |  |  |  |

|   | con | current While programs                                            | 63        |  |  |  |

|   | 5.1 | Target language: RISC with mutex locks                            | 64        |  |  |  |

|   | 5.2 | Preserving race-free expression evaluation                        | 65        |  |  |  |

|   |     | 5.2.1 Requirements on inputs to the wr-compiler                   | 66        |  |  |  |

|   |     | 5.2.2 Proof that all tracked register contents are stable         | 68        |  |  |  |

|   | 5.3 | Preserving a ban on secret-dependent control flow                 |           |  |  |  |

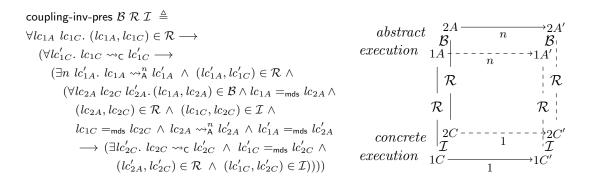

|   | 5.4 | Use of the decomposition principle                                | 69        |  |  |  |

|   |     | 5.4.1 Refinement relation $\mathcal{R}_{wr}$ and its invariants   | 70        |  |  |  |

|   |     | 5.4.2 Refinement pacing function abs-steps <sub>wr</sub>          | 71        |  |  |  |

|   |     | 5.4.3 Concrete coupling invariant $\mathcal{I}_{wr}$              | 74        |  |  |  |

|   |     | 5.4.4 Proof of CVDNI-preserving refinement                        | 74        |  |  |  |

|   | 5.5 | Proof of compositional noninterference preservation               | 76        |  |  |  |

|   | 5.6 | Publications and acknowledgements                                 | 79        |  |  |  |

|   | 5 7 | Summary                                                           | 80        |  |  |  |

| 6 | Cas            | e study: Cross Domain Desktop Compositor input handler 81               |  |  |  |  |

|---|----------------|-------------------------------------------------------------------------|--|--|--|--|

|   | 6.1            | Overview of the case study                                              |  |  |  |  |

|   | 6.2            | External device interactions                                            |  |  |  |  |

|   |                | 6.2.1 Attacker model (at the output devices)                            |  |  |  |  |

|   |                | 6.2.2 Trusted user model (at the input devices)                         |  |  |  |  |

|   | 6.3            | Internal device and inter-component interactions                        |  |  |  |  |

|   |                | 6.3.1 Use of the compositor device (by Overlay driver, Switch) 86       |  |  |  |  |

|   |                | 6.3.2 Remote procedure calls (between SWITCH and OVERLAY driver) 8      |  |  |  |  |

|   |                | 6.3.3 Input-event buffer (between Input driver and Switch) 88           |  |  |  |  |

|   | 6.4            | Proof of confidentiality for the While model                            |  |  |  |  |

|   | 6.5            | Automation and user intervention                                        |  |  |  |  |

|   | 6.6            | Confidentiality-preserving compilation to RISC model                    |  |  |  |  |

|   | 6.7            | Publications and acknowledgements                                       |  |  |  |  |

|   | 6.8            | Summary                                                                 |  |  |  |  |

| 7 | Sec            | urity typing extension for secret-dependent control flow 97             |  |  |  |  |

|   | 7.1            | Intuitions behind the new security typing rule IFH                      |  |  |  |  |

|   | 7.2            | Updates to While-language security type system                          |  |  |  |  |

|   | 7.3            |                                                                         |  |  |  |  |

|   | 7.4            | Proof of soundness of the new typing rule                               |  |  |  |  |

|   |                | 7.4.1 The new bisimulation construction is still a security witness 103 |  |  |  |  |

|   |                | 7.4.2 The construction still captures well-typed program execution 106  |  |  |  |  |

|   | 7.5            | Summary                                                                 |  |  |  |  |

| 8 | Conclusion 109 |                                                                         |  |  |  |  |

|   | 8.1            | What my work showed                                                     |  |  |  |  |

|   |                | 8.1.1 Assume–guarantee makes it feasible to prove that synchronisation  |  |  |  |  |

|   |                | primitives make CVDNI proofs compositional 109                          |  |  |  |  |

|   |                | 8.1.2 Decomposition principles make it more feasible to prove that com- |  |  |  |  |

|   |                | pilers satisfy CVDNI-preserving refinement                              |  |  |  |  |

|   |                | 8.1.3 Security type systems can prove CVDNI automatically for programs  |  |  |  |  |

|   |                | with secret-dependent control flow                                      |  |  |  |  |

|   | 8.2            | Why it matters: Scaling up with scarce resources                        |  |  |  |  |

|   |                | 8.2.1 For multithreaded system software that implements sharing 113     |  |  |  |  |

|   |                | 8.2.2 Support by programming languages and their compilers 113          |  |  |  |  |

|   | 8.3            | What might come next?                                                   |  |  |  |  |

|   |                | 8.3.1 Languages with indirect-addressing commands                       |  |  |  |  |

|   |                | 8.3.2 More compile-time optimisations on shared memory                  |  |  |  |  |

|   |                | 8.3.3 Compiler preservation of general assume–guarantee reasoning 113   |  |  |  |  |

|   |                | 8.3.4 Further support for secret-dependent control flow                 |  |  |  |  |

|   | 8.4            | Closing remarks                                                         |  |  |  |  |

|   |                |                                                                         |  |  |  |  |

| וטו          | שטווטפ                                                                       | graphy |                                         | 115 |  |  |  |  |

|--------------|------------------------------------------------------------------------------|--------|-----------------------------------------|-----|--|--|--|--|

| $\mathbf{A}$ | A Extra details about the Covern wr-compiler                                 |        |                                         |     |  |  |  |  |

|              | A.1                                                                          | Label  | allocation and sequential composability | 127 |  |  |  |  |

|              | A.2 Register allocation scheme model                                         |        |                                         |     |  |  |  |  |

|              | A.3 Informal descriptions of cases of refinement relation $\mathcal{R}_{wr}$ |        |                                         |     |  |  |  |  |

|              |                                                                              | A.3.1  | Base cases                              | 128 |  |  |  |  |

|              |                                                                              | A.3.2  | Inductive cases                         | 128 |  |  |  |  |

| В            | Ext                                                                          | ra det | ails about the IfH security typing rule | 133 |  |  |  |  |

## Chapter 1

# Confidentiality in the face of scale

This thesis is about techniques for proving two things:

1. The total absence of information flow between a trusted and untrusted party in a given program, including concurrent programs that reuse shared memory to scale up their capacity to service different parties at different times.

For such programs, this thesis in particular concerns proofs eliminating the flow of information between two sets of memory locations—sensitive sources and untrusted sinks—designated by the user of the techniques as belonging to each party. Information coming from the former set of locations will also be described as sensitive, and be called secrets. The attacker model throughout this thesis will be an entity with the power to read at any time from the untrusted sinks.

This kind of strict prohibition of information flow is called *noninterference* [32] in the literature. Unless specified otherwise, this thesis will also use the broader terms confidentiality, information-flow security, and security to mean noninterference.

2. That a compiler preserves this total absence of information flow in such programs when translating them to other languages.

To be clear, this thesis is *not* about placing upper bounds on some small but necessary amount of information leakage between a trusted and untrusted party. If I have the job of "password checker", the techniques studied here will inevitably find leaks, for example, between the piece of paper from my boss with today's secret password, and the answer of "accepted" or "rejected" I give to the stranger at the window who tried to guess it. Even if it would take the stranger thousands of guesses, the techniques in this thesis will flag even this tiniest of leaks in a single one of my "yes" or "no" answers as unsafe. I must defer to the authority of other, leakage-bounding techniques like quantitative information flow [87] or differential privacy [4], for determining whether the rate of leakage inherent in the application domain is acceptable—such a task lies outside the scope of this thesis.

This thesis is more about whether I inadvertently leave the password on the coffee table in the break room where we host discussions with external clients who visit the building—or inexplicably blurt out the password at the cafeteria when I'm ordering lunch.

These kinds of extremely obviously wrong behaviours regarding confidentiality may sound easy to avoid. In fact, it sounds so easy that when a computer program about which we have full details does the right thing, surely we should be able to *prove* that it holds, in a way that arises *from the form* of that program. Indeed, techniques already exist that make it straightforward to *prove formally* that some kinds of computer programs do not do the obvious wrong thing, like leaving the password on the proverbial coffee table.

This thesis, however, will be about those programs for which the reasoning of these techniques breaks down—where such an apparently easy task is not, in fact, so easy.

#### 1.1 Mixed-sensitivity concurrency and its challenges

The specific focus of this thesis is on how these two problems—(1) the program verification problem of proving total absence of information flow, and (2) the compiler verification problem of proving its preservation by a compiler—become more challenging when a program has both of the following characteristics:

- Concurrency (Section 1.1.1): specifically, concurrency of access by different threads of execution, to memory locations shared between those threads.

- Mixed-sensitivity reuse (Section 1.1.2): a term I coin to describe a reuse of memory locations to hold information of differing levels of sensitivity, at different times.

These characteristics are answers to fundamental problems of scale. They arise, respectively, from the need to divide work in computer systems that handle information, and the need to share scarce resources to be able to service every customer for whom that work is done. There will always be a program for which that sharing is not abstracted, and whose responsibility is to implement that sharing; proving that it does not permit the information of one customer to flow to another is the objective of this thesis.

As answers to problems of scale, these characteristics pose an additional challenge: Compositionality (Section 1.1.3) demands that a proof about a program be composable from proofs about its parts, that are each not overly sensitive to changes to the other parts. This thesis focuses on compositionality of proofs about program threads—in this way, the proof effort can scale with the development effort as split into concurrent components.

In addressing these challenges, this thesis demonstrates that it is feasible to prove noninterference and its preservation under compilation for *mixed-sensitivity concurrent* programs, a term I coin for those whose threads make mixed-sensitivity reuse of the memory they share. Prior to my doctoral studies, no formal techniques had been exercised to prove noninterference, or its preservation by a compiler, for such a program in its entirety.

#### 1.1.1 Concurrency: Scaling with the number of workers

Concurrency poses two new challenges when proving noninterference properties and their preservation by a compiler: (1) managing the proof impact of inter-thread interactions,

and (2) preventing the conversion of internal timing leaks into storage leaks.

#### Inter-thread interactions, as interference and intermediate value leakage

It is well known that the possibility of interactions between the threads of a concurrent program—as coworkers that need to cooperate using a shared pool of resources—leads to the number of possible configurations growing exponentially in the number of threads.

The main impact on proofs of confidentiality for such programs is that the usual shortcuts that are available to analyses of the behaviour of a *sequential program* (a single thread of execution assumed to be working in complete isolation) no longer apply:

- Analyses of confidentiality for sequential programs will typically assume that secrets (including any intermediate values derived from secrets) can be stored temporarily at locations that might only become visible to the attacker at the end of the program. However, in a concurrent program I cannot assume that secrets stored at such a location will not be read by another worker, if that location is in a shared space.

- As Section 1.1.2 will explain: When coordinating mixed-sensitivity reuse, a program's functional-correctness issues can now become security issues.

Analyses of the functionality of sequential programs will typically assume that values written to a location will still be there later, unless that one thread of execution writes to the location again. This allows such analyses to be *flow sensitive* [19], meaning they can take into account what happens before and after a given point in the program—i.e. be *sensitive* to that program point's position in *the control flow*.

However, as a worker thread in a concurrent program, I cannot assume that something will be where I left it, because another worker thread might have replaced it with something else. This inherent *instability* of the contents of the shared space, due to *interference* by other threads in the program, thus (if not mitigated) poses an obstacle to flow sensitive analysis of a concurrent program's functionality.

These issues pose the challenge of finding ways to reason about the **coordination** of workers' access to certain resources at certain times. With a means of formalising this coordination, (1) confidentiality proofs for concurrent programs can be structured to recognise when the coordination rules out instances of instability due to interference, or inadvertent leaks due to other workers' reading of secret intermediate values; and (2) verified compilers can be proved formally to preserve any such methods of coordination.

#### Internal timing leaks become storage leaks, without a specialised scheduler

Concurrent settings with shared space are notorious for converting internal timing leaks into storage leaks. This section will explain the problem, and the difficulties arising from preventing it without overly constraining programs, or specialising the *scheduler* to assist—that is, the part of the execution environment that chooses how threads are interleaved.

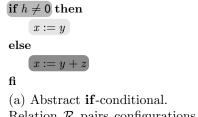

Figure 1.1: Example of conversion of an internal timing leak into a storage leak. Here, h contains a secret, s is shared between both threads, and x is an untrusted sink.

Informally, storage leaks (discernible by a difference in value) are often distinguished from timing leaks (discernible by a difference in the timing of identical changes in value) because an attacker that can easily detect a storage leak (e.g. the final value of v in Thread A in Figure 1.1) may have no way of measuring the timing of changes to storage reliably enough to exploit a timing leak (e.g. the timing of Thread A's assignment of TRUE to s).

In a concurrent program, however, a timing leak must be treated as seriously as any storage leak. Consider the (pseudocode) example program in Figure 1.1, with s = FALSE initially: If the scheduler chooses to switch execution to Thread B after executing three of the numbered commands of Thread A, this program produces a storage leak of the exact (boolean) value of h to the variable x, which stems from the timing leak of h determining whether the assignment to s has happened yet. This example illustrates two principles:

- 1. The notion of time that matters is *scheduler relative*: counted by the distinct points at which the scheduler might interleave a thread's execution with that of others. The literature typically calls this *internal time* (and *internal timing leaks*); I will sometimes use the term *scheduler-relative time*, to emphasise the role of the scheduler.

- 2. Internal timing leaks are propagated to storage by  $race\ conditions$ ; here, a race between Thread A's write and Thread B's read of s determines the final value of x.

Thus, early approaches included: (1) having programs avoid race conditions by disallowing all asynchronous communication via shared memory [101], including that which would be needed to implement synchronisation primitives; or, (2) specialising the scheduler to control the notion of time to avoid leaky schedules [9, 10]. For instance, if the scheduler here only ever chose to switch to Thread B after two (or four) of the numbered commands of Thread A, it could ensure that the final value of x is unconditionally FALSE (resp. TRUE).

Unfortunately, it is not always feasible to impose special requirements like these on the scheduler. Furthermore, race-prone (asynchronous) interactions on shared memory between threads may be inherent to the level of abstraction at which the program is to be analysed—for example, at the operating-system level, or including the implementation of synchronisation primitives. This obliges us to verify that each program thread satisfies a *timing-sensitive* notion of noninterference: specifically, one that rejects the program if it has any internal timing leaks (relative to the scheduler) observable via race-prone

shared memory. This timing sensitivity has follow-on implications both for **compiler** verification, and for verifying programs with secret-dependent control flow:

- Compilers (hardware aside! [31]) tend to optimise as aggressively as possible to make the program run as fast as possible. Consequently, the soundness of any source-level program verification of timing-sensitive noninterference rests on imposing more nuanced compiler verification requirements (regarding timing), than any typically imposed on a production-quality compiler for a mainstream programming language. However, practical approaches to verifying that a compiler preserves timing-sensitive notions of noninterference are only recently beginning to be explored [11, 12]. Thus, this thesis adds to that body of work, by exploring the satisfiability of requirements specialised to mixed-sensitivity concurrent programs [67, 66].

- As timing leaks stem from dependence of timing behaviour on secrets, a common approach (followed by the first few contributions of this thesis) is to avoid precise source-level reasoning about time by disallowing secret-dependent control flow—for example, disallowing if (h) conditionals to prevent any timing leaks from h.

However, a strength of timing-sensitive notions of noninterference proposed recently for mixed-sensitivity concurrent programs [67, 65] is to be compatible with such precise source-level reasoning about the time taken by such control flow paths. Thus, this thesis presents (as a final contribution) an example of such reasoning.

#### 1.1.2 Mixed-sensitivity reuse: Scaling with the number of customers

As previously mentioned, the program verification problem also becomes more challenging when (imagining that we are threads in a concurrent program) my coworkers and I want to reuse any shared space between us to serve two or more mutually distrusting parties.

Under these circumstances, we cannot use a shortcut that makes proving confidentiality easy: calling a workspace permanently tainted if it is used for a given customer A, and then never using it to serve customer B, and vice versa. This is because if we were to use this shortcut, we would need two permanently dedicated workspaces: one for customer A, and the other for customer B. Then, if we served sixty thousand customers, we would need sixty thousand workspaces—this is clearly inefficient, if there is nothing stopping us from flushing the content of one customer before reusing the workspace for another. Furthermore, if we do not know how many customers we are liable to have, we would not even know how many workspaces to set aside. Note that, in a nutshell, it was this impetus for flexible reuse of shared resources—to prevent inefficiency and over- or underprovisioning—that in large part led to the rise to supremacy of cloud architectures.

Rather, any analysis we develop must account more generally for the possibility that a workspace might be used for customer A at one moment, and for customer B the next. The only conceivable way to do this predictably is to have the dedication of that workspace be coordinated by values handled or calculated by the program itself (e.g. as in Figure 1.2).

```

if (current_customer = 0) {

customer_A := workspace;

} else {

customer_B := workspace;

}

```

Figure 1.2: Example of mixed-sensitivity reuse—here, of the workspace, depending on the value of current\_customer.

The security property must therefore be *value dependent* [103, 51, 64] to account for the dynamically changing dedication of the workspace, meaning the analysis must be flow sensitive (Section 1.1.1) enough to track the values on which that property is dependent.

As foreshadowed in Section 1.1.1, however, such value-dependent coordination and its flow-sensitive analysis may be complicated by concurrency. Consider the (pseudocode) example program in Figure 1.2: If workspace contains customer B's data, but another thread overwrites current\_customer with 0, the program will incorrectly deliver the data to customer A. It is in this sense that, as mentioned in Section 1.1.1, functional-correctness issues can become security issues; thus, program functionality coordinating mixed-sensitivity reuse needs to be protected from concurrency, with values calculated needing to be analysed just as seriously as their sensitivity levels. Consequently, mitigations against concurrency's interference with a program thread's functionality (see Section 1.2.1) will become critical to protect also the confidentiality of such programs.

In short, the challenges so far can be summed up as follows: A program with mixed-sensitivity reuse inevitably features value-dependent coordination of that reuse, therefore requiring a flow-sensitive security analysis to track the changes in those values; however, as just mentioned in Section 1.1.1, concurrency interferes with that flow-sensitive analysis.

Then on top of that, we would ideally be able to support verification of a wider variety of software architectures, that might allow a given worker thread to service n customers, or where one customer is serviced (perhaps for m different purposes) by m worker threads. Developing techniques for verifying such programs poses the challenge of finding ways to reason about how worker threads coordinate the dedication of resources to customers, without necessarily tying together workers with customers in a 1:1 relationship. This means managing how formalisms for coordinating customer–resource dedication (see Section 1.2.2) interact with those for coordinating worker–resource access (see Section 1.2.1).

#### 1.1.3 Compositionality: Scaling with the size of the software project

Finally, the proof effort for any techniques that this thesis develops (for handling concurrency and mixed-sensitivity reuse) needs to scale with the size of the software project, in terms of the number of distinctly developed software components it comprises.

Particularly, the program verification effort should scale *compositionally*, meaning proof effort on each software component is possible without (yet, or possibly

ever) knowing the internal details of all the other software components in the system. Furthermore, the compiler verification theorem should ensure that the compiler preserves the compositionality of whatever confidentiality property it is preserving.

This thesis will focus on the development of techniques that scale and compose proof effort for an arbitrary number of worker threads as software components, assuming that the code run by each thread forms a natural area of responsibility or ongoing maintenance in a long-term software development for a concurrent program. When considering worker threads as software components, this adds to the concerns of scalability raised in Section 1.1.1, because while a proof technique may vastly reduce the complexity of an analysis, it may still not be compositional—a notable example is Owicki and Gries [74].

In contrast however, this thesis will simplify to the typical basic case of servicing two customers, assuming that verifying for an arbitrary number of customers amounts to repeated applications of the basic case. We leave to future work any issues of scale in verifying for an arbitrary number of customers (e.g. as in Lourenço and Caires [51]).

#### 1.2 Approaches taken by this thesis

In Section 1.1, I described how the problems of scale addressed by mixed-sensitivity concurrent programs beg for methods of coordination—between worker threads, and towards their cooperative dedication of resources to customers serviced—and how they must give rise to program- and compiler-verification efforts that scale compositionally in the number of threads. Here I will talk about the approaches chosen for dealing with those two challenges of coordination (described in Sections 1.2.1 and 1.2.2 respectively), and for proving that a compiler preserves noninterference for mixed-sensitivity concurrent programs (Section 1.2.3). Finally I describe briefly the methodology for experimenting with the improvements and the application of all of these approaches (Section 1.2.4).

#### 1.2.1 Assume–guarantee contracts, on worker–resource access

This thesis continues a line of experimentation on the adaptation to noninterference verification [54, 64, 67] of assume-guarantee [54] (another name for rely-guarantee [41]), a method for achieving compositional analysis for concurrent programs.

In these confidentiality-focused adaptations of assume—guarantee, inter-thread interference is limited by the use of assumptions (also known as rely conditions) that other worker threads will not write to certain areas of the shared space. Inadvertent leakage of intermediate values is handled using a more confidentiality-centric kind of assumption (as pioneered by Mantel et al. [54]), that other workers will not read from certain areas.

However, as is standard for assume—guarantee, the greater ease of per-thread analysis (due to assumptions) is paid for by proof obligations to establish certain *guarantees* (corresponding to those assumptions). The first focus of this thesis is on a method for proving *all* of these contractual obligations on resource access by threads—these were only partially proved by any known instantiation [33, 65] of the preceding theories [54, 67].

#### 1.2.2 Value-dependent classification, for customer-resource dedication

Static classification of locations corresponds to the inflexible scenario illustrated in Section 1.1.2, in which workspaces tainted by data belonging to a given customer must be classified as belonging to that customer for all time. In contrast, mixed-sensitivity reuse requires dynamic changes to the classification of locations.

This thesis continues experimentation in the literature [64, 67] on confidentiality properties that support value-dependent classification schemes, in which the classification of a location can change dynamically in a manner dependent on values currently held in other locations. This implies a recognition of which of the variables in the program—termed the control variables [64]—are significant for controlling the classification of other variables. (In Figure 1.2, current\_customer would likely control the classification of workspace.)

For control variables to function as an effective means of coordinating customer–resource dedication, these approaches require the instantiator of the theory to demonstrate the satisfaction of certain requirements in the treatment of these variables—for example, the requirement that sensitive information belonging to one customer be flushed from a shared location, before it is reclassified to belong to another customer.

#### 1.2.3 Confidentiality-preserving refinement, for compiler verification

Tying the above concerns together, this thesis gauges the applicability to compiler verification of notions of *confidentiality-preserving refinement* [66, 85], that specifically preserve a timing-sensitive, assume–guarantee-supporting notion of noninterference with value-dependent classification policies [67, 65].

This seeks to mirror the usual approaches of large-scale compiler verification efforts like CompCert [48] and CakeML [47] of using various notions of refinement to prove preservation of program semantics—but in this case, satisfying a notion of refinement expressly designed to preserve security while tackling the difficulties raised in Section 1.1.

#### 1.2.4 Machine-checked formalisation and proof

All theories described in this thesis are simplified presentations of theories formalised [84] in Isabelle/HOL (Isabelle's higher-order logic) [71], with development of the theories having proceeded using the Isabelle interactive proof assistant as a development environment.

The Isabelle/HOL theories for this thesis [84] build directly on top of the previous Isabelle formalisations [65, 66] of Murray et al. [67]—work I assisted prior to this thesis—which in turn had extended the Isabelle-based formalisation [33] of Mantel et al. [54].

#### 1.3 Overview of contributions

This thesis evaluates the feasibility of formal methods (1) for verifying noninterference—total absence of information flow between certain designated locations—for a mixed-sensitivity concurrent software program, and (2) for having that noninterference verifi-

cation proof effort be carried down to a target language semantics by a one-time compiler verification proof effort. Consequently, compiling the threads of such a program yields a concurrent program that also satisfies noninterference.

An extension of the program verification method is also presented, allowing some forms of secret-dependent control flow (as a foundation for future extensions of the compiler).

#### 1.3.1 Completion of a program verification method

Chapter 4 presents the first contribution of this thesis: a novel set of per-thread techniques that is sufficient to prove noninterference for mixed-sensitivity concurrent programs. They show programming-language designers that assume—guarantee makes it feasible to prove that their synchronisation primitives make these proofs compositional.

Specifically I extend, for a generic imperative language, a prior set of proof techniques by Murray et al. [67, 65] whose compositionality was conditional on some unproved requirements. I add mutex lock-based synchronisation primitives to that language, and prove that their semantics maintains the needed compositionality requirements as an invariant of program execution. I also add type-checking rules for the new primitives accordingly, and prove the updated rule sets remain sound. The requirements proved are also from Murray et al. [67, 65], and I present them as formal preliminaries in Chapter 3.

The work of Chapter 4 led to a program logic (with additional features falling outside the scope of this thesis; see Section 2.2.4) that establishes security for mixed-sensitivity concurrent programs using mutex locks, presented in the following paper:

• [68] Toby Murray, Robert Sison, and Kai Engelhardt. COVERN: A logic for compositional verification of information flow control. In *European Symposium on Security and Privacy*, pages 16–30, London, United Kingdom, April 2018. IEEE.

#### 1.3.2 Demonstration of a compiler verification method

Chapter 5 then presents the second contribution of this thesis: the first compiler proved to preserve proofs of noninterference for mixed-sensitivity concurrent programs. This shows compiler developers that decomposition principles make it more feasible to prove that compilers satisfy noninterference-preserving notions of refinement.

Specifically I implement an Isabelle/HOL function that compiles programs from the language of Chapter 4 to a generic RISC-style assembly language, adapted from a compilation scheme originally intended for fault-resilience [95]. I then prove that this compiler satisfies a confidentiality-preserving notion of refinement from Murray et al. [67, 66], using a decomposition principle (falling outside the scope of this thesis) published alongside the compiler [85]. I present these background notions as formal preliminaries in Chapter 3.

The work of Chapter 5 appeared in the following paper:

• [85] Robert Sison and Toby Murray. Verifying that a compiler preserves concurrent value-dependent information-flow security. In 10th International Conference on

Interactive Theorem Proving (ITP 2019), volume 141, pages 27:1–27:19, Portland, USA, September 2019. Schloss Dagstuhl – Leibniz-Zentrum für Informatik.

#### 1.3.3 Demonstration of program verification, preserved by a compiler

Chapter 6 presents the third and central contribution of this thesis, resting on those of Chapters 4 and 5: the first significant mixed-sensitivity concurrent program proved to satisfy a noninterference property, preserved by a compiler down to an assembly-level model. This validates the central claim of this thesis, that proving confidentiality and its preservation by a compiler is feasible for such programs.

Specifically I implement, in the language of Chapter 4, a model of an actual non-trivial mixed-sensitivity concurrent program serving a real-world use case: the software-componentised input-handling regime for the *Cross Domain Desktop Compositor* [13] (CDDC). I then exercise the proof techniques of Chapter 4 on each thread to yield a proof of noninterference for the model. Finally, I show that it is straightforward to use the proofs about the compiler of Chapter 5 to obtain noninterference automatically for a RISC-style assembly language model of the program, output by the compiler.

A demonstration of all these methods on a two-component variant of the CDDC inputhandling model appeared in the paper Sison and Murray [85] (noted by Section 1.3.2) that presented the contributions of Chapter 5. As case study, this thesis presents a threecomponent model that is more faithful to the CDDC input handler's original C-language implementation than the two-component model verified and compiled by Sison and Murray [85]. This three-component model previously appeared in the paper Murray et al. [68] (noted by Section 1.3.1), except that the version in this thesis checks certain functional properties at runtime, instead of discharging them using the general assume—guarantee verification support added by the COVERN logic [68].

#### 1.3.4 Program verification extension for secret-dependent control flow

Although secret-dependent control flow is compatible with the underlying theory of Murray et al. [67] on which this thesis rests, the contributions of Chapters 4 and 5 as applied in Chapter 6 disallow it—a practice common in the literature when proving confidentiality.

To address this, Chapter 7 presents a fourth and final contribution: the first instance of syntax-directed reasoning about secret-dependent control flow for mixed-sensitivity concurrent programs. This shows programming-language designers that security type systems are capable of such reasoning.

Specifically I add to the security type system of Chapter 4 a rule that admits limited forms of conditional branching on secrets, and prove that it remains sound. In short, the rule ensures the absence of any timing leaks that are convertible to storage leaks, assuming a scheduler making decisions according to the same notion of time.

This final contribution is intended to facilitate future work on extending the compiler of Chapter 5 to allow noninterference-preserving compilation of such programs.

# Chapter 2

# Review of related formal methods

As explained in Chapter 1, this thesis is about proving particular forms of a family of confidentiality properties referred to broadly as *noninterference* [32], and its preservation by a compiler, that are designed to cater to mixed-sensitivity concurrent programs.

After introducing the basic forms of noninterference properties and what distinguishes them from the more typical safety properties (Section 2.1), this chapter will present a literature review divided into each of the two problems introduced in Chapter 1—program verification (Section 2.2) and compiler verification (Section 2.3)—gradually narrowing in on the aspects of those problems most relevant to this thesis. A formal presentation of preliminaries from background work on these topics will be given separately, in Chapter 3.

#### 2.1 Defining noninterference

The term "noninterference", as used in the field of security verification, was coined by Goguen and Meseguer [32] to mean: "what the first group (of users) does... has no effect on what the second group of users can see." The literature typically refers to this first and second group respectively as the *high* and *low* user or classification.

This thesis will mostly focus on definitions of noninterference that assert that any two initial states of some program that "look the same" to that low-classified group of users must execute with semantics that also "look the same" to that group. Overloading  $\simeq$  to denote some formal notion of (low-)observational equivalence both (1) between states and (2) between behaviours of the program (to a low user), and using  $\llbracket \sigma \rrbracket$  to denote its behaviour when executed with initial state  $\sigma$ , these definitions broadly take the form:

$$\forall \sigma_1 \ \sigma_2. \ \sigma_1 \simeq \sigma_2 \longrightarrow \llbracket \sigma_1 \rrbracket \simeq \llbracket \sigma_2 \rrbracket$$

Noninterference properties are 2-safety [96] hyperproperties [20]: Two executions are necessary to refute noninterference, whereas safety properties can be refuted by a single execution. A counterexample pair of executions to noninterference, when formalised as just shown, indicates a leakage of information in the form of some difference in the state visible to low user, resulting from differences in some part of the state that cannot be seen

by them—such "hidden" differences could have only resulted from the high user. Formally:

$$\exists \sigma_1 \ \sigma_2. \ \sigma_1 \simeq \sigma_2 \land \llbracket \sigma_1 \rrbracket \not \simeq \llbracket \sigma_2 \rrbracket$$

Information leakage was first formalised in this manner in 1977 by Cohen [22], who termed that leakage a *strong dependency*, and formalised confidentiality in terms of its negation—some 5 years before Goguen and Meseguer [32]. Defining confidentiality in much the same form, seemingly independently of Cohen [22] in the mid-90s, Volpano et al. [99] described it as "noninterference-like", and the name has stuck ever since.

The style of noninterference definition described so far can be contrasted to purge-based definitions, which more closely follow Goguen and Meseguer [32]: These instead compare the behaviour of a program before and after applying a "purge" function that removes secrets from an input to the program. Overloading  $\simeq$  to denote low-observational equivalence between input strings, and  $\llbracket w \rrbracket$  to denote the program's behaviour when executed on input string w, Goguen and Meseguer's noninterference took the form:

$$\forall w. \|w\| \simeq \|\mathsf{purge}(w)\|$$

Note that this is just as much a 2-safety hyperproperty; it is refuted by a counterexample pair of executions of the program that have different observable semantics before and after purging secrets from the input string—that is,  $\exists w. \ \llbracket w \rrbracket \not\simeq \llbracket \mathsf{purge}(w) \rrbracket$ .

## 2.2 Program verification: Proving noninterference

This section will review the literature on improving the precision of analyses (Section 2.2.1) seeking to establish noninterference, and on having these analyses support programs with mixed-sensitivity reuse (Section 2.2.2) and concurrency, in a manner that is compositional across the concurrently running threads (Section 2.2.3). (The formal preliminaries provided in Chapter 3 will then centre on a particular form of noninterference from the literature that combines all three concerns.) After a brief discussion of works contemporary with and subsequent to the work in this thesis that also reconcile mixed-sensitivity reuse and concurrency compositionally (Section 2.2.4), the final part of this literature survey on program verification will focus on related works' decision of whether to allow or disallow secret-dependent control flow (Section 2.2.5). (That topic will be the focus of Chapter 7.)

#### 2.2.1 With better precision, through flow sensitivity

Although Jones and Lipton [39] proved that it is impossible to construct a fully automated sound method of information-flow policy enforcement that is also *complete*—does not reject any secure programs—research in this area has steadily improved the *precision* of methods, so that they accept more and more secure programs. These approaches thereby seek to retain greater scope for automation and pose less practical difficulties than complete

methods like relational Hoare logics [14, 15] and self-composition [7, 96]. (Needless to say, proving *soundness*—rejection of all insecure programs—is broadly treated as compulsory.)

This thesis will focus on security type systems for achieving language-based security, an idea first proposed and demonstrated by Volpano et al. [99]—at the time, as a reformulation of a security analysis method (described by Denning and Denning [25]) to make it amenable to a soundness proof. In their security type system, each variable in the system was given a security type that corresponds exactly to a classification (there called "security class") that does not vary over time. In this way, a violation (e.g. assignment l := h, from a sensitive source h of type High to an untrusted sink of type Low) can be identified instantly just by comparing the security types of the variables involved in a given command.

A body of work surveyed by Hunt and Sands [36] has focused on gaining precision through greater flow sensitivity—in short, the ability to base security judgements on things that happen before or after a given point in the program (i.e. sensitivity to position in the control flow [19]). Consider for example the program l := h; l := 0 against an attacker who can only observe the final value of each variable (thanks to Hunt and Sands [36]). A flow-insensitive analysis (like that of Volpano et al. [99]) would reject the assignment l := h as insecure—in effect, asserting perfect recall [34] of l's entire history, despite the attacker only observing l's final value. To allow the l := h assignment in these situations, flow-sensitive security type systems "allow the type of a variable to float" [36] by having typing environments track the sensitivity of the data in each variable (e.g.  $\Gamma :: Var \Rightarrow \{\text{High}, \text{Low}\}\)$  as the analysis progresses through the control flow of the program. They then only enforce at the end of the program that untrusted sinks (like l in our example) no longer contain secrets (e.g. for some final typing environment  $\Gamma'$ , that  $\Gamma' l \neq \text{High}$ ).

Clearly this kind of reasoning, on account of being sensitive to state, implicitly and broadly assumes both (1) the *stability* of that state—that is, the absence of changes to the values in the locations involved—and (2) that no other parties are able to read from any relevant locations at intermediate points of the program. It is important to note that while such assumptions are perhaps reasonable for sequential programs, they will come under threat upon introducing concurrency (in Section 2.2.3). This caveat will apply to any other improvements in precision that rely on tracking or making use of extra information about the state of the program—such as the "context sensitivity" (using knowledge about the object hosting the current method, in an object-oriented environment) offered by the JOANA tool [89].

#### 2.2.2 With mixed-sensitivity reuse, through value dependence

We now turn to the emergence of confidentiality proof techniques precise enough to allow reuse of locations for data of differing sensitivity levels at different times. This requires judgements of security to be *value dependent*, which in turn means analyses must be flow sensitive (discussed Section 2.2.1) enough to track any runtime changes to those values. (Recalling the example of Figure 1.2, to prevent assigning the data in workspace to the

wrong customer, the assignment would likely be judged secure or not depending on the value of current\_customer, which therefore must be tracked by a flow-sensitive analysis.)

Zheng and Myers [102, 103] were the first to present a formal soundness proof for a security type system with judgements dependent on values that can *change* at runtime (not merely differ between runs, as achieved by Tse and Zdancewic [97] shortly beforehand). Subsequent formally proved-sound security type systems with value dependence include those for the Fine [92] and F\* [93] languages, and the dependent information-flow types of Lourenço and Caires [51]—these each differed in how they map values to sensitivity levels. Costanzo and Shao [23] showed furthermore that proving a value-dependent notion of security is just as possible using a program logic that tracks assertions about state, in the usual fashion for separation logics [72, 77] and other Floyd–Hoare-like logics [29, 35].