# THE UNIVERSITY OF NEW SOUTH WALES SCHOOL OF COMPUTER SCIENCE AND ENGINEERING

# A PHYSICALLY-ADDRESSED L4 KERNEL

Abi Nourai

Bachelor of Engineering (Computer Engineering)

March 2005

Supervisor: Gernot Heiser Assessor: Kevin Elphinstone

### Abstract

All current implementations of the L4 microkernel map thread control blocks (TCBs) into a linear array in virtual memory, a decision that was originally made almost entirely for the performance advantages it offers on the Intel 486 platform. The drawback of this design choice is that page faults generated within L4 complicate the kernel and in particular its verification by formal methods.

An alternative exists however on architectures where physical addressing, or at least a loose equivalent in superpages, is available. On such architectures, TCBs may be addressed physically via indirection provided by an auxiliary lookup table. Addressing TCBs in this manners leads to a completely physically-addressed L4 kernel that offers advantages in simplicity, but has a non-obvious effect on the cache footprint of the performancecritical IPC path that warrants examination.

This thesis endeavours to provide a thorough investigation into the performance trade-offs involved in making the L4Ka::Pistachio implementation of the L4 Version 4 API completely physically addressed. We stress architectural issues that effect the outcome of these trade-offs and explore various implementational design choices that aim to weaken the performance penalties a physically-addressed kernel may suffer. We conclude by running Linux on top of the L4 microkernel to obtain a concise set of benchmarks that prove, at least for the MIPS64 architecture, that the simplicity of a completely physically-addressed L4 kernel may be enjoyed without any notable performance degradation.

## Acknowledgements

I would like to thank all those members of the DiSy group at the University of New South Wales who freely volunteered their guidance and wisdom to me over the course of my thesis. It was a pleasure to work with such a diverse but tightly-knit group of people.

I would especially like to thank Carl van Schaik and Matthew Chapman for allowing me to invade their cubicles unannounced as often as I pleased. The many hours of help they provided was far beyond the call of duty, and proved invaluable to my work.

My supervisor, Gernot Heiser, also deserves special mention for providing me with the opportunity to work on such an interesting and challenging project. His encouragement, feedback and standards of excellence made the last 12 months the most rewarding year of my engineering degree.

# Contents

| 1 | Intr                                                                        | oduction                                                                                                                                                                                  |                                       | 1                                                                                                                                                          |

|---|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 | Bac                                                                         | kground                                                                                                                                                                                   |                                       | 4                                                                                                                                                          |

|   | 2.1                                                                         | 0                                                                                                                                                                                         | Memory                                | 4                                                                                                                                                          |

|   |                                                                             | 2.1.1                                                                                                                                                                                     | Address translation                   | 4                                                                                                                                                          |

|   |                                                                             | 2.1.2                                                                                                                                                                                     | The translation lookaside buffer      | 5                                                                                                                                                          |

|   |                                                                             | 2.1.3                                                                                                                                                                                     | Benefits of virtual memory            | 5                                                                                                                                                          |

|   | 2.2                                                                         |                                                                                                                                                                                           | Caches                                | 6                                                                                                                                                          |

|   |                                                                             | 2.2.1                                                                                                                                                                                     | The memory hierarchy and locality     | 6                                                                                                                                                          |

|   |                                                                             | 2.2.2                                                                                                                                                                                     | The memory cache                      | 7                                                                                                                                                          |

|   | 2.3                                                                         | Threads                                                                                                                                                                                   | · · · · · · · · · · · · · · · · · · · | 10                                                                                                                                                         |

|   |                                                                             | 2.3.1                                                                                                                                                                                     | Execution abstraction                 | 10                                                                                                                                                         |

|   |                                                                             | 2.3.2                                                                                                                                                                                     | Thread control blocks                 | 10                                                                                                                                                         |

|   | 2.4                                                                         | The L4 I                                                                                                                                                                                  | Microkernel                           | 11                                                                                                                                                         |

|   |                                                                             | 2.4.1                                                                                                                                                                                     | The microkernel concept               | 11                                                                                                                                                         |

|   |                                                                             | 2.4.2                                                                                                                                                                                     | Microkernel performance               | 11                                                                                                                                                         |

|   |                                                                             | 2.4.3                                                                                                                                                                                     | L4 concepts and abstractions          | 12                                                                                                                                                         |

|   |                                                                             | 2.4.4                                                                                                                                                                                     | Inside L4Ka::Pistachio                | 15                                                                                                                                                         |

|   |                                                                             |                                                                                                                                                                                           |                                       |                                                                                                                                                            |

| 3 | Phys                                                                        | sically-Ad                                                                                                                                                                                | ldressed L4 Kernel                    | 17                                                                                                                                                         |

| 3 | <b>Phy</b><br>3.1                                                           | •                                                                                                                                                                                         | Idressed L4 Kernel Addressing Defined | <b>17</b><br>17                                                                                                                                            |

| 3 | •                                                                           | Physical                                                                                                                                                                                  | Addressing Defined                    |                                                                                                                                                            |

| 3 | 3.1                                                                         | Physical<br>Address                                                                                                                                                                       |                                       | 17                                                                                                                                                         |

| 3 | 3.1                                                                         | Physical<br>Address<br>3.2.1                                                                                                                                                              | Addressing Defined                    | 17<br>18                                                                                                                                                   |

| 3 | 3.1                                                                         | Physical<br>Address<br>3.2.1<br>3.2.2                                                                                                                                                     | Addressing Defined                    | 17<br>18<br>18                                                                                                                                             |

| 3 | 3.1                                                                         | Physical<br>Address<br>3.2.1 3<br>3.2.2 1<br>3.2.3 7                                                                                                                                      | Addressing Defined                    | 17<br>18<br>18<br>18                                                                                                                                       |

| 3 | 3.1<br>3.2                                                                  | Physical<br>Address<br>3.2.1 3<br>3.2.2 3<br>3.2.3 7<br>Address                                                                                                                           | Addressing Defined                    | 17<br>18<br>18<br>18<br>19                                                                                                                                 |

| 3 | 3.1<br>3.2                                                                  | Physical<br>Address<br>3.2.1 3<br>3.2.2 1<br>3.2.3 7<br>Address<br>3.3.1 1                                                                                                                | Addressing Defined                    | 17<br>18<br>18<br>18<br>19<br>19                                                                                                                           |

| 3 | 3.1<br>3.2                                                                  | Physical         Address         3.2.1         3.2.2         3.2.3         Address         3.3.1         3.3.2                                                                            | Addressing Defined                    | 17<br>18<br>18<br>18<br>19<br>19<br>19                                                                                                                     |

| 3 | 3.1<br>3.2                                                                  | Physical         Address:         3.2.1         3.2.2         3.2.3         Address:         3.3.1         3.3.2         3.3.3                                                            | Addressing Defined                    | 17<br>18<br>18<br>19<br>19<br>19<br>20                                                                                                                     |

| 3 | 3.1<br>3.2<br>3.3                                                           | Physical<br>Address<br>3.2.1 3<br>3.2.2 1<br>3.2.3 7<br>Address<br>3.3.1 1<br>3.3.2 1<br>3.3.3 1<br>A Simpl                                                                               | Addressing Defined                    | 17<br>18<br>18<br>19<br>19<br>19<br>20<br>20                                                                                                               |

| 3 | 3.1<br>3.2<br>3.3                                                           | Physical         Address         3.2.1         3.2.2         3.2.3         Address         3.3.1         3.3.2         3.3.3         A Simpl         3.4.1                                | Addressing Defined                    | 17<br>18<br>18<br>19<br>19<br>19<br>20<br>20<br>21                                                                                                         |

| 3 | 3.1<br>3.2<br>3.3                                                           | Physical         Address:         3.2.1         3.2.2         3.2.3         Address:         3.3.1         3.3.2         3.3.3         A Simpl         3.4.1         3.4.2                | Addressing Defined                    | 17<br>18<br>18<br>19<br>19<br>20<br>20<br>21<br>21                                                                                                         |

| 3 | 3.1<br>3.2<br>3.3                                                           | Physical         Address         3.2.1         3.2.2         3.2.3         Address         3.3.1         3.3.2         3.3.3         A Simpl         3.4.1         3.4.2         3.4.3    | Addressing Defined                    | 17<br>18<br>18<br>19<br>19<br>20<br>20<br>20<br>21<br>21<br>22                                                                                             |

| 3 | 3.1<br>3.2<br>3.3<br>3.4                                                    | Physical<br>Address:<br>3.2.1 2<br>3.2.2 1<br>3.2.3 7<br>Address:<br>3.3.1 1<br>3.3.2 1<br>3.3.2 1<br>3.3.3 1<br>A Simpl<br>3.4.1 1<br>3.4.2 1<br>3.4.3 4<br>A Cavea                      | Addressing Defined                    | 17<br>18<br>18<br>19<br>19<br>20<br>20<br>21<br>21<br>22<br>22                                                                                             |

| 3 | <ul> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>3.5</li> </ul> | Physical<br>Address:<br>3.2.1 2<br>3.2.2 1<br>3.2.2 1<br>3.2.3 7<br>Address:<br>3.3.1 1<br>3.3.2 1<br>3.3.2 1<br>3.3.3 1<br>A Simpl<br>3.4.1 1<br>3.4.2 1<br>3.4.3 4<br>A Cavea<br>A Comp | Addressing Defined                    | <ol> <li>17</li> <li>18</li> <li>18</li> <li>19</li> <li>19</li> <li>20</li> <li>20</li> <li>21</li> <li>21</li> <li>22</li> <li>22</li> <li>23</li> </ol> |

|    | 3.7    | Transla | ting Thread Identifiers in L4Ka::Pistachio | 26     |

|----|--------|---------|--------------------------------------------|--------|

|    |        | 3.7.1   | Validating thread identifiers              | 27     |

|    |        | 3.7.2   | System calls                               | 28     |

|    |        | 3.7.3   | Locating the current thread control block  | <br>28 |

| 4  | Deci   | on & Im | nplementation                              | 29     |

| 7  | 4.1    |         | iction to the MIPS R4700                   | 29     |

|    | 4.2    |         | IPS64 IPC Fastpath                         | 31     |

|    | 7.2    | 4.2.1   | Criteria                                   | 32     |

|    |        | 4.2.2   | Data-cache footprint                       | 32     |

|    |        | 4.2.3   | TLB footprint                              | 36     |

|    | 4.3    |         | of the ThreadID Table                      | 36     |

|    | 1.5    | 4.3.1   | Address format                             | 36     |

|    |        | 4.3.2   | Data structures                            | 37     |

|    |        | 4.3.3   | Maximising cache-line value                | 39     |

|    |        | 4.3.4   | A threadID-table cache                     | 42     |

|    | 4.4    |         | nentation & Analysis                       | 46     |

|    | т.т    | 4.4.1   | Selecting threadID-table designs           | 46     |

|    |        | 4.4.2   | Nine concrete implementations              | 46     |

|    |        | 4.4.3   | Implementational drawbacks                 | 50     |

|    |        | 4.4.4   | Implementation summary                     | 51     |

|    |        | 4.4.4   |                                            | <br>51 |

| 5  | Eval   | uation  |                                            | 53     |

|    | 5.1    | Factors | Influencing Performance                    | <br>53 |

|    |        | 5.1.1   | ThreadID-table design                      | <br>53 |

|    |        | 5.1.2   | User-level operating-system design         | 54     |

|    |        | 5.1.3   | Architectural properties                   | 54     |

|    | 5.2    | Evaluat | tion Environment                           | <br>56 |

|    |        | 5.2.1   | The U4600                                  | <br>56 |

|    |        | 5.2.2   | Microkernel                                | 57     |

|    |        | 5.2.3   | Linux on L4                                | 58     |

|    | 5.3    |         | tion Methodology                           | 60     |

|    |        | 5.3.1   | Benchmarks                                 | 60     |

|    |        | 5.3.2   | Cache behaviour                            | 61     |

|    |        | 5.3.3   | Measurements                               | <br>62 |

|    | 5.4    |         | s & Analysis                               | 63     |

|    | 0.1    | 5.4.1   | Benchmark Set #1                           | 63     |

|    |        | 5.4.2   | Benchmark Set #2                           | 70     |

|    |        | 5.4.3   | Benchmark Set #3                           | 71     |

|    | 5.5    |         | sions & Discussion                         | 73     |

|    | 5.5    | Conciu  |                                            | <br>15 |

| 6  | Epil   | ogue    |                                            | 75     |

| A  | Thre   | ead Con | trol Block Layout                          | 76     |

| B  | The    | IPC Fas | stpath                                     | 77     |

| Bi | bliogr |         | -                                          | 89     |

|    |        | J       |                                            | ~ ~    |

# **List of Figures**

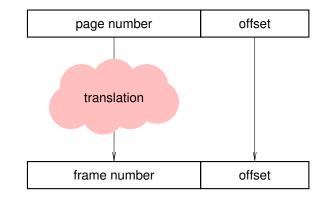

| 2.1 | Address translation.                                                                                   | 4  |

|-----|--------------------------------------------------------------------------------------------------------|----|

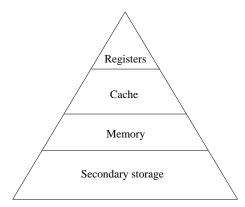

| 2.2 | A typical memory hierarchy.                                                                            | 6  |

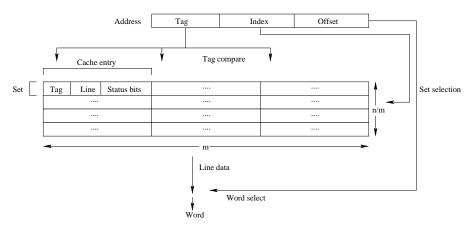

| 2.3 | The cache-lookup operation.                                                                            | 7  |

| 2.4 | A global thread identifier in L4.                                                                      | 13 |

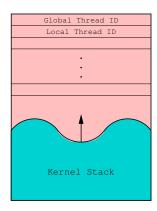

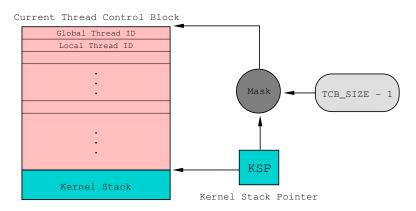

| 2.5 | Per-thread kernel stacks in L4 reside in each thread's TCB.                                            | 15 |

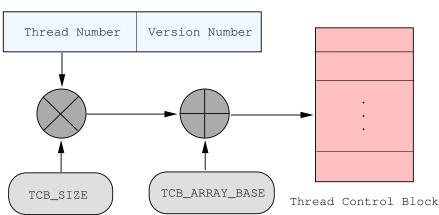

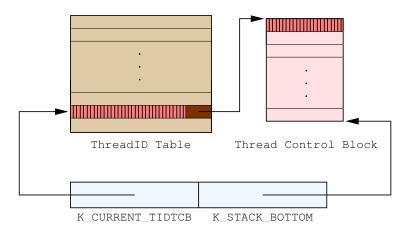

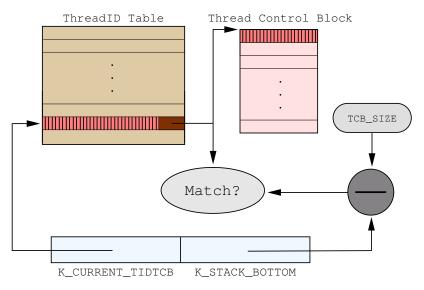

| 3.1 | Directly addressing thread control blocks.                                                             | 19 |

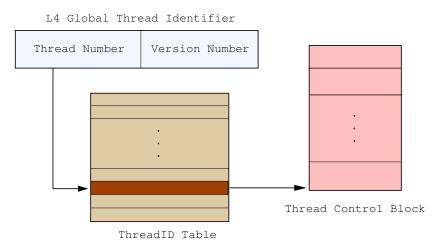

| 3.2 | Indirectly addressing thread control blocks.                                                           | 20 |

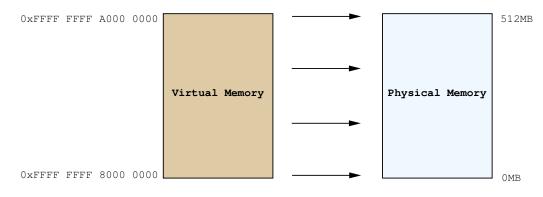

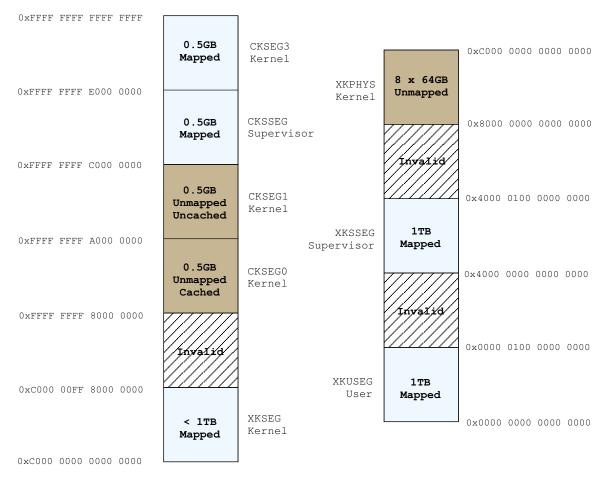

| 3.3 | Physical addressing on the MIPS R4700                                                                  | 25 |

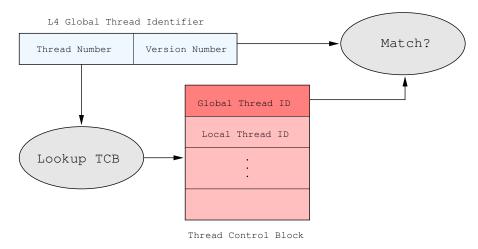

| 3.4 | Validating thread identifiers in L4.                                                                   | 27 |

| 3.5 | L4 system calls that perform thread control block lookups                                              | 28 |

| 3.6 | Locating the current thread's thread control block.                                                    | 28 |

| 4.1 | Address-space layout on the MIPS R4700                                                                 | 31 |

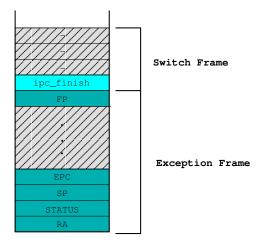

| 4.2 | Exception and switch frames on the MIPS64 IPC-fastpath kernel stack.                                   | 34 |

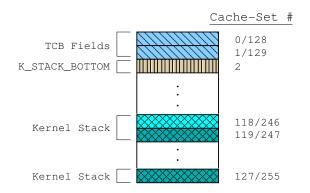

| 4.3 | Data-cache colouring of the MIPS64 IPC fastpath.                                                       | 35 |

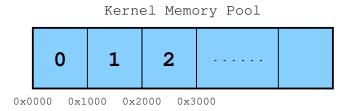

| 4.4 | Partitioning the kernel memory pool into tcb_size chunks, numbered consecutively from zero.            | 37 |

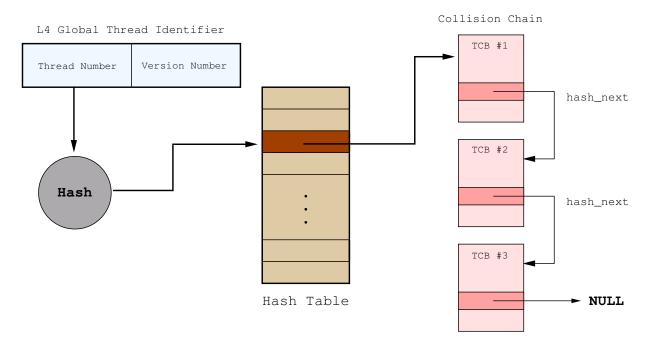

| 4.5 | A hash-table data structure for the threadID table.                                                    | 38 |

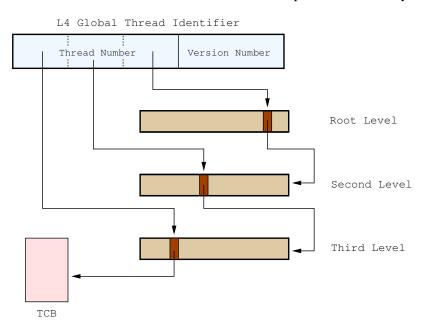

| 4.6 | A hierarchial-table data structure for the threadID table                                              | 39 |

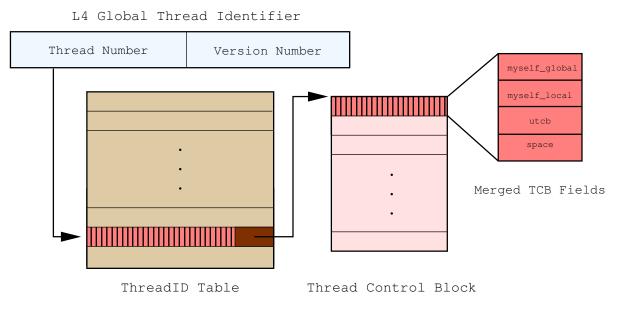

| 4.7 | A threadID table where each entry duplicates a subset of TCB fields                                    | 40 |

| 4.8 | Locating the current thread's threadID-table entry on the MIPS64.                                      | 42 |

| 4.9 | Determining if the current thread's threadID-table entry is still present in the threadID-table cache. | 45 |

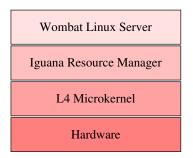

| 5.1 | Iguana and Wombat servers.                                                                             | 58 |

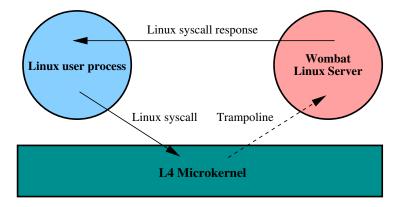

| 5.2 | Linux system-call convention implemented via trampoline                                                | 59 |

# **List of Tables**

| 4.1 | MIPS64 general-purpose register set                                                            | 29 |

|-----|------------------------------------------------------------------------------------------------|----|

| 4.2 | Thread-control-block fields referenced by the MIPS64 IPC fastpath                              | 33 |

| 4.3 | Number of cache lines the MIPS64 IPC fastpath references from thread-control-block memory      | 35 |

| 4.4 | Best-case IPC-fastpath performance of our kernel implementations on the MIPS R4700             | 51 |

| 4.5 | IPC fastpath (open-wait) instruction-cache footprint of our kernel implementations.            | 52 |

| 5.1 | Benchmark results for simulating a file-server workload.                                       | 64 |

| 5.2 | Profiling results for TLB behaviour when simulating a file-server workload                     | 64 |

| 5.3 | Profiling results for IPC activity when simulating a file-server workload                      | 64 |

| 5.4 | Benchmark results for kernel compilation with GCC.                                             | 65 |

| 5.5 | Profiling results for TLB behaviour when compiling a kernel with GCC.                          | 65 |

| 5.6 | Profiling results for IPC activity when compiling a kernel with GCC                            | 65 |

| 5.7 | Benchmark results for threadID-table cache performance when simulating a file-server workload. | 70 |

| 5.8 | Benchmark results for near-worst-case threadID-table cache performance when simulating a       |    |

|     | file-server workload.                                                                          | 70 |

| 5.9 | TLB performance for the kern_virt kernel when compiling a kernel with GCC.                     | 72 |

# **Chapter 1**

# Introduction

L4 is a second-generation microkernel based on the axioms of minimality, extensibility and flexibility. It offers all the advantages of the classical microkernel approach without suffering the performance degradation exhibited by earlier microkernels. The L4 philosophy is founded on the principle that providing only a minimal set of abstractions leads to improved efficiency and flexibility. The documented success of L4 compared to the so-called first generation microkernels validates this philosophy.

The approach adopted by L4 in minimising what is contained in the kernel not only improves performance, but also offers advantages in simplicity. The L4Ka::Pistachio implementation of the L4 API contains in the order of 10,000 lines of C++ and assembly code — an order of magnitude smaller than the first-generation Mach microkernel and two orders of magnitude smaller than the Linux kernel. A microkernel of this size becomes a strong candidate for formal verification, a process by which the kernel source code can be shown to meet correctness and security constraints by mathematical proof. Formally verifying a microkernel is highly desirable because its correctness, reliability and robustness are a prerequisite for the correct and safe execution of any user-level application.

It is a characteristic of software development however, that striving for improved performance often runs counter to simplicity. In particular this is true for the manner in which current implementations of the L4 microkernel choose to address a critical class of kernel-maintained data structures called thread control blocks (TCBs). All current L4 implementations map TCBs into a linear array in virtual memory, a decision that was originally made almost entirely for the performance advantages it offers on the Intel 486 platform. Unfortunately this design choice implies that execution of kernel code cannot be assumed to be sequential, because the occurrence of page faults and, depending on the architecture, TLB-miss exceptions, may interrupt the kernel's smooth operation. This impedes the formal verification process by complicating the development of an accurate formal model representative of the kernel's behaviour.

The alternative to addressing TCBs as a virtual linear array is to address TCBs physically, but indirectly through a lookup table. The motivation for the latter approach is to obtain a completely physically-addressed kernel that is simpler because it is void of the possibility of page faults being generated from within the kernel. On the surface it would appear that this goal is only achievable on architectures that support physical addressing of memory. However we will show that architectures supporting superpages are equally capable of eliminating page faults from within the kernel. In particular this goal is attainable for every architecture for which there currently exists an implementation of L4Ka::Pistachio.

For the Intel 486 platform where L4 was originally implemented, it is not difficult to show that the current method of addressing TCBs offers significant performance advantages over addressing TCBs through a lookup table. However for computer architectures that permit physical addressing, or at least a loose equivalent in superpages, the performance implications associated with physically addressing TCBs are ambiguous and need

to be thoroughly evaluated. To understand why, one must first appreciate what is required of a microkernel to achieve high levels of performance.

Comparisons between L4 and first-generation microkernels such as Mach have highlighted that efficient inter-process communication (IPC) provided by the microkernel is a prerequisite for overall system performance to be fast. In particular, studies have shown that the cache footprint of a microkernel's IPC mechanism must be small if system performance is not to suffer. The underlying thesis that any microkernel implementation must respect is that IPC may be invoked sufficiently frequently on a microkernel-based system that user-level servers and applications must perpetually compete for any portion of the system's caches consumed by IPC primitives.

It has been well established that current implementations of L4 offer highly efficient IPC that is an order of magnitude faster than that found in first-generation microkernels. A small cache footprint largely contributes to the performance achievements of L4. It turns out that choosing to physically address TCB structures impacts on the nature of this cache footprint. On one hand, table lookups required to perform TCB physical addressing potentially increase the usage of a system's memory caches. On the other hand, dispensing with virtual addressing relieves pressure on the translate lookaside buffer (TLB). Although the performance trade-offs associated with physically addressing TCBs are more intricate than this alone, the non-trivial impact a physically-addressed L4 microkernel will have on the performance-critical IPC path is enough to warrant a thorough performance analysis of such a microkernel. The overriding goal of our work is to provide that analysis.

In this thesis we modify the L4Ka::Pistachio implementation of the L4 API so as to obtain a physicallyaddressed L4 kernel that can be subjected to scrutiny via benchmarking. In doing so, a number of implementational design choices are explored, each seeking to weaken any performance penalties a physically-addressed kernel may endure. The investigation itself is largely conducted in the context of the MIPS R4700 64-bit processor. Despite this, we ensure to highlight any architectural properties that have a particularly strong influence on our analysis and results so that we can anticipate a physically-addressed kernel's performance impact on other hardware platforms.

Our evaluation is performed in two stages. In the first stage we perform a series of microbenchmarks that quantify the precise impact a physically-addressed kernel has on the performance-critical IPC path. Both cycle counts and cache footprint are considered. In the second stage we run Linux on top of the L4 microkernel so that we can investigate the overall effect a physically-addressed kernel has on a non-trivial L4-based system. We use the AIM7 multiuser benchmark suite in conjunction with traditional kernel compiles to produce a concise set of results demonstrating that, at least for the MIPS R4700 platform, the simplicity gained from a completely physically-addressed L4 kernel may be enjoyed without any notable performance degradation.

## **Thesis Outline**

#### **Chapter Two: Background**

Chapter two presents the background material required for the remaining chapters in this thesis. It begins by describing the memory-management subsystem on modern architectures — an understanding of which is required for appreciating the subtleties of the trade-offs associated with a physically-addressed kernel. The chapter concludes with an introduction to the L4 microkernel, describing its key concepts and abstractions, and highlighting any implementational properties of L4Ka::Pistachio that prove relevant to our work.

#### Chapter Three: Physically-Addressed L4 Kernel

Before investigating the trade-offs involved with making the L4Ka::Pistachio implementation of L4 completely physically addressed, this thesis first establishes a foundation by not only describing, but also rationalising, the

current state of addressing in Pistachio. It turns out that addressing thread control blocks (TCBs) within the kernel is the major impediment to obtaining a physically-addressed kernel.

We ensure to explain why current implementations of L4 all choose to address TCBs virtually, and then proceed to motivate the quest for removing virtual addressing from within Pistachio. In particular we explain why not having to handle page faults within the kernel leads to simplicity, and why this simplicity is worth striving for. The third chapter concludes with a qualitative architecture-independent exposition of both the performance and non-performance trade-offs associated with physically addressing TCB structures.

#### **Chapter Four: Design & Implementation**

In Chapter four, this thesis turns to addressing the performance impact of a physically-addressed Pistachio kernel. We conduct our analysis in the context of the MIPS64 architecture and focus particularly on the effect on the performance-critical IPC path. A number of implementational design choices are proposed that aim to reduce performance penalties a physically-addressed kernel may suffer from. Chapter four concludes with a presentation of a number of concrete physically-addressed kernel implementations whose impact on the performance-critical IPC path is carefully analysed.

#### **Chapter Five: Evaluation**

Chapter five evaluates the performance of the concrete physically-addressed kernel implementations introduced in the preceding chapter. By running Linux on top of the L4 microkernel, traditional and standardised benchmarks are used to quantify the overall effect these kernels have on an L4-based system. Throughout this chapter, a strong emphasis is placed on appreciating the influence architectural properties and implementational design choices have on benchmark results.

#### **Chapter Six: Epilogue**

The concluding chapter summarises the achievements of this thesis and then proposes a course for future work that addresses any shortcomings.

# **Conventions and Caveats**

- When referring to the L4 microkernel unqualified, we are specifically referring to L4 as defined by the *eXperimental* Version X.2 API. When referring to the L4Ka::Pistachio implementation of the L4 API, we specifically refer to the Version 0.4 release of L4Ka::Pistachio made by the L4Ka team in June 2004.

- New keywords are generally introduced *emphasised*. Code snippets are typeset using typewriter font. Acronyms are capitalised. L4 system calls are typeset in SMALL CAPS. For example, IPC should be treated as the acronym for inter-process communication, but IPC refers specifically to the L4 system call that performs inter-process communication.

- It is somewhat unfortunate that the TCB acronym is overloaded in the literature. It is used as an acronym for both *trusted computing base* and for the *thread control block* data structure. Throughout this document, the TCB acronym is always used to mean the latter. When we need to refer to the former, we use the unabbreviated form to avoid confusion.

Furthermore, when referring to L4 TCBs unqualified, we specifically refer to the kernel-maintained TCBs (KTCBs) and not the user-accessible TCBs (UTCBs). When there is scope for confusion, we shall explicitly use the KTCB and UTCB acronyms.

# **Chapter 2**

# Background

This thesis is concerned with investigating the trade-offs associated with obtaining a completely physicallyaddressed L4 kernel. Understanding the subtlety of these trade-offs requires an understanding of the memorymanagement subsystem of modern architectures. Hence this thesis begins with an introduction to two of the most important elements of modern memory-management units — virtual memory and caches. It concludes with an introduction to the L4 microkernel.

# 2.1 Virtual Memory

### 2.1.1 Address translation

Figure 2.1: Address translation.

The usefulness of a *microprocessor* resides in its ability to execute programs. Doing so requires data (instructions and operands) to be fetched from and stored to *physical memory*. The location of such data in physical memory is called its *physical address*. Permitting programs to access physical memory directly violates the principle of *independence* in that programs may access and modify other programs' data without restriction. It is a principal task of the operating-system kernel to provide this independence.

For the above reason, amongst others, modern-day operating systems and hardware work together to create a *virtual memory* for programs to execute in. Virtual memory is an abstraction of a system's storage (which includes physical memory). When a program executes in virtual memory, it addresses memory by issuing *virtual addresses* instead of physical addresses. A hardware device called the memory-management unit (MMU) lies

between the CPU and memory and has the responsibility of translating these virtual addresses into physical addresses. A *virtual address space* is a set of such virtual to physical mappings.

It is the operating system's responsibility to actually define the virtual to physical translations. These translations occur at the granularity of *pages*. A page is a block of contiguous virtual addresses and is mapped to an equally-sized contiguous block of physical addresses called a *frame*. Depending on the given architecture and operating system, pages may be of fixed or varying size. On architectures that support multiple page sizes, the larger page sizes are often called *superpages*.

Each page in virtual memory is numbered consecutively by a *virtual page number*. Frames in physical memory are similarly numbered by a *physical frame number*. The operating system manages virtual memory by maintaining a data structure called a *page table*. The implementation of page tables varies across operating systems and often depends on the underlying architecture [22]. Despite the variance in implementation, each page-table entry (PTE) typically not only maps a virtual page number to a frame number, but also maintains meta-data such as access rights for that page.

#### 2.1.2 The translation lookaside buffer

A fundamental operation in the virtual memory abstraction is the translation of virtual to physical addresses whenever virtual memory is addressed. A naive implementation of this translation would require a consultation of the page table on every such access. Since the page table itself is contained in memory, this would at the least double the number of memory accesses performed by a process and hence lead to potentially intolerable performance degradation.

To alleviate the overheard in performing address translation, most systems provide a hardware device called the *translation lookaside buffer* (TLB) to hold a subset of address-space mappings. The TLB is a hardware cache of page-table entries, and the operating system's page tables serve as a backing store for that cache.

Upon addressing virtual memory, the MMU first examines the TLB with the appropriate virtual page number in hope of finding a valid mapping to a physical frame number. If found, the MMU hardware validates the access (using protection attributes stored with the TLB translation) and locates the data in physical memory. If the TLB does not contain a valid mapping, a *TLB miss* occurs and the page table must be searched for the correct entry so that it can be placed into the TLB. This operation is referred to as a *TLB refill*.

Depending on the underlying architecture, a TLB refill may be performed either by hardware or software (operating system). Hardware-walked page tables offer faster refill times at the expense of flexibility in page-table structure and simpler hardware design. If the TLB cannot be refilled because the page table contains no valid mapping, a *page fault* is said to have occurred. Page faults are handled by the operating system.

A TLB is said to *cover* a set of virtual addresses if it contains valid mappings for those virtual addresses. The total set of virtual addresses covered by a TLB is referred to as the *TLB's coverage*. Since TLBs only cache a small number of PTEs (typically 32–256 entries) and pages are (typically) only a few kilobytes in size, a TLBs coverage is only a small fraction of the entire virtual address space. Hence to be effective, the TLB's coverage must encompass the working set of currently executing programs so that the costs saved by avoiding memory access (significantly) outbalance the costs incurred by performing TLB refills.

#### 2.1.3 Benefits of virtual memory

Since a primary objective of this thesis is to implement a completely physically-addressed L4 kernel, it is appropriate to describe the benefits of virtual addressing so that later we can later ascertain what impact (if any) the forfeiting of these benefits has for the kernel.

• Virtual memory provides a basis with which an operating system can prevent processes executing in different address spaces from interfering with each other. That is, operating systems may use virtual address spaces to provide independence and security to user-level programs.

- The access right attributes associated with each mapping of a virtual page to a physical frame permits the operating system to protect memory access at page granularity and have this protection enforced by hardware. This makes it possible, for example, to protect programs from modifying their own text segments (by marking them read-only).

- Virtual memory permits user processes to address their data without knowing (or assuming) its actual location in physical memory.

- The operating system may provide shared memory access for processes executing in different address spaces by mapping virtual pages in their respective address spaces to identical physical frames.

- Virtual memory permits the kernel to implement *demand paging* transparently to user processes.

- Virtual memory allows programs to access data in an address space larger than that provided by physical memory, and in fact provides a uniform view of all storage devices in a system that the operating system chooses to map virtual memory to.

# 2.2 Memory Caches

It turns out that our physically-addressed kernel increases the pressure exerted on a performance-critical component of modern architectures called the memory cache. Much of this thesis is devoted to understanding and evaluating the performance impact this increased pressure implies. To do so, however, we must first understand cache architecture and cache operation on modern architectures.

#### 2.2.1 The memory hierarchy and locality

There is an abundance of devices that a microprocessor can use for storing and retrieving data. These devices can be characterised by their capacity, speed and cost. In an ideal world, storage would be as large, cheap and fast as one desired. Unfortunately in the real world, the aforementioned storage characteristics are diametrically opposed to each other— devices with fast access times, for example, are generally smaller and more expensive than those with slower access times.

Figure 2.2: A typical memory hierarchy.

The trade-offs amongst the three key characteristics of storage devices presents a dilemma that is solved by organising these storage devices into what is called a *memory hierarchy*. As one ascends the memory hierarchy, access times decrease at the expense of size and cost. The memory hierarchy endeavours to provide a large

storage capacity characteristic of the device at the lowest level of the hierarchy, but at a speed only attainable by devices at the higher levels of the hierarchy. It is the *principle of locality* that makes this goal realisable.

Modern applications exhibit two types of locality: *temporal* locality and *spatial* locality. A program exhibits temporal locality when recently-referenced memory locations are likely to be referenced again in the near future. Spatial locality implies that data nearby recently-referenced memory locations are likely to be soon referenced themselves. When locality is strong, storage devices at the upper levels of the memory hierarchy are more frequently accessed than devices at the lower levels. Because of this, the memory hierarchy is able to create the illusion of a low latency but high capacity storage device being available to computer programs.

#### 2.2.2 The memory cache

Modern computer architectures place a small but high-speed memory called a *cache* between the system's physical memory and the processor. Such a cache forms a critical component of modern memory hierarchies, typically appearing between a processor's register set and main memory. When a processor references main memory, it first checks for the presence of the appropriate data in the memory cache. If the data is found in the cache a *cache hit* is said to have occurred and main memory need not be consulted. Otherwise a *cache miss* has taken place and the cache is (usually) refilled with the appropriate data from main memory.

#### **Cache operation**

Caches are organised as a fixed number of *cache sets*. Each cache set contains an identical number of entries called *cache lines*. The structure of cache lines varies between architectures, but at a minimum each cache line contains a fixed amount of cached data, a cache tag and some status bits. The cache tag, together with the encompassing cache set, uniquely identifies the location of the cached data in memory. The status bits typically include a valid bit and a dirty bit. The valid bit indicates whether the cache line holds valid data that may be used by the processor. When a cache line is marked as valid, the dirty bit indicates whether the cached data is consistent with the corresponding data held in main memory.

Figure 2.3: The cache-lookup operation.

The process by which data is fetched from a cache is called a *cache lookup* and is depicted in Figure 2.3. The address of the main-memory location being referenced serves as the input to this process. The index bits of the input address index the memory cache to select a cache set. A cache hit occurs precisely when the tag bits of the input address matches against the cache tag of any one the cache lines contained in the selected set, provided that cache line is also marked as valid.

In the special case where a cache contains exactly one cache set, the set-indexing operation becomes trivial and hence the cache-lookup process derives to the task of comparing the tag bits of the input address with the cache tag of every entry in the cache. Such a cache is described as a *fully-associative* cache. At the other extreme, a cache whose cache sets all contain exactly one cache line is known as a *direct-mapped* cache. More generally, an *m*-way *set-associative* cache is a memory cache where each cache set contains exactly *m* cache lines. Hence an *m*-way set-associative cache containing a total of *n* cache lines is a direct-mapped cache precisely when m = 1 and fully associative when m = n.

#### **Cache addressing**

The address of the main-memory location being referenced serves as the input to the cache-lookup process. The index bits in this address are used to select a cache set, and the tag bits are used to select a cache line from within that set. Thus far we have neglected to specify whether the input address is virtual or physical. In fact not only are both types of address possible, but the index bits and tag bits used in the cache lookup need not both be derived from a physical address, nor need they be both derived from a virtual address. This gives rise to four distinct possibilities — physically-indexed physically-tagged caches, virtually-indexed physically-tagged caches, and virtually-indexed physically-virtually caches.

The trade-offs associated with each of the four cache-addressing methods are intricate, and for the most part beyond the scope of this thesis. We shall however pay particular attention to virtually-indexed virtually-tagged caches because they share an important property with TLBs. The interested reader can find a more thorough comparison of cache-addressing methods in *UNIX Systems for Modern Architectures* [40].

#### Virtually-addressed caches

For each valid cache line there is a corresponding memory location whose contents are cached. When a cache is virtually tagged these memory locations are necessarily virtual addresses. In particular, this is true for virtually-indexed virtually-tagged caches — more succinctly referred to simply as *virtually-addressed* caches. Because virtual addresses are always tied to a particular address space, this implies that the contents of a virtually-addressed cache are tied to a particular addressing context.

Virtually-addressed caches are therefore faced with a dilemma when the current addressing context changes (that is, when an address-space switch occurs). The simplest solution to this problem is to perform a *cache flush* on every address-space switch so that the contents of the virtually-addressed cache are written back to main memory and then declared invalid. Cache flushing however is an expensive operation. There are direct costs associated with performing the cache-flush operation itself, and more importantly, potentially crippling indirect costs associated with reestablishing a process's entire cache working set on each address-space switch.

A virtually-addressed cache need not perform a complete flush however if the address space being switched to does not overlap with the address space being switched from. In this special case the contents of the virtually-addressed cache are not made ambiguous on address-space switch and may therefore remain present in the cache provided they are not accessible.

More generally however, a virtually-addressed cache can only avoid a complete cache flush on address-space switch if each valid cache line is identified with the address space it is tied to. For example, if each address space is bestowed a unique numeric *address-space identifier* (ASID) and each cache line is tagged with the ASID of its corresponding address space, then cache entries no longer become ambiguous when the addressing context changes. Hence a virtually-addressed cache tagged with ASIDs need not flush its contents on every address-space switch.

Recall that the translation lookaside buffer introduced in Section 2.1.2 is indexed and tagged by virtual page numbers which are themselves derived from virtual addresses. Hence the cached entries of a translation lookaside buffer are also tied to a particular addressing context. We note that the same mechanisms that may be

used to avoid flushing virtually-addressed caches can, in particular, also be used to avoid flushing the translation lookaside buffer on address-space switch.

#### **Cache misses**

Cache misses can be categorised into three different groups [38]:

- 1. A cache miss is said to be a *compulsory miss* when the cache is not completely full and the new cache entry does not replace an existing valid entry in the cache. Compulsory cache misses, for example, occur immediately after a cache flush has been performed.

- 2. *Conflict misses* occur when competition between cache lines within a set causes a new cache entry to displace another valid cache line within the same set. The more associative a cache is, the less likely it is for conflict misses to occur. Hence direct-mapped caches exhibit the highest levels of conflict misses.

- 3. A *capacity miss* is said to have occurred when the sole cause of a cache miss is insufficient cache capacity. Such a cache miss occurs independently of the level of associativity in the cache. In particular it would still occur if the cache were fully associative.

When a cache miss occurs, the cache is generally refilled by obtaining the referenced data from main memory. For a direct-mapped cache there is no dilemma as to which cache line the new cache entry should replace. However caches with higher levels of associativity must choose which cache line in the appropriate cache set to replace. This choice function is governed by the cache's *replacement algorithm* or *replacement policy*. Ideally the replacement algorithm would replace the cache line that is least likely to be used in the near future. Determining such a cache line is in general an impossible task. Nevertheless, feasible algorithms exist that most often perform reasonably effectively. Three common replacement algorithms employed by caches are *first-in first-out* (FIFO), *least-recently-used* (LRU) and *pseudo-random replacement* [43].

#### **Cache write policies**

When a processor performs a write to a memory location whose contents are present in the memory cache, it may either write the data into both the cache and physical memory, or it may choose to only write the data into the cache. The former is referred to as a *write-through* cache policy and the latter is referred to as a *write-back* cache policy. When write-back is used, modified cache lines are marked as dirty to identify that their contents are no longer consistent with main memory.

The rationale behind *write-back* is to reduce memory traffic as main memory then only needs to be written to when dirty cache lines are mapped out of the cache. The advantage of write-through, however, is to simplify cache-consistency issues, which is particularly appreciated on multi-processor systems and by I/O modules performing direct memory access [42].

When a processor performs a write to a memory location whose contents are not present in the memory cache, it may choose to either write the data directly to memory but not perform a cache refill, or it may choose to first perform a cache refill and then update the contents of the cache. The former is referred to as a *no-write-allocate* policy and the latter is referred to as a *write-allocate* policy. Write-back caches most often employ a write-allocate policy in hope that subsequent writes will be captured by the cache. Write-through caches however most often employ a no-write-allocate policy since subsequent writes will still need to go to main memory.

# 2.3 Threads

It turns out that to obtain a physically-addressed L4 microkernel, we must first alter the way in which a class of kernel-maintained data structures called *thread control blocks* are addressed by the kernel. Hence it is appropriate to discuss the use and purpose of these data structures within L4.

#### 2.3.1 Execution abstraction

A *thread* is an abstraction of an execution unit on the CPU. It consists of an *instruction stream* executing within a known *context*. At a minimum a thread's context comprises of the address space in which the thread executes, and the contents of the CPU's registers during its execution. The CPU register set typically consists of an instruction and stack pointer, general purpose registers and system control and status registers.

Most operating-system kernels are responsible for multiplexing the execution of numerous threads on a single CPU. At certain points in time the operating system may perform a *context switch* to change the currently executing thread. A context switch involves the saving of the currently executing thread's context followed by the restoration of a suspended thread's context.

#### 2.3.2 Thread control blocks

An operating-system kernel maintains a per-thread data structure called the *thread control block* (TCB). The thread control block is where a thread's state is saved to or restored from on a context switch. Additionally, the TCB holds thread-specific meta data required for the kernel's management of that thread. Typical TCB fields include:

- a thread identifier that uniquely identifies the thread;

- a characterisation of the thread's current state (e.g. running, suspended);

- execution context (address space and registers);

- scheduling parameters (e.g. thread priority, timeslice, total quantum);

- queues for managing inter-process communication.

Thread control blocks (along with page tables) are perhaps the most important data structures maintained by an operating-system kernel. In fact TCBs implement the thread abstraction for a kernel. Much of this thesis is concerned with investigating and evaluating different methods of addressing TCBs within the context of the L4 microkernel. We have already presented an introduction to addressing and to TCBs. It remains to introduce the L4 microkernel.

## 2.4 The L4 Microkernel

L4 is a second-generation microkernel based on the principles of minimality, extensibility, and flexibility. It offers all the advantages of the classical microkernel concept without suffering performance degradation symptomatic of the previous generation of microkernels. The L4 project was originally established by Jochen Liedtke in the 1990s and today is actively researched by the L4Ka team at the University of Karlsruhe in collaboration with the DiSy group at the University of New South Wales and the Dresden University of Technology.

Formally, L4 is defined by a platform-independent<sup>1</sup> API and a platform-dependent ABI. Our work is predominantly concerned with L4 as defined by the L4 *eXperimental* Version X.2 kernel API [27] which we hitherto refer to more succinctly as the L4 Version 4 API or the L4 v4 API. L4Ka::Pistachio [26] implements the L4 v4 API and is available on a variety of widely-used architectures including the MIPS64 [14], ARM [24] and IA-32 (Pentium and above) [19] platforms.

In this section we provide a brief introduction to the microkernel concept and identify how L4 distinguishes itself from earlier microkernels. We then proceed to describe the key L4 abstractions and implementational issues that prove relevant to this thesis.

#### 2.4.1 The microkernel concept

Traditionally, the term *kernel* is used to describe the component of the operating system that is either mandatory to all other software, or executes on the underlying architecture at an elevated privileged level [33]. Historically, most operating systems employed a large monolithic kernel. In such systems, all the services provided by the operating system were contained in the kernel itself.

In contrast, the *microkernel* approach aims to minimise the kernel, implementing conventional operatingsystem services such as file systems, device drivers and even memory management outside the kernel wherever possible. Such services run in user mode and are viewed by the microkernel no differently than any other user-level application.

From the software-engineering point of view, the microkernel concept offers some clear advantages over the classical, large, integrated, monolithic kernel approach. These advantages include (but are not limited to) improved flexibility, extensibility, reliability and security. For an in-depth exposition of the software-technological advantages of microkernels we direct the reader to the literature [33]. More relevant to this thesis are the performance implications of microkernels and the L4 philosophy.

#### 2.4.2 Microkernel performance

Early microkernels such as Amoeba [46], Chorus [39] and Mach [11] were notoriously noted for suffering from excessive performance limitations. For example, Mach on a DEC-Station 5200/200 was found to endure peak degradations of up to 66% when compared to Ultrix running on the same hardware [3], and Mach-based OSF/1 is cited to perform on average at only half the performance level of monolithic OSF/1 [5].

It is well understood that exporting traditional operating-system services as user-level processes running on a microkernel inherently leads to an increased number of user-kernel mode switches and an increased number of address-space switches. Deeper investigation of the performance degradation suffered by early microkernels has, however, highlighted *inter-process communication* (IPC) as the chief cause of their performance overhead [2, 5, 13, 33].

For a microkernel exporting the client-server paradigm, IPC is the fundamental mechanism provided for communicating between different subsystems co-existing on the microkernel. IPC is invoked frequently enough on microkernel-based systems that overall system performance is dependent on IPC performance [29]. Not only

<sup>&</sup>lt;sup>1</sup>As an exception, we note that the L4 v4 API does distinguish between 32-bit and 64-bit architectures — but never in a processor-specific manner.

must the direct costs of IPC be minimised, but indirect costs in terms of cache footprint must also be considered. Research first conducted by Chen and Bershad [3] and later further analysed by Liedtke [30] demonstrated that up to 73% of the overhead suffered by a user-level Ultrix server running on Mach when compared to native Ultrix was accounted for by IPC-related activities and that 20% of the total system cache misses suffered by user-level Ultrix were caused by user-level competition. In particular, the instruction-cache working set of Mach was cited as a principal bottleneck to achieving user-level Ultrix performance comparable to that of monolithic Ultrix.

The response to this performance degradation is what distinguishes the so-called first-generation microkernels from second-generation microkernels. The response adopted by first-generation microkernels such as Mach and Chorus was to reintegrate critical operating-system servers and drivers back into the microkernel [2, 5]. Although this architectural change reduced both IPC overhead and the number of user-level and address-space switches, it sacrificed much of the software-technological benefits promoted by the microkernel movement.

In contrast, second-generation microkernels such as L4 [32], Exokernel [10] and QNX [16] are based on the thesis that efficiency is derived from providing only a minimal set of microkernel abstractions. In particular, the L4 microkernel supplies only three key abstractions in threads, address spaces and IPC and implements a total of only eleven system calls [27]. It offers lean but super-fast IPC that not only provides the foundation for user-level device drivers and memory management, but also performs an order of magnitude faster than earlier counterparts with only 10–20% of the cache footprint [32,34]. Härtig et al. [13] demonstrated that Linux running on top of L4 under AIM multiuser workloads [1] was capable of achieving performance levels within 5–8% of native Linux whereas MkLinux [6] — Linux running on top of a first-generation Mach-derived microkernel — suffered an average performance degradation of 49%.

#### 2.4.3 L4 concepts and abstractions

L4 provides a minimal set of abstractions in threads, address spaces and inter-process communication (IPC) that can be used to construct a wide range of operating-system policies at user level. Because the L4 microkernel serves as a centrepiece for this thesis, we provide a more thorough introduction to these concepts in the following. We pay particular attention to threads, thread identifiers and IPC, as these abstractions especially form the focus of much of our work.

#### Threads

Threads form the basic execution unit in L4. They are created, manipulated and destroyed via the THREAD-CONTROL system call. Every thread executes within an L4 address space that constitutes its protection domain. A thread may migrate to different address spaces over the course of its life.

Each thread is associated with two special threads, a *pager* and a *scheduler*. A thread's pager is responsible for handling page faults generated by that thread. A thread's scheduler dictates its priority, timeslice length and other scheduling parameters. An optional *exception handler* may be associated with a thread to handle any exceptions it raises.

We note that in L4, hardware interrupts are abstracted as threads to permit the use of user-level device drivers. The occurrence of a hardware interrupt is then represented by an IPC message from the hardware-interrupt thread to a user-level interrupt handler that implements the device driver for that interrupt.

#### **Thread identifiers**

Every thread in L4 has both a *global* and *local* thread identifier (thread ID). Global thread IDs are, as the name suggests, unique throughout the entire system. On the other hand, the scope of a local thread ID is limited to that thread's own address space. It is the global thread ID that we will chiefly be interested in. Hence hitherto we shall simply refer to global thread IDs as *thread IDs* unless there is danger of causing confusion with local thread IDs.

A thread ID consists of a single word (hence its size differs on 32-bit and 64-bit architectures), but contains two distinct parts — a thread number and a version number. The upper 18-bits of the thread ID on 32-bit architectures, and the upper 32-bits on 64-bit architectures, encode the thread number. The remaining lower bits of the thread ID word encode the thread's version number.

Figure 2.4: A global thread identifier in L4.

At any point in time, at most one thread with a given thread number may exist. The thread version number is assigned by user-level servers (with appropriate privileges) and is not used internally by the L4 kernel except to verify the validity of global thread IDs passed to it from user threads (via system calls). Any implementation of the L4 v4 API may choose an upper limit of thread numbers it supports, provided the limit is one less than a power-of-two and can be encoded into the appropriate upper bits of a thread ID word. The L4 implementation exports this upper limit to user level via the KERNELINTERFACE system call. We call the range of thread numbers made available by an L4 implementation the *thread-number space*.

There are two special thread IDs reserved by the L4 API — NilThread and AnyThread. The former is guaranteed not to match any thread's identifier and the latter is guaranteed to match every thread's identifier. The NilThread is implemented as a word whose bits are all set to zero, and the AnyThread identifier is implemented as a word whose bits are all set to one. We will revisit these special thread IDs when discussing L4 IPC in Section 2.4.3.

#### **Address spaces**

Because L4 address spaces play a minor role in this thesis, we only provide a brief description of their construction and manipulation. The interested reader can find a more thorough treatment in Liedtke's *On*  $\mu$ -*Kernel Construction* [30] and in the L4 *eXperimental* Version X.2 reference manual [27].

L4 provides the mechanism for implementing recursively-defined virtual address spaces that are managed completely at user level. Each address space is defined in terms of at least one parent address space, with the exception of the  $\sigma_0$  address space that acts as the root address space and represents physical memory. The *map*, *grant* and *unmap* primitives are used to recursively construct L4 address spaces [30]. The map operation maps memory regions called *fpages* [27] from one address space into another. The grant operation is similar but also removes the mapping from the source address space once it has been transferred. The unmap primitive is used to revoke mappings.

Page faults in L4 are abstracted by the microkernel by representing them as special messages delivered via IPC. When a thread generates a page fault, the microkernel fabricates a page-fault IPC message from the faulting thread to its associated pager. The contents of this message include the address of the faulting instruction and the address that was faulted upon. Upon receiving the page-fault message, the pager can respond (via IPC) with an address-space mapping that will permit execution of the faulting thread to continue.

#### **Inter-process communication**

Inter-process communication (IPC) is the fundamental mechanism provided by the L4 microkernel for synchronisation and communication between threads. L4 IPC is additionally used to abstract and propagate page faults, hardware interrupts and exception events to user-level servers.

L4 provides message-based, synchronous IPC between threads. Hence an IPC operation in L4 transfers a message from a sending thread to a destination thread if and only if the destination thread has agreed to the exchange by invoking a corresponding IPC operation.

Every thread in L4 owns 64 *virtual message registers*. These registers are mapped to real hardware registers or to memory locations as dictated by the processor-specific L4 ABI [27]. The simplest form of IPC simply transfers a subset of these virtual registers from source to destination. In such a transfer, the data contained in the virtual registers are called *untyped* because the microkernel imposes no semantics on them.

A more complicated form of IPC in L4 transfers *typed* items between threads. Typed items have semantics imposed on them by the microkernel and fall into two distinct categories — those that are used to map and unmap memory regions (fpages) between address spaces, and those that are used to transfer memory buffers. For historic reasons dating back to the Version 2 L4 API (and earlier) [9,31], IPC involving transfer of memory buffers between address spaces is often referred to as *Long IPC*.

#### The IPC system-call interface

In theory, synchronous IPC can be provided by a kernel via two system calls — SEND and WAIT — each accepting a thread identifier as the sole parameter. In this case a round-trip send-and-reply IPC message between two threads would require four system calls and in particular four user-kernel mode switches to take place. Instead L4 offers a single IPC system call that accepts two thread identifiers as input — a to-thread specifier and a from-thread specifier. When a thread invokes this IPC primitive, it sends a message to the thread identified by to-thread, and then waits for a message from the thread identified by from-thread. In effect, the IPC primitive in L4 combines the logical SEND and WAIT operations into a single IPC system call. This allows a round-trip send-and-reply IPC between two threads to take place with only half the number of user-kernel mode switches.

In the special case where the to-thread parameter is NilThread, an invocation of the IPC system call only executes the wait phase of the IPC. We term this specific type of IPC a *wait-only* IPC. Likewise, when the from-thread specifier is NilThread, the IPC system call only executes a send operation, skipping the wait phase. We term these *send-only* IPCs. A thread may also invoke the IPC system call with AnyThread as the from-thread specifier. This indicates that the thread, once it has completed the send phase of the system call, is willing to accept an IPC message from any L4 thread. We call this special case an *open-wait* IPC and call any other invocation of the IPC system call involving a wait-phase a *closed-wait* IPC<sup>2</sup>. A special case of closed-wait IPCs occurs when the to-thread specifier is identical to the from-thread specifier — signifying that the source thread expects a reply from the send-phase recipient and is not willing to accept IPC from any other threads. We describe these as *call* IPCs.

We conclude by noting that the L4 IPC system call also accepts a third parameter that can be used to specify (possibly different) timeout constraints for the send and wait phases of an IPC invocation. Two special timeouts are the Zero timeout and the Forever timeout. As an example of their use, a send-only IPC with a Zero timeout will not complete if the destination thread is not already blocked in the wait phase of an IPC invocation. A thread performing a wait-only IPC system call with a Forever timeout and the from-thread specifier set to its own thread ID will block forever.

#### User thread control blocks

The L4 API provides a *lazy thread switching* mechanism with which intra-address space IPC may be performed without entering kernel mode [35]. The purpose of this is to avoid the performance penalty of user-kernel mode switches when performing a frequently invoked subset of IPC system calls. This mechanism however requires at a minimum, a thread's user stack pointer and thread status be made visible to other threads executing in its address space. Traditionally, a thread's stack pointer and status are maintained in kernel-protected TCB structures. Since it would be dangerous to make TCBs entirely user accessible, support for lazy switching

<sup>&</sup>lt;sup>2</sup>In the L4 v4 API, threads are also able to specify that they are only willing to accept IPC messages from threads executing in the same address space as themselves. We choose to ignore this special case as it currently has no implementation in L4Ka::Pistachio.

necessitates dividing each TCB into a *kernel TCB* (KTCB) and a *user TCB* (UTCB). The KTCB is kernel protected whereas the UTCB is made available to user threads (executing in the same address space as the UTCB's owner).

In L4, UTCBs also serve as an efficient way for user-level threads to communicate with the kernel. In particular, a thread's virtual registers that are not mapped to hardware register are actually mapped to memory locations inside its UTCB. Which virtual registers are mapped into the UTCB and at what offset is specified by the L4 processor-specific ABI [27].

It should be mentioned that our work is concerned almost entirely with KTCBs rather than UTCBs. Hence we shall refer to KTCBs simply as TCBs unless there is potential for confusion.

#### 2.4.4 Inside L4Ka::Pistachio

L4Ka::Pistachio is an implementation of the L4 v4 API. Our work is primarily concerned with investigating the trade-offs involved in making the Pistachio kernel completely physically addressed. Recognising and understanding these trade-offs naturally requires an understanding of the current implementation of Pistachio. In this section we highlight a few implementational design choices in Pistachio that prove highly relevant to the remainder of this thesis. An exposition of the current state of addressing in Pistachio is, however, deferred until Chapter 3 where we give it a particularly thorough treatment.

#### **Kernel stacks**

A currently-executing user thread may be pre-empted at any time by an interrupt or exception. At this point the microprocessor traps into system code with an elevated privilege called kernel mode. Synchronous events such as system-call invocations may also trap into system code.

For the kernel to execute, it must have its own local stack. In theory only a single kernel stack (per processor) is needed, but for simplicity the Pistachio implementation uses per-thread kernel stacks. Per-thread kernel stacks simplify handling blocking system calls as all the state required to resume a thread's execution is implicitly contained on its own kernel stack. The drawbacks over single kernel stack implementations include increased cache footprint and resource usage.

Figure 2.5: Per-thread kernel stacks in L4 reside in each thread's TCB.