## THE UNIVERSITY OF NEW SOUTH WALES SCHOOL OF COMPUTER SCIENCE AND ENGINEERING

## Optimising L4 on Blackfin 533/537:

an investigation into a high performance L4 microkernel without virtual memory

Clarence Dang (3101378)

Bachelor of Software Engineering Program

Submission Date: 2006-10-31

Supervisor: Kevin Elphinstone Assessor: Gernot Heiser

## **Abstract**

The L4 microkernel is used as the basis for several operating systems but was built on the assumption of virtual memory. This thesis examines general design issues for constructing a high performance port of L4 without virtual memory but with memory protection. It also aims to provide a concrete implementation by porting L4 to the Blackfin processor.

The results of our research were found to be general, and not just Blackfin-specific. Therefore, we enable L4 to support an additional category of processors – those without virtual memory.

Our L4 implementation on Blackfin verifies the validity of the design. While it outperforms ucLinux, at least on context switching time, there is still much work to be done before it is deployable.

## **Acknowledgements**

Kevin Elphinstone supervised this thesis and the thesis prior to this one. Stefan Petters and Gernot Heiser also supported me during the difficult task of changing to this thesis.

Gernot Heiser gave me the summer project of which this project is based upon. He sparked my interest in kernel hacking.

Alex Webster, Ben Leslie, Matthew Warton and Carl van Schaik, helped answer my torrent of questions about L4 kernel implementation.

Aiden Williams lent me two STAMP boards and his expertise.

## **Table of Contents**

| 1 Introduction                               | 11 |

|----------------------------------------------|----|

| 1.1 Goals                                    | 12 |

| 1.2 Report Structure                         |    |

| 2 The Blackfin Architecture                  | 15 |

| 2.1 Basic Operations.                        | 17 |

| 2.1.1 How they were measured                 |    |

| 2.1.2 Analysis of costs                      |    |

| 2.2 Interrupts, Exceptions and Traps         |    |

| 2.3 Memory                                   |    |

| 2.3.1 Memory layout                          |    |

| 2.3.2 Memory caching                         |    |

| 2.3.3 Memory protection                      | 28 |

| 2.3.4 Conclusions about memory and Blackfin  |    |

| 2.4 Instruction Pipeline                     |    |

| 2.4.1 Pipelining                             | 31 |

| 2.4.2 Blackfin                               | 31 |

| 2.4.3 Conclusions on instruction pipelining. | 32 |

| 2.5 Possible Blackfin Security Bug.          |    |

| 2.5.1 Zero overhead loops                    |    |

| 2.5.2 Exploit code                           | 34 |

| 2.5.3 Analysis of exploit code               |    |

| 2.5.4 Blackfin bug conclusions               |    |

| 2.6 Comparison to ARM                        |    |

| 2.6.1 ARM1156T2-S                            |    |

| 2.6.2 ARM7TDMI                               |    |

| 2.6.3 ARM comparison conclusion              |    |

| 2.7 Blackfin Architecture Summary            | 39 |

| 3 L4 Background                              | 40 |

| 3.1 The Microkernel Approach                 | 41 |

| 3.1.1 Abstractions                           |    |

| 3.1.2 The microkernel advantage              | 42 |

| 3.2 Versions of L4                           | 43 |

| 3.2.1 NICTA L4-embedded                      | 43 |

| 3.2.2 Ports                                  |    |

| 3.3 Recent Developments                      |    |

| 3.3.1 N2                                     |    |

| 3.3.2 Single Stack Kernel                    | 44 |

| 3.3.3 Physical TCB Arrays                    |    |

| 3.4 Summary                                  | 46 |

| 4 An Initial Blackfin Port                   | 47 |

| 4.1 Pingpong Microbenchmark                  | 48 |

| 4.2 Kernel Entry and Exit                    |    |

| 4.2.1 Cache performance of the whole path    |    |

| 4.2.2 Trapframe cost                                  | 51  |

|-------------------------------------------------------|-----|

| 4.2.3 Performance of the C++                          | 52  |

| 4.2.4 Conclusions about the kernel entry and exit     |     |

| 4.3 System Calls                                      |     |

| 4.3.1 System call mechanism.                          |     |

| 4.3.2 System call convention.                         |     |

| 4.3.3 Nested exceptions.                              |     |

| 4.3.4 System call summary                             |     |

| 4.4 IPC                                               |     |

| 4.4.1 Before the thread switch                        |     |

| 4.4.2 After the thread switch (for Inter-AS IPC only) |     |

| 4.4.3 Analysis.                                       |     |

| 4.4.4 Ways to speed up IPC                            |     |

| 4.5 Memory                                            |     |

| 4.5.1 No instruction protection.                      |     |

| 4.5.2 Data protection.                                |     |

| 4.5.3 CPLB replacement policy                         |     |

| 4.5.4 Page table                                      |     |

| 4.5.5 Initial memory layout                           |     |

| 4.5.6 New memory layout                               |     |

| 4.5.7 Conclusions about memory issues                 |     |

| 4.6 Thread ID Space                                   |     |

| 4.7 UTCBs                                             |     |

| 4.8 Conclusion                                        | 73  |

| 5 D                                                   | 7.4 |

| 5 Design Assumptions                                  |     |

| 5.1 No Kernel Preemption                              |     |

| 5.1.1 Costs                                           |     |

| 5.1.2 Idle Loop.                                      |     |

| 5.2 N-series API                                      |     |

| 5.2.1 Security                                        |     |

| 5.2.2 Memory Mapped Registers                         |     |

| 5.2.3 DMA                                             |     |

| 5.3 Conclusion                                        | 79  |

|                                                       | 0.0 |

| 6 Physical Memory Implications                        |     |

| 6.1 Userspace changes.                                |     |

| 6.1.1 Program Loading                                 |     |

| 6.1.2 Physical memory space                           |     |

| 6.1.3 Swapping.                                       |     |

| 6.2 Kernel changes                                    |     |

| 6.2.1 Mappings.                                       |     |

| 6.2.2 Kernel Interface Page                           |     |

| 6.2.3 TCB Array                                       |     |

| 6.2.4 UTCB Area.                                      |     |

| 6.2.5 Message Registers in the UTCB                   |     |

| 6.3 Conclusion.                                       | 85  |

|                                                       |     |

| 7 Protected Kernel Addressing                         | 86  |

| 7.1 Advantages and Disadvantages                      | 87  |

| 7.2 Nested Excentions                                 | 88  |

| 7.2.1 Blackfin system calls                      | 88                 |

|--------------------------------------------------|--------------------|

| 7.2.2 Avoiding nested exceptions                 |                    |

| 7.2.3 Conclusion about nested exceptions         |                    |

| 7.3 UTCB Area                                    |                    |

| 7.3.1 Option A: Reserve UTCB Areas in userspace  | 91                 |

| 7.3.2 Option B: Never reserve UTCB Areas         | 91                 |

| 7.3.3 Option C: Create UTCBs on demand in kspace | 92                 |

| 7.3.4 Choosing a solution                        | 94                 |

| 7.3.5 Conclusions on the UTCB Area               | 96                 |

| 7.4 Conclusion                                   | 98                 |

| 8 Saving Memory on UTCBs                         | 99                 |

| 8.1 Smaller UTCBs                                |                    |

| 8.1.1 Sacrificing message registers.             |                    |

| 8.1.2 Pathological worst case.                   |                    |

| 8.1.3 Conclusions on smaller UTCBs.              |                    |

| 8.2 UTCB Deletion Trade-offs                     |                    |

| 8.2.1 Saving cycles v.s. saving memory           |                    |

| 8.2.2 Deleting immediately may waste memory!     |                    |

| 8.2.3 Conclusions on UTCB deletion.              | 102                |

| 8.3 Conclusion.                                  |                    |

| O Swatowa Calla                                  | 105                |

| 9 System Calls                                   |                    |

| 9.1 Preserving Part of the Trapframe.            |                    |

| 9.1.1 Performance improvement                    |                    |

| 9.1.2 Security concerns                          |                    |

| 9.1.3 Trap code implications                     |                    |

| 9.1.4 Trapframe preservation conclusions         |                    |

| 9.2 Registers to be Preserved.                   |                    |

| 9.3 Registers for Args / Return Values.          |                    |

| 9.3.1 Likely userspace language                  |                    |

| 9.3.3 Summary                                    |                    |

| 9.4 Conclusion.                                  |                    |

|                                                  |                    |

| 10 The Single Stack Kernel                       |                    |

| 10.1 Conversion procedures                       |                    |

| 10.1.1 Changes to switching.                     |                    |

| 10.1.2 Changes to trapping.                      |                    |

| 10.1.3 Summary of conversion procedures          |                    |

|                                                  |                    |

| 10.2.1 Boot stack                                |                    |

| 10.2.2 TCB size                                  |                    |

| 10.2.4 Performance                               |                    |

|                                                  |                    |

| 10.2.5 Implementation summary                    | 122<br>12 <i>A</i> |

| 10.5 Conclusion.                                 | 124                |

| 11 Physically Addressed TCBs                     |                    |

| 11.1 Address to TCR Conversion                   | 126                |

| 11.2 TCB Allocation.                                       | 127        |

|------------------------------------------------------------|------------|

| 11.2.1 Virtual TCB array                                   | 127        |

| 11.2.2 Physical TCB array                                  |            |

| 11.2.3 Physical TCB pointer array                          |            |

| 11.3 Conclusion.                                           |            |

| 10 70 0                                                    | 4.00       |

| 12 IPC                                                     |            |

| 12.1 User Context.                                         |            |

| 12.2 Register-Backed Message Registers                     |            |

| 12.2.1 In theory                                           |            |

| 12.2.2 In practice – the need for an IDL compiler          |            |

| 12.2.3 Attempts on Blackfin                                |            |

| 12.3 Conclusion.                                           | 136        |

| 13 Micro-optimisations                                     | 137        |

| 13.1 Assertions                                            |            |

| 13.2 Volatile Operations.                                  |            |

| 13.2.1 SSYNC pipeline flush                                |            |

| 13.2.2 Register reads.                                     |            |

| 13.3 Inlining Functions.                                   |            |

| 13.4 Avoid Jumps.                                          |            |

| 13.4.1 Do not allow special cases.                         |            |

| 13.4.2 Do not provide optional return arguments            |            |

| 13.4.3 Do not generalise.                                  |            |

| 13.4.4 Use sensible data structure invariants.             | 147        |

| 13.4.5 Use branch prediction.                              |            |

| 13.5 Simplicity                                            |            |

| 13.6 In Loops, Use Pointer Arithmetic - Not Array Indexing | 148        |

| 13.7 Avoid Software-Based Primitives                       |            |

| 13.8 Conclusion.                                           | 151        |

| 14 CPLB Optimisations                                      | 152        |

| 14.1 Switching Address Spaces                              |            |

| 14.1.1 Methods                                             |            |

| 14.1.2 Performance results                                 |            |

| 14.1.3 Performance analysis.                               |            |

| 14.1.4 Experimental findings                               |            |

| 14.1.5 Restoring CPLBs creates problems                    |            |

| 14.12 Restoring CPLBs Without Caching                      |            |

| 14.2.1 Methods                                             |            |

| 14.2.2 Performance results                                 |            |

| 14.2.3 Performance analysis.                               |            |

| 14.2.4 Experimental findings                               |            |

| 14.3 Conclusion.                                           |            |

| 15 Karnal Davalanment Strategies                           | 1/7        |

| 15 1 Pool Hordware                                         |            |

| 15.1 Real Hardware                                         |            |

| 15.2 Debugging Without Visible Output.                     |            |

| 15.3 Debug-Driven Development.                             | 169<br>170 |

| 16 Flaws with L4                           | 171 |

|--------------------------------------------|-----|

| 16.1 Fixed Kernel Memory Heap              | 172 |

| 16.2 Ways to Exhaust Kernel Memory         |     |

| 16.2.1 Creating threads and address spaces |     |

| 16.2.2 Touching memory                     |     |

| 16.2.3 TCB allocation.                     |     |

| 16.2.4 Dummy TCB mappings                  | 173 |

| 16.3 Conclusions.                          |     |

| 17 Global Evaluation                       | 176 |

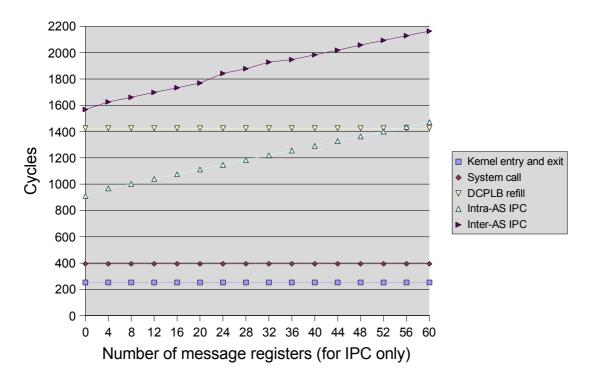

| 17.1 Performance Improvement.              | 177 |

| 17.2 Final Kernel Port Performance         |     |

| 17.2.1 Kernel entry and exit               | 179 |

| 17.2.2 System call                         |     |

| 17.2.3 DCPLB Refill                        | 181 |

| 17.2.4 Intra-AS IPC                        | 181 |

| 17.2.5 Inter-AS IPC                        | 182 |

| 17.2.6 IPC message register copying costs  | 182 |

| 17.3 Conclusion.                           | 183 |

| 18 Conclusion                              | 184 |

| 18.1 Achievements                          | 185 |

| 18.2 Future Work                           |     |

| 18.2.1 ARM ports                           |     |

| 18.2.2 Tweaking the Blackfin kernel        |     |

| 18.2.3 After tweaking the Blackfin kernel  |     |

## **Illustration Index**

| Illustration 1: Final L4/Blackfin kernel's performance | Illustration 1: Final L4/Blackfin kernel's performance | 179 |

|--------------------------------------------------------|--------------------------------------------------------|-----|

|--------------------------------------------------------|--------------------------------------------------------|-----|

## **Index of Tables**

| Table 1: Speed of basic Blackfin operations                             | 17  |

|-------------------------------------------------------------------------|-----|

| Table 2: Blackfin memory layout.                                        | 21  |

| Table 3: Blackfin D-cache miss cycles                                   | 25  |

| Table 4: Performance of the initial L4/Blackfin port                    | 49  |

| Table 5: Cache performance of the initial L4/Blackfin port              | 50  |

| Table 6: Locked DCPLB entries in the initial L4/Blackfin port           | 61  |

| Table 7: UTCB Area design alternatives                                  | 94  |

| Table 8: L4/Blackfin UTCB components                                    | 100 |

| Table 9: L4/Blackfin TCB fields                                         | 117 |

| Table 10: Performance benefits of inlining functions                    | 143 |

| Table 11: Blackfin jump and branch prediction costs                     | 144 |

| Table 12: Address space switching strategies                            | 154 |

| Table 13: CPLB misses after an address space switch (and flushed CPLBs) | 155 |

| Table 14: Methods for restoring CPLB entries                            | 163 |

| Table 15: L4/Blackfin benchmarks (initial and final kernels)            | 177 |

| Table 16: DCPLB refill cost breakdown                                   | 181 |

| Table 17: Intra-AS IPC cost breakdown                                   | 181 |

## Chapter 1

## 1 Introduction

The L4 microkernel [Lie96] is used as the basis for several operating systems but currently only supports processors with virtual memory.

The main advantages of virtual memory is that it provides application isolation and demand paging. However, the use of virtual caches, for performance reasons, creates extra complexity such as synonyms and homonyms.

Virtual memory is a two-edged sword – without virtual memory, these complexities are gone but others take their place. L4 was built on the assumption of virtual memory so the suitability of its primitives must be re-evaluated. We therefore examine the issues in supporting L4 on architectures with memory protection units (MPU).

The Blackfin [Ana05] is a popular embedded processor and a specific instance of an MPU architecture so we examine the problems in its context.

The remainder of this chapter defines the goals of this thesis and then presents the structure of the rest of this report.

## 1.1 Goals

This thesis will identify the microkernel construction issues that arise out of supporting L4 on MPU-based processors, specifically Blackfin. The findings will be generalised to other architectures without virtual memory, such as the ARM1156T2-S MPU-based processor, and even to architectures without memory protection, such as the ARM7TDMI.

We shall construct a port of L4 to Blackfin whose performance will compare favourably to ucLinux, whose minimum context switch time is approximately 2,485 cycles [Hen06]. We will even attempt to match the speed of other L4 ports to RISC architectures, whose context switches complete in the low hundreds of cycles.

In doing so, we will identify a number of Blackfin-specific optimisations as well as general techniques for constructing high performance kernels.

Finally, our work will mean that Blackfin will become the 4<sup>th</sup> mature, public port of NICTA L4-embedded after ARM, x86 and MIPS64. This will strengthen the applicability and competitiveness of L4 in a wider part of the embedded market.

## 1.2 Report Structure

This section describes the structure of the remainder of the thesis.

Our thesis begins by providing the necessary background for our work:

- Chapter 2 analyses the features and performance of the Blackfin processor. It also compares Blackfin to the variants of ARM without virtual memory, to provide a more general feel for the thesis.

- Chapter 3 discusses the benefits of a microkernel approach to operating system construction, the L4 microkernel and recent, relevant L4 developments.

- Chapter 4 reflects on a "quick and dirty" implementation of the kernel on Blackfin that ignored design. The subsequent chapters in the thesis are primarily devoted to addressing the design and performance issues identified here.

We then provide 5 chapters on design:

- Chapter 5 identifies the assumptions in the design of our kernel.

- Chapter 6 discusses the effects of a lack of virtual memory.

- Chapter 7 analyses the implications of *protected kernel addressing*, a feature of some processors.

- Chapter 8 considers ways of reducing the amount of memory used by UTCBs, a particular kernel data structure.

- Chapter 9 explores choices in the system call ABI.

Our thesis then implements and critiques some related work:

- Chapter 10 describes the implementation of Warton's single stack kernel [War05].

- Chapter 11 investigates the implementation of Nourai's physically addressed thread control blocks [Nou05].

We then shift our focus largely onto general implementation issues:

- Chapter 12 describes a small number of issues regarding IPC. Other IPC performance bottlenecks are also dealt during the coverage of more general issues in Chapters 7, 13 and 14

- Chapter 13 presents micro-optimisations that dramatically improve kernel performance.

- Chapter 14 runs experiments that aim to improve the kernel's performance, through changing the way it manipulates the Blackfin's protection unit and considers address space switching in this context.

Finally we reflect on, and evaluate, the work we have done:

- Chapter 15 describes some peripheral observations we made the implementation of this thesis

- Chapter 16 presents problems with the L4 microkernel, that we met along the way.

- Chapter 17 evaluates the entire thesis.

- Chapter 18 reflects on what goals have been achieved and what remains to be done.

## Chapter 2

# 2 The Blackfin Architecture

The chapter describes the characteristics and performance of the Blackfin architecture, providing a qualitative and quantitative foundation on which we will be able to make informed decisions regarding kernel design trade-offs. We perform measurement experiments and analyse aspects of the architecture. Relevant parts of the Blackfin reference manuals [Ana05, Ana05c, Ana05b] are also summarised to provide the minimal background required to understand this thesis. We begin by providing some light Blackfin and architecture background before moving on to describe the structure of the rest of this chapter.

The Blackfin is an embedded DSP processor from Analog Devices [Ana05]. It is a 32-bit RISC processor whose striking feature is that it has no virtual memory but it does have a memory protection unit. We shall concentrate on the Blackfin 533 and 537 due to gcc toolchain support [Bla05] and because they have identical cores. ucLinux [Bla06d] runs on this processor and is a key competitor to L4-based operating systems.

During the last decade, CPU frequency has slipped away from being the primary determinant of system performance. Other aspects such as caching, TLB coverage and pipelining have become equally, if not more, important. As a result, these issues must be analysed in some depth.

We now describe the structure of the remaining parts of this chapter:

- 1. The section *Basic Operations* will measure the cost of key, basic Blackfin instructions.

- 2. *Interrupts, Exceptions and Traps* will describe aspects of entering and exiting the kernel.

- 3. It is followed by the *Memory* section with extended discussions on caching and protection mechanisms, as well as performance implications.

- 4. Instruction Pipeline will examine instruction pipelining on the Blackfin.

- 5. The *Possible Blackfin Security Bug* section deals with a potential exploit due to a instruction set design flaw.

- 6. Finally, we look at the similarities between Blackfin and other virtual-memory-less architectures in the *Comparison to ARM* section, in order to make our findings more general.

## 2.1 Basic Operations

So that proper architecture trade-offs could be determined, the cost of basic operations were measured:

| Operation                           | With D-cache & I-cache |                | Uncached |

|-------------------------------------|------------------------|----------------|----------|

|                                     | Cycles                 | Initial cycles | Cycles   |

| NOP                                 | 1                      | 7              | 13       |

| Register copy                       | 1                      | 7              | 13       |

| Register addition                   | 1                      | 7              | 13       |

| Read word from RAM <sup>1</sup>     | 1                      | 8              | 49       |

| Write word to RAM                   | 1                      | 8              | 28       |

| Read from Core MMR <sup>2</sup>     | 4                      | 7              | 13       |

| Write to Core MMR                   | 4                      | 7              | 13       |

| Call to empty function <sup>3</sup> | 18                     | 21             | 417      |

| CSYNC <sup>4</sup>                  | 10                     | 10             | 71       |

| SSYNC <sup>5</sup>                  | 16                     | 23             | 86       |

Table 1: Speed of basic Blackfin operations

We firstly discuss how these results were measured and then provide an analysis of these costs. The speed of branches is considered in another section [p144, Chapter 13.4].

<sup>1</sup> RAM = main memory (SDRAM) write-back cached by L1.

Core MMR = uncached Memory Mapped Register storing CPU state. The innocuous DTEST\_DATA0 (0xffe0 0400) was used for both tests. It is believed that reads and writes to this register do not have side-effects that could cause extra computation. Other registers (e.g. for changing memory protection) were expected to cause actual computation.

The function was:

<sup>00</sup> e8 00 00 LINK 0x0; // Create stack frame 01 e8 00 00 UNLINK; // Tear down stack frame 10 00 RTS; // Return to caller

<sup>4</sup> CSYNC = pipeline flush and CPU buffer synchronisation with L1.

<sup>5</sup> SSYNC = CSYNC followed by synchronisation of L1 with the rest of the system.

## 2.1.1 How they were measured

The statistics were measured by executing the operations in question 256 times:

```

// Flush pipeline & CPU buffers, sync L1, sync with SDRAM

ssync;

// Guarantee pipeline flush (pipeline is only 10 long)

nop; [256 times]

.align 32: // Align on cache boundaries

r0 = cycles; // Read 64-bit cycle counter

r1 = cycles2;

// All instructions are at least 2 bytes.

// Therefore, at least 256 * 2 / 32 = 16 I-cache lines will be

allocated.

<the operation in question>; [256 times]

// Unfortunately, this will cause another I-cache line to be

// allocated. This is not a big problem as the above operation

// causes 16x more allocations and the total cycle count will be

// divided by 256 anyway.

r4 = cycles; // Read 64-bit cycle counter

r5 = cycles2;

nop; [256 times] // Ensure no pipeline speculation warping results

```

50 runs of this were executed.

For the values for caching off, *Cycles* is the average of the cycles counts of all 50 runs, divided by 256. The standard deviation of the 50 runs divided by 256 (the number of times the operation was repeated) was 0, rounded to the nearest integer, in all cases.

For the values with caching on, *Initial Cycles* represents cycle count of the first run, with a cold D-cache and I-cache, divided by 256. *Cycles* is the average of the cycle counts of the last 49 runs divided by 256 on a warm D-cache and I-cache. The standard deviation of the last 49 runs was always 0, rounded to the nearest integer.

## 2.1.2 Analysis of costs

In this section, we discuss the measured instruction costs.

Under normal circumstances, the processor is capable of executing 1 basic computation per cycle. Note that access to L1 – or equivalently, cached main memory – is just as fast as register access!

However, memory mapped registers (MMRs) require 4 cycles to access even though they are in L1 memory, albeit in a different section. Firstly, this may be because interrogating and manipulating CPU state cannot come completely for free or that testing. Secondly, by running

the accesses back-to-back, we have introduced pipeline dependencies. In further testing, where we placed 16 NOPs (enough to flush the pipeline) between MMR writes, we found that the cost of MMR writes drops to 3 cycles, on average. However, given that we do tend to place MMR writes very close to each other, we quote the figure with pipeline dependencies – 4 cycles – in the table.

The function call exposes the cost of flushing the pipeline on both the call and return unconditional jumps. The cost of CSYNC pipeline flush is 10 which is surprisingly fairly cheap and equal to the length of the (short) pipeline. However, the values for both CSYNC and SSYNC are expected to be larger in real code due to extra required buffer synchronisation. The initial CSYNC cycle cost is the same as the cycle cost on a warm I-cache — this is an anomaly with the data that should be investigated.

The initial L4/Blackfin port was uncached so for completeness, the uncached values have been provided. The CPU store buffer can be seen to absorb the cost of 256 writes to the same RAM address but there is no similar "load buffer" for the more expensive reads. The uncached performance is dominated by instruction loads from SDRAM as can be seen from 2 benchmarks:

- 1. Call to empty function: The repeated function calls cause constant pipeline flushes, on both the jump into the functions and the returns, resulting in a high rate of instruction refetch.

- 2. CSYNC/SSYNC: We see the cost of refilling the pipeline, from SDRAM, for each of the 256 CSYNC/SYNC instructions (normally, 64-bits of instructions can be read in at a time but every instruction is a pipeline flush).

In summary, we ran experiments to measure the speed of basic operations on the Blackfin. The Blackfin, with no cache misses, can execute a basic instruction or memory access in a single cycle. Memory Mapped Registers can be accessed in 4 cycles. Function calls are very expensive, at 18 cycles. Finally, flushing the pipeline takes at least 10 cycles.

## 2.2 Interrupts, Exceptions and Traps

In this section, we describe the program sequencing in the context of entering and exiting the kernel. There are 16 interrupt/exception levels. The important ones are:

- 1. General-purpose, asynchronous hardware interrupts 7-15: These are generated by hardware or synthesised by the kernel mode RAISE instruction.

- 2. Synchronous exceptions "posing" as interrupt level 3: These are caused by events such as accesses to unmapped memory and illegal instructions. System call exceptions can be invoked by using the user and kernel mode EXCPT instruction.

Low priority interrupts (high numbered ones) can be preempted by equal or higher priority ones (low numbered).

However, exceptions are not allowed to occur when servicing an exception and cause the processor to event a *double fault* state. To bypass this problem, one simply needs to switch the processor to an interrupt mode on the initial exception, as exceptions are permitted during interrupts.

Interrupts are automatically disabled on kernel entry. Interrupts in kernel mode can be reenabled by exploiting a bizarre instruction side effect — pushing the register containing the address of the user instruction (RETI) onto the kernel stack. So if one wishes to save RETI without re-enabling interrupts in kernel mode, one must copy it to another register first:

```

R0 = RETI;

[--SP] = R0;

```

Interrupts can be masked using the IMASK memory-mapped register. If userspace is, for some reason, given access permissions to the IMASK register, it can also mask interrupts. Regardless of processor mode, exceptions cannot be masked.

Trapping can be done without reserving userspace registers for the kernel (like MIPS32's k0 and k1). This is because there are separate userspace and kernel space stack and instruction pointers.

A readonly memory-mapped IPEND register contains bits set for each interrupt level currently being serviced in order to keep track of nested interrupts/exceptions. Usermode is defined as the state of the CPU when it is not serving any interrupts. But since IPEND cannot be directly written to, it is difficult to return to usermode when serving nested interrupts. This is in contrast to the writeable *CPU status register*, found on other chips, which normally contains a single bit stating whether the chip is currently in kernel mode.

In summary, the Blackfin supports nested interrupts and different interrupt priorities but it is difficult to return from usermode in the presence of nesting. Exceptions cannot be nested so if we wish to allow exceptions while serving a first exception, we must switch to an interrupt mode on the initial exception.

## 2.3 Memory

We will now analyse the all the memory aspects of the Blackfin – layout, caching and protection.

It is important to emphasise that the Blackfin is a pure physical memory system. Virtual cache issues [Uns05] that plague virtual memory architectures, such as cache synonyms (multiple virtual addresses per physical addresses) and homonyms (a virtual address referring to different physical addresses depending on the current address space) are therefore non existent.

## 2.3.1 Memory layout

The Blackfin has a flat 4GB 32-bit address space and supports a maximum of 128MB of conventional, SDRAM [Bla06, Ana05b]:

| 0 - up to 128MB         | conventional memory                                                                      |

|-------------------------|------------------------------------------------------------------------------------------|

| 128MB - 0xffc00000      | memory mapped registers (MMRs) for devices(there are many reserved holes in this region) |

| 0xffc00000 - 0xffe00000 | CPU's system MMRs                                                                        |

| 0xffe00000 - 4GB        | CPU's core MMRs                                                                          |

Table 2: Blackfin memory layout

The system MMRs access "on-chip peripherals outside of the core" [Ana05 p1-6] and run at the system clock frequency (99MHz on the STAMP board). Conventional memory is therefore capped as this speed but this overhead is absorbed by cache.

The core MMRs run at the CPU clock frequency (497MHz on the STAMP board).

## 2.3.2 Memory caching

In this section, we provide a general, architecture-neutral motivation for caching and then discuss it in terms of the Blackfin.

### **Motivation for caching**

The speed of main memory has not improved as quickly as the speed of CPUs. As a result, the CPU may stall waiting for memory to be copied to and from registers, when it could be serving literally hundreds of instructions. One way to reduce the impact of this is to have a small but very fast amount of memory *cache* near the CPU. The hope is that because of locality, most accesses can be served directly by the cache (a *cache hit*) instead of needing to access slow main memory (a *cache miss*). As a result, cache hits have a dramatic beneficial effect on system performance. To amortise memory access costs, on a cache miss, the cache copies to

and from memory the size of a cache line ("typically 16-32 bytes" [Uns05]).

An associative cache is split into a number of sets of cache lines. The bits in a memory address are viewed as and split into the following (the number of bits for each varies from cache to cache) [Uns05]:

- 1. Tag (most significant bits)

- 2. Set number

- 3. Byte within the cache line's data (least significant bits)

The *set number* determines which cache set a particular memory address is in. The hardware performs a parallel (also known as associative) lookup of all lines in the set and determines whether the memory address is in the cache by matching the *tag* bits of the address. A *way* consists of all of the same numbered lines from each set i.e. it cuts across all sets.

Higher associativity – more cache lines per set – results in complex and expensive hardware due to the parallel lookup. However, this leads to fewer cache conflicts because different memory addresses with the same set number have a number of lines to choose from. One extreme is a *fully associative* cache, where there is only one set. The other extreme is *direct mapped* where each set contains only one line.

From a programmer's point of view, in order to minimise the number of cache misses:

- 1. Minimise the size of code and data so that our working set is more likely to fit into the high-speed cache.

- 2. Do not unnecessarily cross an alignment boundary. For instance, if the cache lines are 32 bytes each and an 8 byte variable is stored at the address n \* 32 + 28 (for arbitrary n), accessing this variable would result in 2 cache misses a line for n \* 32 and the line for (n + 1) \* 32 as the variable is split between 2 cache lines.

In summary, caching uses the principle of locality to hide the latency of memory. Given the size of the memory-CPU speed gap, caching is essential for system performance. However, this only works if we optimise our code and data for size so that the working set fits into cache.

## Blackfin's caching

We now consider different aspects of the Blackfin's caching features, building on top of the caching background we just provided. The topics that will be covered include L1 memory, data and instruction caches, store buffer, cache coherency and the cost of cache misses.

#### L1 memory

L1 memory runs "at the full processor speed with little or no latency" [Ana05 p1-4] so is approximately 5 times (497 / 99) faster than the main SDRAM memory.

The Blackfin 53x series of chips contain [Bla06, Ana05c]:

- 16 KB of instruction SRAM/Cache

- 16 − 32 KB of data SRAM/Cache (32 KB for the 533)

- 16 64 KB of instruction SRAM (64 KB for the 533)

- 0-32 KB of data SRAM (32 KB for the 533)

- 4 KB of scratchpad data SRAM

*SRAM/Cache* means that part or all of the respective memory block can be configured as cache – we have highlighted these in **bold**. A cache is bypassed if it is disabled or if a newly fetched line is not deemed "important" enough (see our *Instruction Cache* discussion below) to replace an existing line [Ana05 p6-16].

All other SRAM can potentially be used for locking in kernel code and data without polluting the caches. Instruction SRAM can only be filled using DMA ([Ana05c p307]) which means code that is to be placed there must be specially linked to the right address or be relocatable.

The Blackfin 53x's have no L2 memory [Bla06].

#### Instruction cache

This is a 16KB 4-way associative cache with each line containing 32 bytes of data. Tags and line attributes are stored separately from each line.

The processor keeps track of 2-bits per line for an LRU replacement policy. The operating system can state an LRU "importance" bit in each cache line's tag so that "unimportant" lines cannot evict "important" ones.

On an instruction cache miss, the CPU begins reading 32 bytes (the size of a cache line) from the line fill buffer, which consists of four 64-bit entries [Ana05 p6-15]. The line fill buffer will read from external memory. The CPU restarts as soon as the line buffer returns a word as "the line fill buffer allows the core to access the data from the new cache line ... [before] the line has been written".

It is possible to flush and modify lines of the cache.

#### Data cache

The data cache is 32KB 2-way associative cache with each line containing 32 bytes of data. Again, tags and line attributes are stored separately from each line.

Data cache lines can be configured to either "write-through" or "write-back" and the line replacement policy is determined by the Cache Controller [Ana05 p6-29].

A line fill buffer similar to the instruction cache's one exists. An SSYNC instruction is required to flush the write buffer [Ana05 p6-35].

It is possible to prefetch, flush and invalidate lines.

#### Store buffer

A 6 \* 32-bit store buffer sits between L1 and the CPU core [Ana05 p6-28]. The CPU can read two 32-bit words simultaneously from the store buffer and or write 32-bits.

#### **Cache coherency**

Modifying cached instructions requires invalidating the respective cache lines to guarantee cache coherence [Ana05 p6-16].

Similarly, the data cache lines must be invalidated before a DMA operation [Ana05 p17-2].

#### **Cache misses**

Consistent values for I-cache and D-cache misses and refills could not be obtained. The value appears ranges from 47-226 but seems to hover around 113-134 cycles. This section describes some our experiments in attempting to measure cache miss costs and attempts to justify the measurement variability.

#### **D-Cache refill cost**

We attempted to measure D-cache costs by flushing the D-cache and then using this code (different to the previous test [p17, Chapter 2.12.1]):

```

// Flush pipeline & CPU buffers, sync L1, sync with SDRAM

ssync;

// Guarantee pipeline flush (pipeline is only 10 long)

nop; [256 times]

.align 32: // Align on cache boundaries

r0 = cycles; // Read 64-bit cycle counter

r1 = cycles2;

p1.h = <arbitrary_cplb_mapped_address>;

p1.l = <arbitrary_cplb_mapped_address>;

r6 = [p1];

r4 = cycles; // Read 64-bit cycle counter

r5 = cycles2;

nop; [256 times] // Ensure no pipeline speculation warping results

```

The code was run with and without the statement that caused a D-cache line pull r6 = [p1] (D-cache line pull) and we concluded that the cycle difference of 66 was the cost of a D-cache miss. Adding the r6 = [p1] could not have caused an extra I-cache line pull as the total instruction size between the cycle counter reads inclusive is 14 bytes including it.

#### I-Cache refill cost

Similarly, I-cache misses were measured at approximately 113.5 per line by adding and removing the italicised nop; [256 times] below. This was based on the claim that there would be an addition or removal of 256 \* sizeof(NOP) / 32 = 16 lines (ignoring the comparatively insignificant cost of executing the NOPs themselves):

```

// Flush pipeline & CPU buffers, sync L1, sync with SDRAM

ssync;

// Guarantee pipeline flush (pipeline is only 10 long)

nop; [256 times]

.align 32: // Align on cache boundaries

r0 = cycles; // Read 64-bit cycle counter

r1 = cycles2;

// Each NOP instruction is 2 bytes

nop; [256 times]

r4 = cycles; // Read 64-bit cycle counter

r5 = cycles2;

nop; [256 times] // Ensure no pipeline speculation warping results

```

However, we found that of values of 66 cycles for a D-cache miss and 113.5 cycles for an I-cache miss were not consistent, as described in the following section.

#### Inconsistent results

At other times, D-cache has been measured to be slower than we initial measured (e.g. 134 cycles instead of 66) and I-cache faster (e.g. 60 cycles instead of 113.5). For instance, we ran 3 tests, with different chip configurations, that flushed the D-cache and touched the first 32-bit word of every 32 aligned bytes of 32KB (the size of the D-cache). It resulted in the following cycle counts and suggest that D-cache misses take about 114 cycles (not our previously measured 66):

| Chip Configuration                                                          | Cycles per D-cache Line (32 bytes) |

|-----------------------------------------------------------------------------|------------------------------------|

| 1. D-cache and I-cache enabled                                              | 114                                |

| 2. I-cache only                                                             | 48                                 |

| 3. I-cache only baseline (our D-cache line touches were replaced with NOPs) | 9                                  |

Table 3: Blackfin D-cache miss cycles

This involved 1024 repeated instances of:

```

r2 = [p0]; // Changed to NOP for the 3^{rd} case in the table r4 = p0; r5 = 32; r4 = r4 + r5;

```

$$p0 = r4;$$

The results in the table above are given for the second run so that the I-cache is warm. I-cache conflicts for this code (1024 copies \* 5 instructions = 5KB) are assumed to be small. The cost of executing these instructions is assumed to be much smaller than the D-cache misses.

Because the 1<sup>st</sup> test executed the worst case for caching – causing 32 bytes to be loaded for every 4 bytes read – this 2<sup>nd</sup> test case performs expectedly better when D-cache is *off*.

To double check that the bulk of the costs we are measuring in the 1<sup>st</sup> test can be attributed to D-cache refills, we performed a 3<sup>rd</sup> test which replaced the memory access with a NOP. The 3<sup>rd</sup> test executed in far fewer cycles (9) so we can conclude that the cost of the 1<sup>st</sup> test is largely due to D-cache lines being faulted in, in approximately 114 cycles. But this is almost double the figure of 66 we arrived at previously.

#### Possible reasons for inconsistent cache miss measurements

The inconsistent values that we are getting for D-cache and I-cache line fills are worrying. Evidently, there is something happening inside the CPU that we were not expecting

One possibility is the line fill buffers (between L1 & SDRAM) enabling CPU access to the data before the entire cache line is filled. Because the refill protocol stipulates that the pipeline restarts as soon as the word, to be accessed, is loaded (and the rest of the line is refilled in the background), the matter is made more complicated. There may be following instructions, accessing the same cache line, proceeding in the pipeline while the cache line is being filled. Depending on the offsets of the accesses within the cache line and timing, these following accesses could potentially succeed without stalling the pipeline if the fill buffer is sufficiently filled.

A "back of the envelope" calculation suggests that for D-cache, the cost of copying a line from SDRAM into the *fill buffer* is:

```

497 / 99 * 32 / 4 = approximately 40 CPU cycles where:

497 = CPU frequency

99 = system frequency i.e. SDRAM upper bound

32 = cache line size

```

4 = word size (assuming word size bus transfers [Ana05c]).

An extra 32 / 4 = 8 cycles would then be used to copy from the fill buffer to L1. The total of 40 + 8 = 48 cycles is fairly close to the 60 odd cycles sometimes seen for I-cache and D-cache misses (also given the variability and impact of SDRAM refreshes).

In any case, we can conclude that I-cache and D-cache misses cost at least 60 cycles and sometimes take more than 100.

## **Memory caching conclusions**

System performance is strongly linked to cache footprint. The Blackfin's split L1 instruction and data caches can be accessed as almost quickly as registers, amortised, and assuming no cache misses. We ran experiments but could not determine precise costs for D-cache and I-cache misses but we do know that they are in the order of 100 cycles each.

## 2.3.3 Memory protection

In this section, we will firstly discuss the Translation Lookaside Buffer used for memory protection. Then we will analyse the Blackfin's version of this mechanism.

#### **Translation Lookaside Buffer**

Most CPUs contain a *Memory Management Unit (MMU)* which provides virtual to physical translation and checks memory accesses by looking up permissions from a Page Table stored in main memory. Unfortunately, if the CPU were to access the page table (memory) on every memory access, this would double the number of memory transactions resulting in suboptimal performance. Therefore, CPUs contain a small (e.g. 16 entries) but very fast (fully associative) cache of page table entries [Uns05], called a *Translation Lookaside Buffer (TLB)*.

MMUs are far more common than the *Memory Protection Unit (MPU)* used on architectures without virtual memory. MPUs contain all the protection functionality of MMUs without the translation.

If the memory address of the access to be checked is not in the TLB, a *TLB miss* occurs and the TLB must be filled from the entry in the Page Table corresponding to the address. This is performed by either hardware or the kernel depending on the architecture.

If it is not in the page table, a *page fault* exception is sent to the kernel. The kernel must either insert an entry into the Page Table or if the faulting thread does not have the appropriate permissions to access the faulting address, killing the offending thread.

We will now consider TLB replacement policies and other operating system considerations.

#### **TLB** replacement policies

As with cache lines, in order for a TLB refill to occur, an existing line must be evicted to make room for the new one, unless there are free lines. Ideally, the line that will not be used for the longest should be removed. Three policies are First In First Out (FIFO), Random and Least Recently Used (LRU).

FIFO is fast and simple to implement but fails to exploit locality as occasional accesses to other addresses evicts commonly used pages. Random is almost as fast and simple but also avoids the pathological worst case of cyclical access to a working set slightly larger than the TLB coverage. Random is the most popular method for TLB replacement.

LRU assumes prior behaviour is suggestive of future behaviour i.e. that line used least recently will not be used for the longest period of time. Without an oracle, LRU is as close as practical for optimal exploitation of locality. Unfortunately, tracking which line has been used most recently would require updating state on every memory access resulting in unacceptable performance.

An approximation of LRU is the 2nd chance or Clock eviction policy. Clock maintains a

pointer to a "current" line. Whenever a line needs to be evicted, the clock increments its pointer (wrapping around to the first line), evicts the first line with the *reference bit* clear and finishes. For all lines it encounters along the way, the Clock clears the reference bit. Accesses to lines with zero reference bits results in a fault (TLB readonly exception). The kernel will respond by setting the reference bit of the faulting line. In this way, the reference bit simulates a "least-recently-used" bit. Lines which are in use are less likely to be evicted.

However, each run of the Clock algorithm may mark many pages as readonly. The subsequent protection violations, on writes to these many pages, usually outweighs the benefit of avoiding the refill cost of the accidental eviction of a single page. Simple and fast policies such as Random are much better.

#### Other operating system considerations

The size of memory has been growing rapidly but the TLB, and the memory coverage of the TLB, has not [Uns05]. Therefore, TLB pressure is increasing. In order to reduce the overhead of TLB misses, an operating system should minimise the number of TLB misses by ensuring that each entry covers the largest address range possible (as long as each address in the range shares the same protection attributes). Therefore, the TLB may support a number of page sizes. "Large" page sizes such as 1MB and 4MB are often referred to as *superpages*.

Tagged TLBs contain Address Space IDs (*ASIDs*) in order to avoid leaking protection between address spaces. Untagged TLBs without ASIDs normally require that the operating system flush the TLB on each address space switch. This performance penalty is compounded by the extra cost of serving the TLB misses that occur immediately after the switch.

#### **Blackfin**

As Blackfin does not support virtual memory, it has MPUs instead of TLBs. We now describe the details of its MPUs.

The Data Cacheability Protection Lookaside Buffer (DCPLB) is a 16 entry, untagged and fully associative MPU for data accesses. Each entry controls caching attributes and enforces user read and write access permissions.

The Instruction *Cacheability Protection Lookaside Buffer (ICPLB)* is a similar MPU but for controlling instruction fetches. It operates totally independently of the DCPLB. It is therefore possible to execute instructions (ICPLB) but not be able to read them (DCPLB).

Both are refilled in software by the kernel and therefore, suffer from pipeline and cache pollution. This means that system performance depends more heavily on reducing the number of MPU entry refills, compared to a hardware-refilled MPU.

1KB, 4KB, 1MB and 4MB pages are supported. There are bits for locking a line and marking a page as kernel accessible only. Pages cannot overlap so they can only be shared between userspace and kernel space at the same fine or coarse granularity.

The MPUs are optional and are off by default. If you enable them for memory protection, even kernel accesses must go through the MPUs. MPU pressure is therefore increased and we

discuss further implications of this protected kernel addressing later [p86, Chapter 7].

The MPU must be disabled before changing any MPU entries. This requires an SSYNC to flush the pipeline and propagate the protection disable notification. After changing some MPU entries, one must re-enable protection and SSYNC again. These 2 SSYNCS alone mean that protection changes require at least 2 \* 10 = 20 cycles [p17, Chapter 2.1].

Protection can be turned on without caching. However, caching requires protection. Therefore turning off protection to bypass the MPU for accessing memory in kernel mode should not be done for long periods of time due to the performance hit of no caching.

#### **Summary of memory protection**

The TLB is a hardware cache of the page table, providing virtual to physical translation and protection. TLB misses are either served by the kernel or hardware depending on the architecture. A simple and effective TLB replacement policy is Random. The operating system should attempt to use large superpages for greater TLB coverage and to reduce TLB pressure. Untagged TLBs cannot allow for entries from different protection domains so mandate expensive flushes on address space switches.

The Blackfin has software-refilled, split data and instruction protection units that offer no translation – the DCPLB and ICPLB. Kernel addressing is also subject to the CPLB protection mechanisms. Changing CPLB entries is expensive, as is leaving them off as they control caching as well.

## 2.3.4 Conclusions about memory and Blackfin

The Blackfin does not have virtual memory so has a single 32-bit address space, with many CPU memory-mapped control registers at the top. Accessing cached data in the split instruction and data caches is just as fast as register accesses. The Blackfin has software-refilled and separate data and instruction CPLB protection units.

## 2.4 Instruction Pipeline

In this section we discuss the features of CPU instruction pipelines. We then delve into the details of the Blackfin's pipeline.

## 2.4.1 Pipelining

Modern RISC processors split instruction execution into multiple stages. Therefore, multiple instructions can be "in flight" at different stages of execution, maximising the usage of different CPU units, as long as the instructions are independent.

The pipeline is stalled in the presence of data dependencies i.e. "when an instruction depends on the results of a previous instruction" [CNC00] but that previous instruction has not yet written its output.

Branch hazards can occur because the processor speculatively executes instructions based on a *prediction* of whether a branch will be taken. If this prediction is wrong, the pipeline must be flushed of such instructions and refilled – expensive with a long pipeline. Speculative reads or writes from I/O devices may cause unexpected behaviour.

#### 2.4.2 Blackfin

The processor contains a 10 stage pipeline which stalls automatically in several places so that software does not have to deal with hazards in order to guarantee correctness [Ana05]. Assuming no stalls, the Blackfin can perform at least 1 instruction per cycle [p17, Chapter 2.1].

Write operations write to the store buffer [p24, Chapter 2.3.2] and complete before "the data is actually written to an external memory or I/O location". Reads may be satisfied from the store buffer.

Read instructions, placed after a branch instruction, may be speculatively executed before the branch instruction is committed. This is unexpected for an I/O devices and so the CSYNC instruction must be used before I/O reads to flush the store buffer and to ensure "any pending interrupts, speculative states (such as branch predictions), or exceptions" are completed. The SSYNC instruction performs a CSYNC and then "flushes any write buffers between the L1 memory and the system domain and generates a sync request to the system that requires acknowledgement".

Interrupts can cause I/O accesses to be aborted, possibly after a "memory-read cycle was initiated". In this case the access will occur again after the interrupt, which off-chip devices do not guard against. Therefore, interrupts should be disabled before such accesses.

Static branch prediction is used for conditional branches and we discuss the performance of this, on the Blackfin, in another chapter [p144, Chapter 13.4].

## 2.4.3 Conclusions on instruction pipelining

Modern chips execute multiple instructions simultaneously at different stages of a potentially long *pipeline*. Branches decrease performance because they prevent effective instruction readahead into the pipeline.

On the Blackfin, the pipeline is only 10 stages long and can normally execute 1 instruction per cycle. Speculative execution and work store ordering mean that I/O device accesses must be surrounded by CSYNC/SSYNC barriers and depending on the situation, require interrupts to be disabled.

## 2.5 Possible Blackfin Security Bug

We strongly believe that the Blackfin contains a security hole so this section describes an exploit in detail and also workarounds. The hardware feature that enables this exploit, *zero overhead loops*, will be explained followed by a presentation of the code and an analysis.

## 2.5.1 Zero overhead loops

The Blackfin enables this exploit through its support for zero overhead loops [Ana05]. Normally, one points an LT (Loop Top) register to the start instruction address of a loop. LB (Loop Bottom) will point to the last address in the loop. LC (Loop Count) will be set to the number of iterations of a loop. These registers can only setup loops a short distance away from the setup code.

However, if user loop setup code is placed sufficiently close to the kernel trap or untrap code and executed, a zero overhead loop may be setup in the *kernel* code. The kernel would then loop when trapping in (or out) which would corrupt the kernel stack. Worse still, possible stack overflows (or underflows) would either corrupt other kernel memory and/or cause a in-kernel faults due to unexpected accesses to unmapped memory.

On the following page, we present the code for the exploit that sent to Analog Devices on 2006-03-02. This will be followed by a subsequent analysis of the attack.

## 2.5.2 Exploit code

#### **Userspace**

```

// Point the loop registers to kernel code.

// For whatever reason, the user is aware of the position of the

// kernel untrap code ("untrap_middle" & "untrap-end").

r0.h = untrap_middle; r0.l = untrap_middle; lt0 = r0;

r0.h = untrap_end; r0.l = untrap_end; lb0 = r0;

r0.h = 0x7fff; r0.l = 0xffff; lc0 = r0; // >2*10^9 loop iterations.

// Loop forever waiting for an interrupt to fire.

l:

jump.l l;

```

#### Kernel space

```

untrap_from_interrupt:

usp = [sp++];

fp = [sp++];

[... restoring of more registers ...]

// Loop registers get restore here, forming a loop!

lt0 = [sp++];

1b0 = [sp++];

lc0 = [sp++];

// This label is here just to make it clear as to what userspace is

// pointing to.

untrap middle:

b3 = [sp++];

b2 = [sp++];

b1 = [sp++];

b0 = [sp++];

13 = [sp++];

12 = [sp++];

[... restoring of more registers ...]

a0.w = [sp++];

// This label is here just to make it clear as to what userspace is

// pointing to.

untrap end:

a0.x = [sp++];

// Return to usermode.

rti

```

## 2.5.3 Analysis of exploit code

We firstly describe the sequence of events, arising from the previous exploit code, followed by a discussion on how to defeat the attack.

#### Sequence of events

- 1. Userspace sets up malicious loop registers that point to kernel code.

- 2. Userspace spins in a loop waiting for an interrupt to fire.

- 3. An interrupt fires.

- 4. The kernel saves all registers on the trap in.

- 5. The kernel serves the interrupt.

- 6. The kernel attempts to exit back into usermode via untrap\_from\_interrupt.

- 7. The kernel begins restoring registers.

- 8. As part of 7. it restores the loop registers 1t0, 1b0, 1c0 (just before untrap\_middle). But the user pointed these registers to kernel code (specifically to loop between untrap\_middle and untrap\_end and for more than 2 billion iterations). Therefore a hardware loop is now active in *kernel mode*.

- 9. The kernel continues restoring registers between untrap middle and untrap end.

- 10. But before it reaches the rti instruction, it decides to loop back to untrap\_middle due to the hardware loop. This is repeat 2 billion times until the kernel stack is underflowed.

## Can we defeat this exploit?

While this could be defeated by masking the LBO and LB1 registers, which are stored on stack, to ensure that they only point to userspace, a similar exploit that forms a hardware loop before the kernel *trap* is entered, at first, seems certain to be triggered by helpless kernel entry code. But this too can be defeated by making use of a feature of hardware loops – they can only cause code at most 30 bytes away to loop. Therefore, ensuring that there is enough padding between user code and the kernel trap code is sufficient to ensure the exploit will fail.

Nevertheless, we had significant difficulty in getting either exploit to work. Analog Devices only provided canned responses.

## 2.5.4 Blackfin bug conclusions

The zero overhead hardware loop feature of the Blackfin opens up the possibility of a malicious

userspace process creating loops in the kernel. However, we are experiencing difficulty verifying whether it is a genuine exploit and in any case, it can be worked around.

## 2.6 Comparison to ARM

Recall that our focus is on supporting L4 efficiently on architectures without virtual memory, by drawing conclusions based on an implementation on the Blackfin architecture [p12, Chapter 1.1]. So while our focus will be on Blackfin, most of the results will generalise to other architectures without virtual memory.

In this section, we introduce two such architectures – ARM1156T2-S [Arm05, Wig99] and ARM7TDMI [Arm04] – and compare them with the Blackfin to provide a broader context for our research. We find that ARM1156T2-S is a very similar MPU-based chip to the Blackfin and that ARM7TDMI is similar to ARM1156T2-S but has no memory protection at all.

Throughout this document, all our conclusions should generalise to these chips except for the areas where we point out Blackfin-specific problems or features.

#### 2.6.1 ARM1156T2-S

This is a 32-bit RISC architecture with 37 registers, with 16 visible at any one time. There are different privileged modes for different types of exceptions and some registers are banked (e.g. The stack pointer and the link register) between usermode and kernel mode. The ARM features DSP instructions and a separate *Thumb-2* 16/32-bit instruction set for improving code density. The pipeline has 9 stages and features global branch prediction. This is all fairly similar to the Blackfin except that Blackfin has fewer protected modes and only has static branch prediction.

Both the ARM and Blackfin have trouble dealing with nested exceptions. Recall that Blackfin disallows exceptions within exceptions, so exception handlers must defer their work into interrupt handlers (which support a nested exception) [p16, Chapter 2.2]. With ARM, in the event that an exception occurs during the handling of the same type of exception, the link register is trashed. Therefore, the kernel must ensure that this situation never occurs – or switch modes just as Blackfin kernels are forced to.

Like the Blackfin, the ARM has separate instruction and data caches, which are both usually 4-way associative (like the Blackfin instruction cache). The line length is also identical to Blackfin with eight 32-bit words.

The ARM also has separate instruction and data untagged MPUs, each containing 16 entries. It also features protected kernel addressing, in which kernel accesses are constrained by the MPUs [p86, Chapter 7]. These aspects are identical to the Blackfin.

However, there are significant differences between the 2 chips. The ARM supports page sizes of every power of 2 from 32 *bytes* to 4GB while the Blackfin only supports 1KB, 4KB, 1MB and 4MB. MPU entries are permitted to refer to pages that overlap, unlike the Blackfin. Furthermore the ARM has hardware-loaded MPUs (based on a 2 level page table), while the Blackfin suffers from slower software MPU refills.

Recall that turning off the Blackfin MPU completely disables caching [p30, Chapter 2.3.3]. ARM is similar except that it reverts to a memory layout where the bottom 1.5GB or 2GB of the address space – according to a runtime configuration option – is cacheable.

The ARM supports changing of protection entries without disabling the MPU, unlike the Blackfin. However, disabling or enabling the MPU, for whatever motivation, requires flushing both caches. In contrast, disabling or enabling the MPU on the Blackfin only requires SSYNC pipeline flushes.

#### 2.6.2 **ARM7TDMI**

The ARM7TDMI is a simpler ARM chip with no virtual memory but its main difference is that it does not have memory protection. It used in Apple's extremely popular iPod music player so supporting L4 on this architecture would create the potential for massive, global L4 microkernel use. L4 would also provide an alternative to iPodLinux – a port of ucLinux to the iPod [Ipo06].

We aim to provide a unified L4 API for all non-virtual-memory architectures regardless of whether the architecture has an MPU, to reduce the porting effort for applications built on top of the microkernel. Ideally, to migrate applications to an MPU-less architecture, all we would need to do is simply need to disable the protection mechanisms.

## 2.6.3 ARM comparison conclusion

Our goal is to support L4 on architectures without virtual memory. While our focus is on the Blackfin, we realise that another popular MPU-based architecture – ARM1156T2-S – is extremely similar so our results will generalise. The important differences are that ARM's MPU is hardware-loaded, supports a much broader set of pages sizes and that MPU entries can refer to overlapping pages. We can also trivially support architectures without even MPUs, such as the ARM7TDMI (and also very similar), by simply turning off the protection.

## 2.7 Blackfin Architecture Summary

The following characteristics of the Blackfin were discussed:

- No virtual memory

- 32-bit architecture and 32-bit address space

- Exceptions cannot be nested so if we wish to allow exceptions while serving a first exception, we must switch to an interrupt mode on the initial exception

- Software-refilled Data Caching Protection Lookaside Buffer and Instruction Caching Protection Lookaside Buffer as MPUs.

We ran experiments to measure the speed of basic operations and cache misses. The important results we found were:

- Primitive instructions can be executed in 1 cycle

- Cached word accesses are just as fast as register accesses and also complete in just 1 cycle

- Cache misses cost in the order of 100 cycles so a key to good kernel performance is to minimise cache footprint

A potential kernel exploit utilising Blackfin's zero overhead hardware loop feature was described and workarounds suggested.

We also compared the Blackfin to other architectures without virtual memory so that our work can generalise:

- 1. ARM1156T2-S is a very similar chip, also with split instruction and data MPUs. However, its MPU is hardware-loaded and supports overlapping pages.

- 2. ARM7TDMI has an instruction set similar to ARM1156T2-S but does not have an MPU. We hope to support such MPU-less architectures using the same L4 API as for MPU architectures but with the protection functionality ignored.

## Chapter 3

# 3 L4 Background

Traditional *monolithic* operating systems, such as Linux or Windows, have millions of lines of operating system code running in the privileged kernel mode. A single bug – security or otherwise – in the kernel is likely to compromise the entire system.

This implies that the only way to develop reliable systems is to restructure operating systems to minimise the amount of privileged code. The centrepiece of this radically different structure is the L4 microkernel [Lie96] foundation, on which operating systems can be built to execute safely and efficiently in userspace.

In this chapter, we analyse *The Microkernel Approach* and motivate the need for operating systems to be built this way for reliability.

We then describe the various *Versions of L4*.

Finally, *Recent Developments* will cover relatively new, related work that will be incorporated into our thesis – namely, the N2 API, Single Stack Kernel and Physical TCB Arrays.

## 3.1 The Microkernel Approach

In an L4-based system, only the small microkernel (tens of thousands of lines of code) runs in kernel mode. A well-known claim is that a small "trusted computing base" [Nic06a] is much more likely to be correctly implemented and lends itself to formal verification. Traditional operating systems services are instead run as servers in usermode and should they fail, they can be restarted.

In this section, we introduce basic L4 abstractions and then provide further motivation for microkernel-based operating systems.

#### 3.1.1 Abstractions

The main L4 abstractions are address spaces, threads and Inter-Process Communication messages (*IPC*) [Nic05a].

## **Address Spaces**

Each address space can be viewed as a traditional "process" whose memory is isolated from other address spaces. Each address spaces contains 1 or more threads and maintains, in kernel space, a page table.

Address spaces provide for bug isolation as memory corruption from unrelated processes cannot occur.

#### **Threads**

L4 threads are the same as lightweight kernel threads in traditional operating systems.

Threads' IDs, kernel stacks, and other such information are stored in *Thread Control Blocks* (*TCBs*) in kernel space. Thread state shared between userspace and kernel space (e.g. message registers for IPC) is stored in *User Thread Control Blocks* (*UTCBs*).

#### **IPC**

Threads synchronise and communicate with each other via IPC and potentially, shared memory. This provides a strict, well-defined interface between different threads and processes in the system – in contrast to the ad-hoc structuring of monolithic systems such as Linux, where device drivers manipulate page table structures apparently directly [RC01 ch. 13].

As the primary communication mechanism in a microkernel-based operating system, IPC must be very fast even across address spaces. Ideally, this should be completed in tens of cycles but on most architectures, this can only be implemented in the order of hundreds of cycles or at worst, the low thousands. A distinguishing characteristic between L4 and previous generation microkernels, such as Mach, is in IPC performance [Lie96].

## 3.1.2 The microkernel advantage

Process isolation with address spaces and well-defined interfaces using IPC means that each process can be individually engineered and mathematically verified. This is not possible in a monolithic system where a memory bug in say, a driver, could compromise an unrelated system such as the virtual memory manager (unless a protection system hack such as Nooks is used [SML+02]).

But microkernels come at a cost. Firstly, proper object-orientated operating system design is, in the short term, more difficult than ad-hoc implementation. However, in the long term, it tackles the problem of increasing data and control flow complexity in traditional operating systems. Secondly, well-defined interfaces that happen to depend on address space switches are slower than simply accessing a variable or calling a function. It remains to be seen whether a real-world system can be constructed using a pure microkernel architecture and exhibit comparable performance to a traditional operating system.

## 3.2 Versions of L4

In this section, we describe the foundation for our work, NICTA L4-embedded, and previous work on porting different versions of L4 to other architectures.

#### 3.2.1 NICTA L4-embedded

NICTA L4-embedded [Nic05a] is NICTA's version of L4 with a focus on embedded systems. Based on the Pistachio tree, it is largely written in C++ so the code for any single architecture is between ten thousand to fifteen thousand lines of code. It is commercially relevant – more recently, Qualcomm has started developing chipsets based on L4-embedded [Nic05b]. Therefore, this thesis focuses on NICTA L4-embedded due to its active development and support within the ERTOS research group.

#### **3.2.2 Ports**

The L4-embedded [Nic06b] source tree contains working ports to other architectures – namely, ARM, IA32 and MIPS64. Their code served as reference implementations that guided the development of the Blackfin port. The MIPS64 port was referred to because it was straightforward and the IA32 port was used because it has the same word size and endian as the Blackfin.

Alpha [Pot99, Sch96], MIPS32 [Bla06e] and SPARC-V9 (by Philip Derrin but report is not published) ports of L4 – to name a few – are well-documented outside of the source code. However, as the discussions are very architecture-specific and given that they describe versions of the API that differ greatly from NICTA's [Nic05a], they are of limited use. Ports prior to Pistachio, of which L4-embedded is based upon, were written in assembler and are even less useful as references.

## 3.3 Recent Developments

The Blackfin port was based on an "N1.5" (between N1 and N2) version of the NICTA L4-embedded kernel. Recent research and development within the ERTOS group has steered the port in additional directions. We consider N2, the single stack kernel and the physically-addressed TCB changes.

#### 3.3.1 N2

We wrote an initial port of L4 to Blackfin to get a feel for the issues involved in microkernel construction [p47, Chapter 4]. However, in the meantime, the L4 *N-series* API [Nic05a] underwent continual refinement and progressed to the *N2* version. In order to pick up architectural changes, the Blackfin port was updated. This was so that performance analyses would still be valid for the current architectural state of the kernel rather than one long gone by.

This was time-consuming because there were many breaking changes on an implementation level but luckily, it was found that nothing significant – other than the addition of a cache management API – had actually been done.

## 3.3.2 Single Stack Kernel

When the initial port of L4 to the Blackfin was written, there was a kernel stack for every user thread, making context switches transparent to the majority of kernel code. However, reserving a stack for every thread in the system consumes a lot of memory and cache footprint. As a result, L4 is now moving to a continuation model with a single kernel stack [War05]. We will implement this and report our findings in this thesis [p113, Chapter 10].

## 3.3.3 Physical TCB Arrays