## THE UNIVERSITY OF NEW SOUTH WALES SCHOOL OF COMPUTER SCIENCE AND ENGINEERING

## **Efficient Concurrency Control for High-Performance Microkernels**

Anna Lyons

Supervisor: Gernot Heiser Assessor: Kevin Elphinstone

Thesis submitted as a requirement for the degree Bachelor of Computer Science (Honours) / Bachelor of Arts

November 15, 2011

#### Abstract

Concurrency control in OS kernels for multicore processor systems requires locking, which introduces complexity and overheads. One simple approach to avoiding data structure corruption is to avoid concurrency in the kernel by using one big kernel lock. Alternatively, one can identify critical sections and resources in the kernel and lock these individually, using lock ordering to prevent deadlock. Both approaches have their risks. Using many locks increases kernel complexity, risks deadlock and makes correctness hard to guarantee. But using a big kernel lock reduces scalability.

This project evaluates the giant-locking scheme of a high-performance microkernel with very short system calls, for present and near-future high-performance embedded hardware. We implement a light-weight instrumentation framework that reveals features of the system and provides detailed system traces. We investigate the scalability of a variety of workloads using simulation, and relate these to real workloads via a simple model.

#### Acknowledgements

Firstly, I would like to thank my supervisor Gernot for allowing me to undertake this project, even though I had yet to prove myself by succeeding in the Advanced Operating Systems course. I would like to attribute great thanks to my assessor Kevin, not for being my assessor, but for allowing me to take the time off work to focus on my thesis. You are going to enjoy a much better read as a result!

Thanks to my mentor, Aaron, for helping me every step of the way, from handling Linux faulting on global variables to showing me how to represent data in a more meaningful fashion by organising it in better charts.

Thanks to Justin, for the tissues and for reading through my results at literally the last minute, and to Tim, for reading my entire report before I had spell checked it. And thanks James, for being just as stressed as me and taking to time to give valuable opinions and help anyway.

In Swedish they have a phrase which is so much more effective than anything we use in English. "Tusen tack". I know people use it in English too, but the Swedish syllables make it far more rewarding.

# Contents

| 1 | Intro | Introduction                              |    |  |  |

|---|-------|-------------------------------------------|----|--|--|

|   | 1.1   | Goals                                     | 7  |  |  |

|   | 1.2   | Thesis Overview                           | 7  |  |  |

| 2 | Back  | sground                                   | 9  |  |  |

|   | 2.1   | Microkernels, Microvisors & Hypervisors   | 9  |  |  |

|   |       | 2.1.1 OKL4                                | 10 |  |  |

|   | 2.2   | Synchronisation                           | 10 |  |  |

|   |       | 2.2.1 Synchronisation in the Linux Kernel | 12 |  |  |

|   |       | 2.2.2 Amdahl's Law                        | 12 |  |  |

|   | 2.3   | Platform                                  | 14 |  |  |

|   | 2.4   | Summary                                   | 14 |  |  |

| 3 | Rela  | ted Work                                  | 15 |  |  |

|   | 3.1   | Mach                                      | 15 |  |  |

|   | 3.2   | Raven: A Microkernel for SMPs             | 15 |  |  |

|   | 3.3   | A Lock Free Multiprocessor OS Kernel      | 16 |  |  |

|   | 3.4   | Lock Free L4                              | 17 |  |  |

|   | 3.5   | Corey                                     | 18 |  |  |

|   | 3.6   | Hierachial Clustering                     | 18 |  |  |

|   | 3.7   | Multikernel                               | 19 |  |  |

|   | 3.8   | Microkernel Scalability                   | 19 |  |  |

|   | 3.9   | Fine-grained Locking                      | 20 |  |  |

|   | 3.10  |                                           | 20 |  |  |

|   | 3 1 1 | Summary                                   | 20 |  |  |

| 4 | App | roach   |                                                                   | 22 |

|---|-----|---------|-------------------------------------------------------------------|----|

|   | 4.1 | Design  | 1                                                                 | 22 |

|   | 4.2 | Instrun | nentation and Logging                                             | 23 |

|   | 4.3 | Worklo  | oad Benchmarking                                                  | 24 |

|   | 4.4 | Simula  | ation                                                             | 26 |

| 5 | Imp | lementa | ition                                                             | 28 |

|   | 5.1 | Instrun | nentation & Logging                                               | 28 |

|   |     | 5.1.1   | Log buffer                                                        | 28 |

|   |     | 5.1.2   | Lock instrumentation                                              | 30 |

|   |     | 5.1.3   | Microvisor system calls                                           | 33 |

|   |     | 5.1.4   | Instrumentation library                                           | 34 |

|   |     | 5.1.5   | Linux system calls                                                | 35 |

|   |     | 5.1.6   | Limitations of the logging implementation                         | 36 |

|   | 5.2 | Simula  | utor                                                              | 36 |

|   |     | 5.2.1   | Implementation                                                    | 37 |

|   |     | 5.2.2   | Limitations                                                       | 41 |

| 6 | Exp | eriment | tation, Results & Analysis                                        | 43 |

|   | 6.1 | Micro-  | benchmarks                                                        | 43 |

|   |     | 6.1.1   | System call entry & exit cost                                     | 43 |

|   |     | 6.1.2   | Lock latency                                                      | 44 |

|   |     | 6.1.3   | Instrumentation effects on one processor                          | 46 |

|   |     | 6.1.4   | Lock latency and instrumentation effects over multiple processors | 48 |

|   |     | 6.1.5   | Lock-exit latency                                                 | 48 |

|   | 6.2 | Macro   | -benchmarks                                                       | 51 |

|   |     | 6.2.1   | Limitations                                                       | 52 |

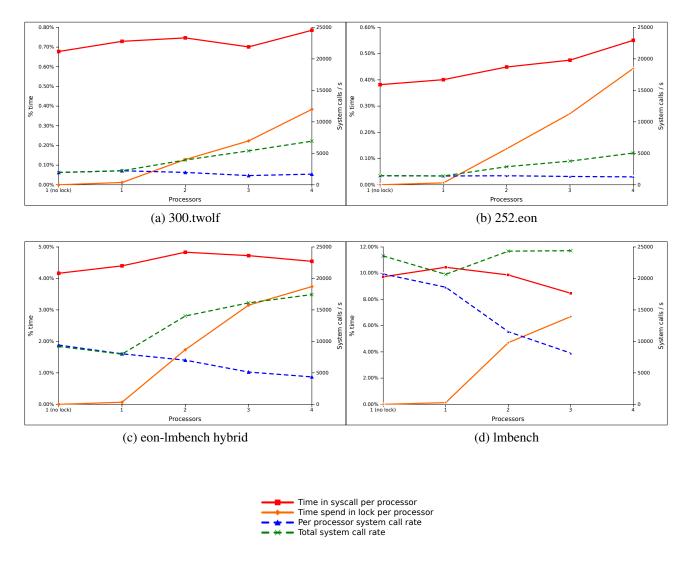

|   |     | 6.2.2   | Test-set: Imbench                                                 | 52 |

|   |     | 6.2.3   | Test-set: 300.twolf                                               | 53 |

|   |     | 6.2.4   | Test-set: 252.eon                                                 | 53 |

|   |     | 6.2.5   | Test-set: eon-Imbench hybrid                                      | 54 |

|   |     | 6.2.6   | Workload analysis                                                 | 56 |

|   | 6.3 | System  | n call analysis                                                   | 60 |

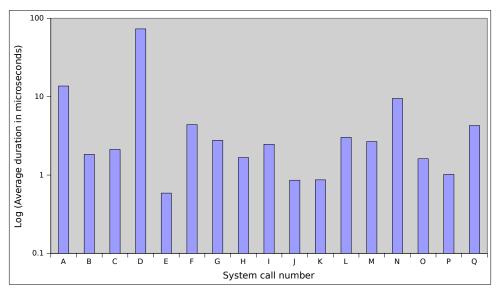

|   |     | 6.3.1   | System call duration                                              | 60 |

|   |     | 6.3.2   | System call occurrences                                           | 61 |

|     |              | 6.3.3   | System call impact                            | 64 |

|-----|--------------|---------|-----------------------------------------------|----|

|     | 6.4          | Simula  | tion                                          | 65 |

|     |              | 6.4.1   | Simulator accuracy                            | 65 |

|     |              | 6.4.2   | Simulated scalability                         | 66 |

|     |              | 6.4.3   | Simulated lock latency                        | 67 |

|     |              | 6.4.4   | Simulated coarse grained locking              | 70 |

|     | 6.5          | Real w  | orkloads                                      | 74 |

| 7   | Cond         | clusion |                                               | 77 |

|     | 7.1          | Future  | Work                                          | 77 |

| A   | Instr        | rumenta | ition effects                                 | 80 |

| B   | SMP          | OKL4    | and Locking                                   | 82 |

|     | <b>B</b> .1  | Impact  | of make_consistent on system call scalability | 83 |

| Bil | Bibliography |         |                                               |    |

# **List of Figures**

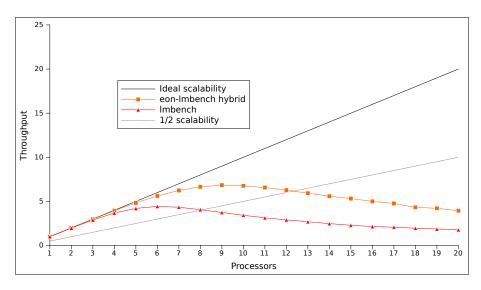

| 2.1 | The ideal scalability curve in contrast with more realistic curves                      | 11 |

|-----|-----------------------------------------------------------------------------------------|----|

| 4.1 | Points at which the cycle counter will be read                                          | 24 |

| 4.2 | The stages of a system call with reference to the instrumentation points shown in       |    |

|     | Figure 4.1                                                                              | 25 |

| 5.1 | Layout of the log buffer and helper pages.                                              | 29 |

| 5.2 | Layout of data in the 3 words that form an entry in the log buffer                      | 30 |

| 5.3 | Lock entry instrumentation                                                              | 31 |

| 5.4 | Lock exit instrumentation                                                               | 32 |

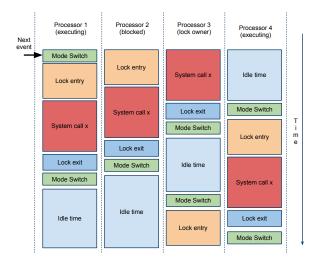

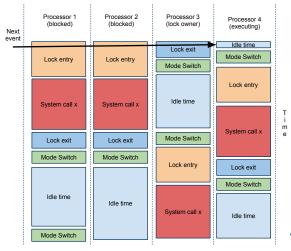

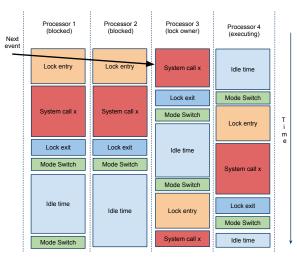

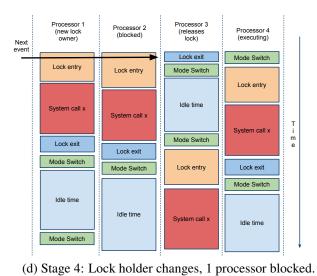

| 5.5 | A sample execution of the simulator, showing a replay of a 4 processor trace            | 40 |

| 5.6 | Sample simulator configuration file                                                     | 42 |

| 6.1 | Lock exit instrumentation for measuring lock exit cost only                             | 49 |

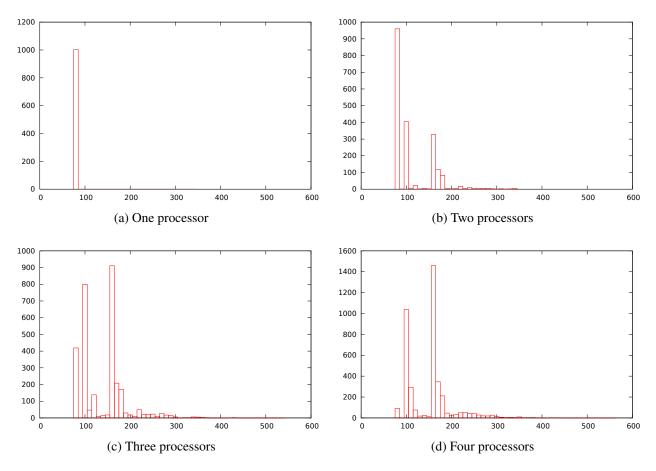

| 6.2 | Lock exit latency on a highly contended lock, over 1 – 4 processors. Each processor     |    |

|     | completed 1000 system calls. Axes are frequency vs. cycles                              | 50 |

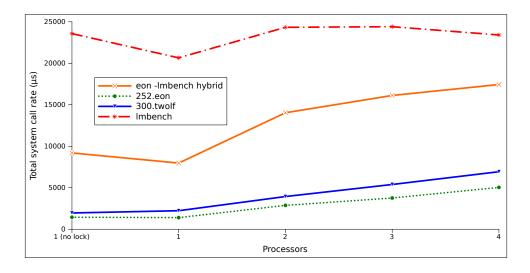

| 6.3 | Characteristics of each workload, over 1 to 4 processors. Note that the left y-axis of  |    |

|     | each graph does not use the same scale; since the larger workload ranges would dwarf    |    |

|     | the smaller workloads                                                                   | 55 |

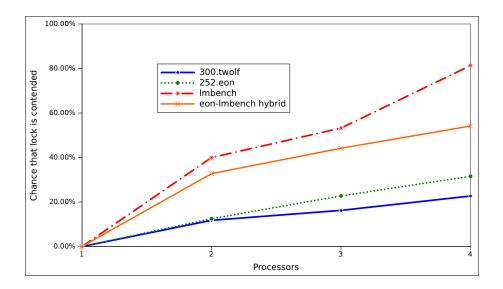

| 6.4 | This graph shows, for each workload over 1–4 processors, how likely the lock was to     |    |

|     | be contended when a processor tried to take the lock                                    | 57 |

| 6.5 | This graph shows how the total system call rate varied between workloads                | 58 |

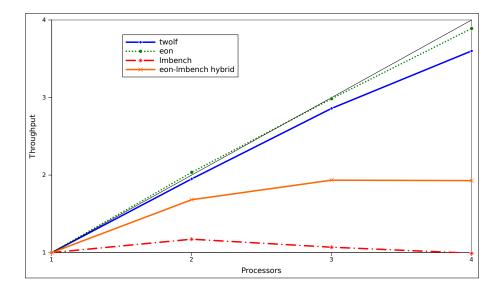

| 6.6 | This graph shows a normalised scalability curve for each workload. It is based on the   |    |

|     | time taken to complete the workload. A reference line is shown for ideal scalability    | 59 |

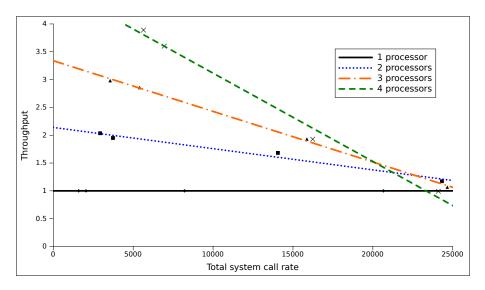

| 6.7 | This graph shows throughput vs. total system call rate and illustrates the relationship |    |

|     | therein                                                                                 | 59 |

|     |                                                                                         |    |

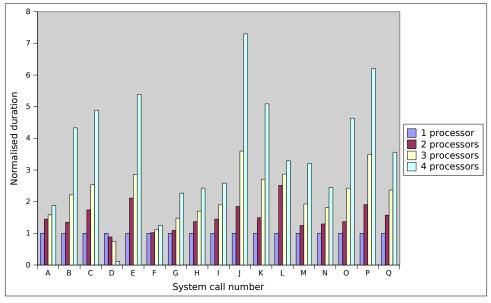

| 6.8  | These two charts show the average durations of system calls made during an Im-         |    |

|------|----------------------------------------------------------------------------------------|----|

|      | bench workload and how the average system call durations increase as we increase       |    |

|      | the amount of workloads and processors. Note the values for four processor lm-         |    |

|      | bench are missing system call counts for one Linux instance                            | 62 |

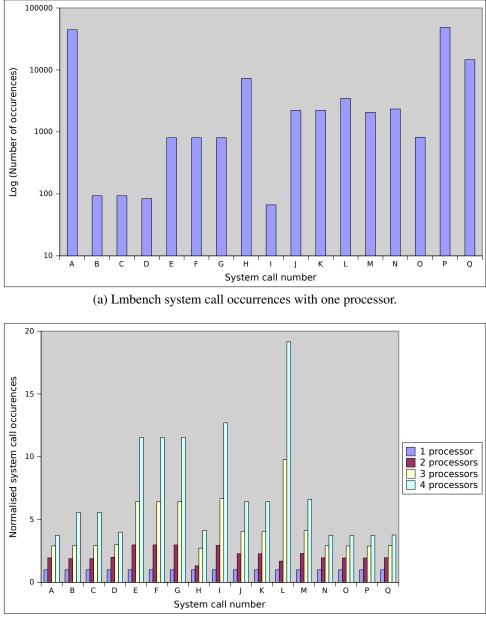

| 6.9  | These two charts show the amount of system calls made during an Imbench workload       |    |

|      | execution and how these values increase as we add processors and increase the amount   |    |

|      | of workloads. Note the values for four processor lmbench are missing system call       |    |

|      | counts for one Linux instance.                                                         | 63 |

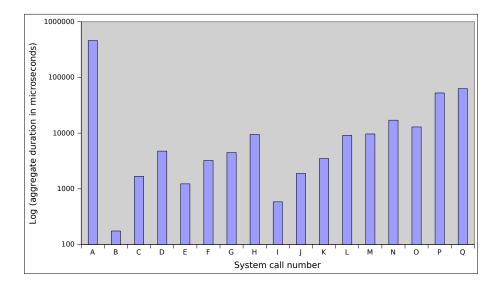

| 6.10 | This chart shows the total amount of time spent in each system call during a one       |    |

|      | processor lmbench workload                                                             | 64 |

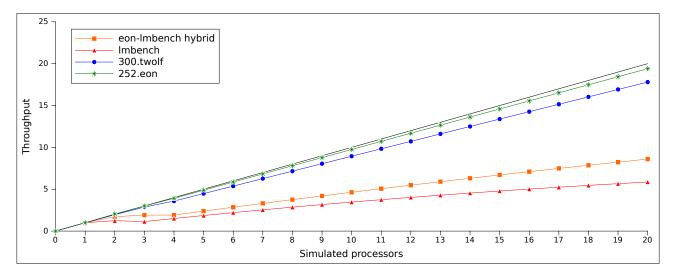

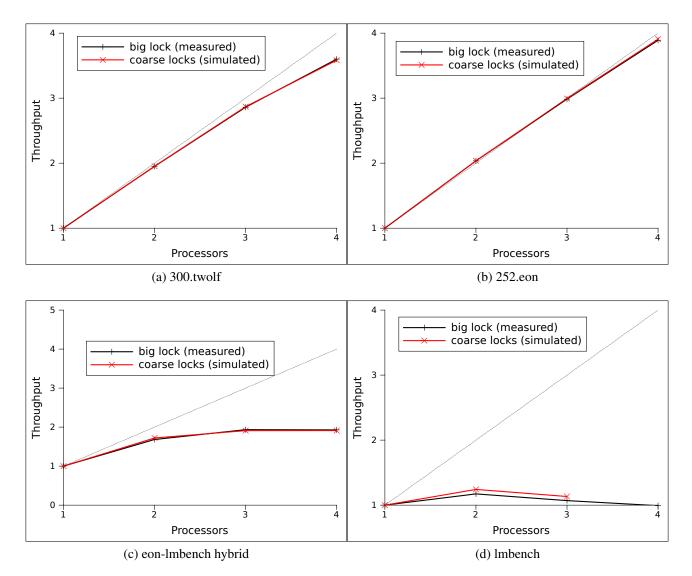

| 6.11 | The simulated scalability of all four of the workloads                                 | 66 |

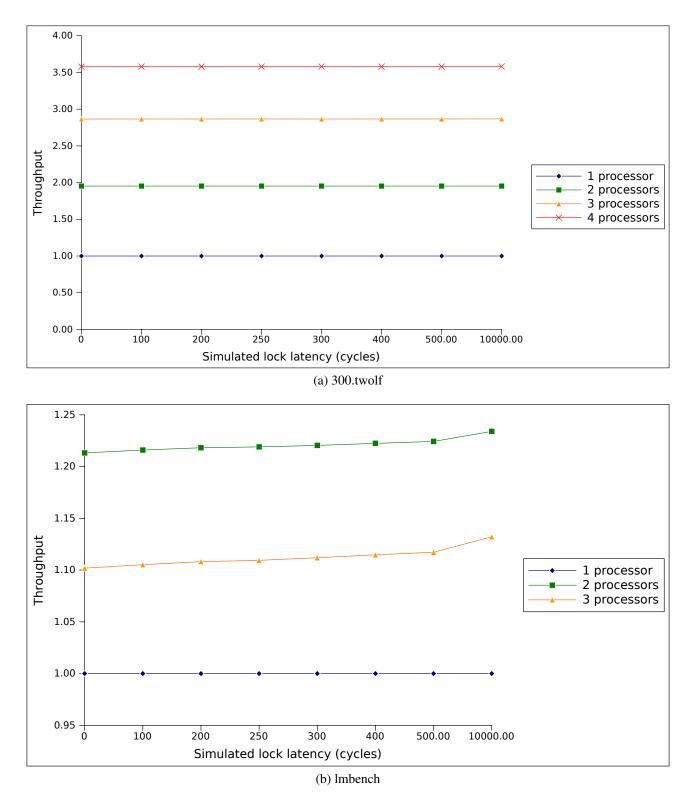

| 6.12 | These two charts show the effect of a changing lock latency on the scalability of a    |    |

|      | workload                                                                               | 68 |

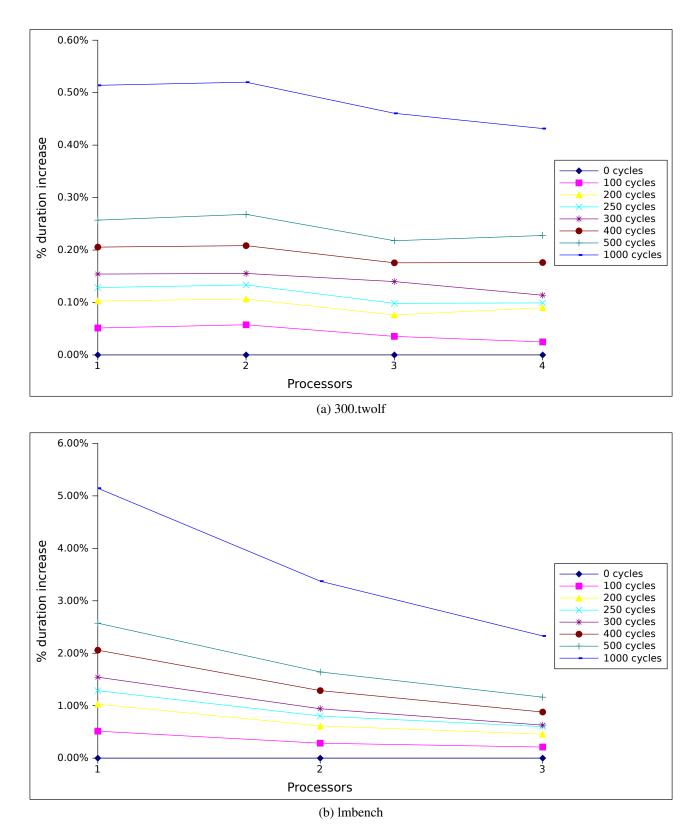

| 6.13 | These two charts show the effect of a changing lock latency on workload duration.      | 69 |

| 6.14 | The modelled scalability of the workloads using coarse grained locking                 | 71 |

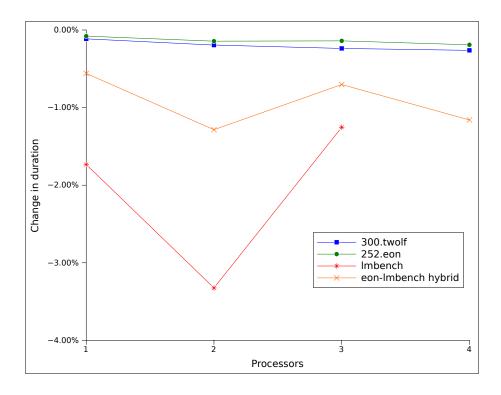

| 6.15 | The modelled effect of coarse grained locking on workload duration. In all cases it    |    |

|      | reduces the workload time, but not by much                                             | 72 |

| 6.16 | The simulated scalability of all four of the workloads with a simulated coarse grained |    |

|      | locking scheme                                                                         | 73 |

|      |                                                                                        |    |

## Chapter 1

## Introduction

In recent years, multiprocessors have gained an increased popularity along-side their single-core, single-threaded predecessors. The driving force behind this change is that it has become cheaper to produce several less powerful processors that work together, rather than focus on manufacturing faster single uniprocessors. Other advantages are also present in the form of improved power efficiency, parallelism, fault tolerance and increased performance. Using multiple cores allows for increased power efficiency, as unused processors can be switched off. Multiple cores can allow for significant performance increases through designing programs to harness their parallelism [Sch94].

Nevertheless, significant improvements do not come without a cost. Operating systems (OS) for multiprocessor processors require different designs to manage multiple processors and take full advantage of the benefits available. There are many different styles of multiple processor systems, however this project will focus on operating-systems approaches for shared-memory symmetric multiprocessing (SMP). SMPs are multiprocessor systems which present uniform access to shared memory for all processors. Operating system data structures are stored in this shared memory, accessible by all processors. There are two key factors to designing OSs for SMPs. First, the integrity of shared data structures must be preserved through synchronising any access to them. Second, performance must not suffer as a result of the synchronisation methods employed.

Much of the previous research into synchronisation on SMPs focuses on scalability for monolithic kernels or other very large scale systems, designed for tens and hundreds of processors. However, multiprocessors for embedded devices are already emerging, with the iPad 2 released this year having a dual-core processor.

One synchronisation approach that is generally thought to be unscalable is to place one lock around any OS operations, effectively single-threading the kernel. This approach is referred to as *giant locking*. Another approach, one that is thought to afford greater scalability, is to use many locks

to protect shared resources. The amount of locking used is referred to as the *lock granularity*. The finer the lock granularity, the harder the OS becomes to design and change. System calls become more complex and correctness becomes very difficult to prove. Our hypothesis is that for high-performance, SMP microkernels (characterised by very short system calls) on tightly integrated chips, the overhead of giant locking will be small enough for a limited amount of processors.

## **1.1 Goals**

The goal of this thesis is to investigate the scalability of a giant locking scheme on the OKL4 SMP microvisor, and establish the features of the current locking implementation. We develop a light-weight instrumentation framework in order to extract detailed system traces during a the execution of a variety of workloads over 1 - 4 processors. Finally, we use simulation to investigate scalability over more processors, the effect of lock implementation in a giant locked system, and to model a theoretical coarse-grained locking model.

### **1.2** Thesis Overview

Chapter 2 provides a background and broader examination of the ideas presented in the introduction, including a brief introduction to microvisors, a look at the trade-offs involved in lock-granularity, and an overview of the hardware platform used in experiments during this thesis.

Chapter 3 surveys a range of relevant related work, however it does not attempt to cover all of it as synchronisation on operating-systems is a widely explored topic. We take a look at previous SMP microkernel implementations, lock-free synchronisation approaches, applying distributed systems techniques to multiprocessor systems and previous instrumentation techniques for analysing locking.

Chapter 4 presents the overall approach and vision for this thesis project, as well as rationalising broader decisions and the relationship between different components of the implementation.

Chapter 5 takes a detailed look at the implementation of all of the systems implemented as a part of this thesis project. The chapter describes the design and implementation of an instrumentation and logging system for the OKL4 microvisor, the development of workloads for experimentation and the design of a simulator for modelling fine-grained locking.

Chapter 6 details many of the experiments run and their results, including micro-benchmarks of the OKL4 giant-lock, analyses of system traces and simulation results.

Chapter 7 presents an evaluation of the suitability for giant-locking versus a more coarse-grained approach based on the results of the experimentation and simulation.

## Chapter 2

## Background

The operating systems that are most commonly used in everyday life, such as Windows and Linux, have kernels that are referred to as *monolithic*. The *kernel* is the part of the OS that operates with privileged access to the processor in order to safely perform tasks that allow applications to run independently of each other. Monolithic operating systems contain all services required to run applications within the kernel. They are generally very large, complex systems that are difficult to maintain and impossible to assert correctness about.

## 2.1 Microkernels, Microvisors & Hypervisors

A *microkernel* attempts to minimise the amount of features in the kernel to achieve a small trusted computing base. Microkernel-based systems implement much of the operating system functionality as user-level servers run in separate address spaces. The servers communicate using interprocess communication (IPC) that is built into the microkernel and are otherwise isolated from each other and use separate resources. Microkernels have very small code bases and attempt to achieve minimal complexity.

Of particular relevance to this project is the fact the long-running, complex system calls of monolithic OSs are no longer system calls, but implemented externally by user-level servers. Examples of such system calls include file system interaction and I/O. Due to this fact, critical sections in a giant-locked microkernel are much shorter than for a giant-locked monolithic kernel. Accordingly giant locking can be expected to scale further on a microkernel.

#### 2.1.1 OKL4

OKL4 is a third-generation, L4 [Lie95] family *microvisor* that we use for this project. A microvisor [HL10] is a microkernel that satisfies the objectives of both a microkernel and a *hypervisor*. A hypervisor is a highly efficient operating system designed to run multiple guest operating systems simulaneously, even if the guest operating systems do not support the hardware platform that the hypervisor is running on. OKL4 is distinct from previous L4 microkernels, in that it only offers asynchronous IPC in the form of *virtual IRQs*.

OKL4 is SMP-capable and can run on ARM uniprocessors and multiprocessors. Multiple versions of Linux can runs as guests on the OKL4 microvisor, which is used in generating the workloads used in this project. Each Linux runs on one *virtual CPU* (vCPU) and uses one *virtual MMU* (vMMU). A virtual CPU is effectively a single task, and a virtual MMU is the associated address space. The Linux that we run is Linux for a uniprocessor, not SMP Linux. As a result Linux's own locking scheme does not interfere with the results of this research.

For more detail on the SMP design of OKL4 and its locking strategy, see Appendix B.

#### 2.2 Synchronisation

There are many ways, proposed and in practice, to synchronise kernel data structures for SMPs. As referred to in the introduction, one approach is to use giant locking. That is, to lock any access to the kernel with one lock. This approach effectively single-threads the kernel, as only one processor can be executing kernel code at a time. This means that system calls, interrupt requests, page faults or anything else requiring entry to the kernel must be accessed through the giant lock.

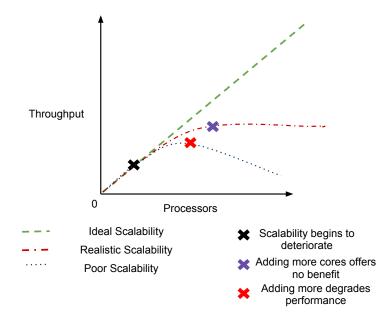

This lock can easily become a bottleneck reducing system *scalability* under *contention*. Contention of a lock occurs when more than one entity requires access to the lock at the one time. Scalability refers to how the entire system performs when adding more processors. For the purposes of this thesis, we will assess scalability as a function of cores vs. *throughput*. Throughput is dened as how much work the system can get done per unit of time. In an ideal system, adding a new processor should increase the throughput by  $\frac{1}{n+1}$ . The scalability of a locking system can be evaluated by examining how much throughput is added by adding new processors. Higher scalability refers to a throughput increase closer to the ideal, whilst lower scalability refers to something further away from the ideal. Figure 2.1 shows the ideal scalability curve in constrast with some more realistic scalability curves.

Alternatively, one can increase lock granularity, dividing shared data structures into small, self-

Figure 2.1: The ideal scalability curve in contrast with more realistic curves.

contained segments and critical sections that can be locked individually. Lock ordering is used to prevent deadlock. This approach, designed properly, can result in an implementation that scales much better than a single kernel lock. However designing a fine-grained locking scheme that is correct is non-trivial. If one is adapting an existing kernel, often there are many different code paths leading through separate resources and identifying critical sections becomes difficult [JAdG86].

|                             | Giant Locking | Fine-grained Locking |

|-----------------------------|---------------|----------------------|

| Implementation Cost         | +             | -                    |

| Correctness guarantees      | +             | -                    |

| System call complexity      | +             | -                    |

| Scalability                 | -             | +                    |

| Latency under no contention | +             | -                    |

Table 2.1: Fine-grained vs. giant locking.

As a result, giant locking cannot be discarded completely. Adding more locks increases system complexity and provides greater room for crippling problems. One runs a high risk of deadlock and each lock added increases the complexity of system calls, making the system less efficient for cases of low contention. In addition, more locks makes correctness very hard to establish.

Table 2.1 presents a quick summary of the two extremes of giant locking and very fine-grained

locking. A '+' indications the advantaged scheme and a '-' indicates a disadvantaged scheme. From examining the table it can be seen that if the system scales well enough for the target hardware and kernel, giant locking would be the favoured result. However, if giant-locking does not scale well enough the benefits are irrelevant.

Lock performance is affected by critical section length. Shorter critical sections allow for greater scalability, as processes spend less time in them thus reducing contention. When using giant locking, the system calls themselves are effectively critical sections.

#### 2.2.1 Synchronisation in the Linux Kernel

Linux 2.0 utilised giant locking. However it was quickly found that this lock became a large bottleneck, causing uniprocessor Linux to perform similar workloads more efficiently than SMP Linux on multicore processors. Performance improvements have been gained by slowly adapting the kernel to have finer lock granularity.

In 2.2, one spin lock controlled access to the block I/O subsystem; another worked for networking, and so on. A modern kernel can contain thousands of locks, each protecting one small resource. This sort of fine-grained locking can be good for scalability; it allows each processor to work on its specific task without contending for locks used by other processors. Very few people miss the big kernel lock [CRKH05].

In general, monolithic operating systems developers, such as Linux kernel developers, have perceived that fine-grained locking implemented properly greatly outperforms coarser granularities of locks. But we must note that in the conventional monolithic systems, most services are implemented in the kernel. The implication is that a standard user load is composed of software applications that frequently make expensive system calls to I/O devices and file systems. Long system call duration means a giant lock is highly contended, as each processor must wait for other processors to leave the kernel before proceeding. As a result, throughput is limited. One can deduce this from the fact that Linux 2.0 experienced a significant performance hit for very few cores, with a significant amount of time spent waiting on locks [CRKH05].

#### 2.2.2 Amdahl's Law

To find the maximum expected improvement to an overall system when only part of the system can be improved, Amdahl's law [Amd67] is used. When Amdahl's law is applied to parallelisation, we get

the following property: the theoretical maximum speedup that can be achieved using N processors, where P is the section that can be parallelised, is:

$$\frac{1}{(1-P) + \frac{P}{N}}$$

A large part of parallel programming is spent minimising (1 - P).

To further rationalise why revisiting the giant-locking versus fine-grained locking debate with application to microkernels, we can argue according to an amended form of Amdal's law. Consider that, when applied to giant locking, *P* becomes the user time with (1 - P) representing time spent in the kernel. Applying fine-grained locking around shared data-structure accesses reduces the amount of time spent in the kernel and thus increases *P*.

However, the analysis above is missing one key factor. When considering any system one cannot simply slice a workload into P and (1 - P). Synchronisation techniques used to control access to the non-parallel section add more time to the original workload. So the formula used to express the actual (as opposed to maximum) speed-up that can be achieved using N processors could be expressed as:

$$\frac{1}{(1-P)+\frac{P}{N}} - f(N,C)$$

where f(N,C) is the overhead added by synchronisation techniques, i.e. the overhead is a function of N, the number of processors and C, the contention of the lock. But the function f itself is not so clear cut. The overhead added by a lock is a product of a number of things. First, the locking code itself adds a constant minimum overhead, which varies depending on the order of processors accessing the lock. If one processor accesses the lock over and over again, no cache operations will take place as no other processors will need to access the shared memory used in the lock. However, even at no contention, if several processors access a lock one after the other, the time taken to execute the lock code will increase due to the cache coherency operations of the hardware. Additionally, if the lock is contended, the time a processor waits in a lock is added to the locking cost.

When applied to giant-locking, we can see that f(N,C) is just the cost of the one lock, increasing as more processes access the lock. Fine-grained locking seeks to minimise (1-P) but at the same time increases f(N,C) by including more locks. However, fine-grained locking aims to reduce contention, with processors waiting on different, less contended locks rather than one highly contended lock. As such, fine-grained locking also undesirably increases f(N,C). Fine-grained locking will only succeed over giant-locking if the decrease in (1-P) is signifigantly greater than the increase in f(N,C).

For a monolithic kernel such as Linux it is understandable that (1 - P) is very large, such that fine-

grained locking greatly decreases it whilst the increase in f(N,C) is minimal. Additionally, due to the diversity of services offered from within Linux, one can expect that the cost of some fine-grained locks will be greatly reduced as less processes will be accessing them. For example, consider a lock protecting the sound driver. Only processes playing sound need to access this lock, thereby reducing potential cache effects and contention that would increase the cost of the lock.

However, for a microkernel the gains of fine-grained locking are far less clear. The time spent in-kernel should be a small percentage of a total workload, thus (1 - P) is not as large as it may be, and there are far less resources and shared data structures to divide up. As only essential services are included in the microkernel, it is far more likely that most processes will need access to most of the resources. A smaller (1 - P) means that it is much more likely that increases in f(N,C) will come closer to the decrease in (1 - P).

### 2.3 Platform

All experiments were carried out on a NaviEngine<sup>®</sup>1 [YST<sup>+</sup>07] multiprocessor platform, using 4 ARM11<sup>TM</sup> MPCore processors with 256MiB of memory. Processor clock speed is 399 MHz and the architecture version is ARMv6. The ARM11 has an eight-stage pipeline and no L2 cache.

The benchmarking conducted in this thesis required signifigant use of the processor monitor unit (PMU) for each processor. Each PMU has one cycle counter, which can be set to tick every cycle or every 64<sup>th</sup> cycle. In addition, each PMU has two event counters, which can be set to measure cycles, or other performance characteristics including cache misses, instructions executed and branch mispredictions. The cycle counters on the PMU can only be read in privileged mode.

### 2.4 Summary

Previous uses of giant-locking have been on monolithic kernels with long system calls and high complexity, where giant locking was not feasible for even two processors.

The OKL4 microvisor, aimed at embedded systems provides us a platform to revisit giant- locking. We investigate that the prior criticisms of giant-locking, with the idea that they will not apply due to the unique features of OKL4 SMP and that giant-locking will provide comparable scalability to finergrained locking, without the associated risks.

## Chapter 3

## **Related Work**

#### 3.1 Mach

Mach [ABB<sup>+</sup>86] was one of the first microkernel implementations with a design goal of being not only multiprocessor-capable, but to offer system functions that did not limit parallelism. The major features of Mach include thread and task management, IPC, memory management, device support, multiprocessor and multicomputer support. Mach was designed to be able to run on non-uniform multiprocessor architectures as well as uniform memory architectures (or SMPs). Note that unlike L4 microkernels, the Mach microkernel kept device support and thread-management inside the kernel.

For synchronisation within the kernel, Mach used coarse-grained locking, including a lock around a shared run queue for global scheduling [Bla90].

Given Mach's poor IPC performance, even in contrast to the predecessors of L4 [Lie93], it is understandable that a giant-locking scheme would never be feasible, as the time spent in the kernel would be too long to be treated as one critical section. However, L4 microkernels offer much faster IPC performance [LES<sup>+</sup>97] and shorter system calls.

### 3.2 Raven: A Microkernel for SMPs

Ritchie and Neufeld [RN93] present the Raven microkernel, designed to provide a lightweight environment for multithreaded, parallel applications. Like Mach, this microkernel was targeted at SMP platforms with a small numbers of processors (up to four) and was tested on a Motorola MVME188 Hypermodule with four MC88100 RISC microprocessors. Raven is a similar microkernel to those of the L4 family, with the supervisor kernel (essentially the microkernel) providing basic abstractions

such as threads and virtual memory management. One major difference is present in the fact that a user-level threading library communicates with a per-process shared-memory section within the kernel. A second major difference is that IPC is implemented at user level. Interprocess communication is implemented in the user-level kernel using shared memory to avoid the perceived performance cost of mode switching for communication.

The implementors found that using simple test&test&set [Rit93] spin locks for in-kernel synchronisation was sufficient to attain good performance. Although the synchronisation scheme is not described in great detail, they refer to using multiple spin locks to synchronise access to in-kernel critical sections in both parts of the kernel. This can be considered to be fine-grained locking. The author notes that on other hardware, cache coherency could form a bottleneck that would be amended by using more complex spin-lock based locking procedures. The hardware Raven was designed for implemented a memory bus snooping protocol to allow for cache coherency between all caches in the system, reducing contention caused by spin locks.

The Raven kernel is relevant as it is a microkernel designed for small-scale SMPs. It also shows the use of a locking scheme suitable just for a specific set of hardware using a simple style of lock rather than something more complex for scalability. However Raven appears to be just that — designed as a proof of concept at a stage when multiprocessor hardware approached a more accessible cost. Scalability is not a design factor, neither is high performance or power management. Additionally, Raven uses shared memory between the kernel and the user-level threads library rather than IPC, based on the performance of poorly implemented IPC mechanisms in Mach [ABB+86]. However, IPC performance has increased dramatically with second-generation microkernels (such as L4), so such shared-memory management (which introduces security risks as well as memory management overhead) is not required.

### 3.3 A Lock Free Multiprocessor OS Kernel

Massalin and Pu [MP91] demonstrated that it is possible to implement SMP kernels without using locks at all. The approach in this paper implements all kernel data structures as lock-free using single and double word compare-and-swap operations. The authors adapt the Synthesis kernel [PMI88] and run it on a dual-68030 Sony NeWS workstation, claiming minimal overhead.

However it is important to note that without compare-and-swap being implemented efficiently by the hardware, this sort of approach has so far been found to be infeasible. The authors claim by using such a lock free implementation synchronisation overhead is avoided, there is increased concurrency, avoidance of deadlock. Priority inversion is also eliminated.

The benchmarks shown are only for two processor hardware, so it is impossible to tell how the implementation scales. It is possible that the bus contention created by using compare-and-swap so frequently would cause performance degradation comparable to using spin locks given more cores.

As with the Raven microkernel, this kernel was implemented as a proof of concept and not as production software. It depends on specific hardware operations and has not been designed specifically for scalability. The authors acknowledge that without native hardware compare-and-swap, locks are necessary. Applying the same methods to larger scale production software was not in the scope of the project.

#### 3.4 Lock Free L4

Hohmuth and Härtig [HH01] approach lock-free synchronisation by developing an L4 microkernel, Fiasco, with the aim of building nonblocking real-time systems. The system incorporates locks whilst preserving the property of being wait-free. Fiasco, at the time, ran only on uniprocessors, however the authors assert that the approach lends itself well to multiprocessor-system implementations. Lockfree synchronisation is used to implement frequently-accessed global state, and wait-free techniques are used for global state that is not relevant to real-time components of the system.

Fiasco does not depend on double-word compare-and-swap, unlike the Synthesis kernel implementation described above. Instead, interrupts are disabled to perform multiword atomic updates. The authors recommend using simple spin-locks to conduct such updates with a multiprocessor. Fiasco could only be targeted at a small number of processors if it were to use such a technique.

Of particular interest is how Fiasco handles the synchronisation of thread state. Part of the thread state is protected by wait-free locks, however the IPC-critical portion of thread state uses lock-free synchronisation.

By using a minimal number of locks, Fiasco avoids the high risk of deadlock found in finegrained locking implementations. However, a risk of deadlock definitely exists, with the described implementation including a lock count for each thread to make sure a thread does not sleep while holding a lock. The careful interleaving of lock-free data structures with wait-free locking appears to be similarly hard to get completely correct as a fine-grained locking implementation. Finally, whilst the authors claim that Fiasco would be easily adapted to and perform well on a multiprocessor system, we lack a solid implementation with benchmarks to see how well it could scale. The authors refer to research showing that lock-free approaches offer less overhead than wait-free or lock-based synchronisation techniques [ARJ97]. This research, however is only focused on uniprocessors and does not consider the expense of atomic operations on multiprocessor architectures.

### 3.5 Corey

Boydwickizer et al. [BWCC<sup>+</sup>08] present an OS named Corey designed explicitly to reduce sharing in order to increase scalability. Specifically they allow applications to define sharing requirements for kernel data. The paper argues that the kernel should arrange data structures such that only one processor need update it, unless applications specify otherwise. They achieve communication through shared memory.

When sharing across processors is required, Corey uses MCS locks as presented by Mellor-Crummey and Scott [MCS91] with fine-grained locking. Corey was tested on Intel Xeon and AMD Opteron processors with up to sixteen cores. Benchmarks are run in comparison with Linux showing a 25% speed improvement, although the authors acknowledge that Corey is not a fully fledge monolithic OS and lacks a lot of the features that cause Linux to operate slower. However they do claim most of the performance gain is relative to the scalability enhancements made in the design of Corey.

This paper is of interest to us because it claims increased scalability based on a reduction in locking and use of fine-grained locking. Their findings will differ significantly from ours as Corey is based on a monolithic kernel, written from the ground up to achieve scalability. As far as we have read it is not aimed at embedded systems, and to apply the synchronisation and data organisation techniques in Corey would require substantial changes to OKL4.

### **3.6 Hierachial Clustering**

Many approaches to operating system scalability propose the use of distributed systems principles in order to develop a scalable microkernel operating system. Hierachial clustering as presented in Urau et. al. [USK93] aims to produce an operating system for a broad range of memory models (non-uniform multiprocessor architectures (NUMA) as well as SMP) suitable for a high number of processors. Small groups of processors are assigned to different *clusters*, where each cluster shares kernel data structures as a small-scale, efficient multiprocessor operating system. For large systems there are multiple clusters, which communicate and collaborate through shared memory to present the interface of a single operating system.

In specific application to this thesis topic, clustering is used to reduce the amount of fined grained locking. By representing the operating system as a collection of operating systems, each for only a few processors, the authors attain a much coarser granularity of locking thereby simplifying the entire system and reducing risk of deadlock and concurrency errors. Results are presented that show that smaller clusters have lower contention, thereby reducing the stress on the coarse grained locking

system and increasing kernel response time.

### 3.7 Multikernel

Yet another approach furthers the use of distributed system concepts so far as to treat the entire system as a distributed system. This is presented as a *multikernel* approach in Baumann et al. [BPS<sup>+</sup>09, BBD<sup>+</sup>09]. Message passing between kernels is used to achieve synchronisation, rather than relying on shared data. The Barrelfish OS has been designed centered around these ideas. Its design is similar to that of a microkernel, in that device drivers are user-level and message-based communication is conducted between processes to achieve protection and isolation. However unlike OKL4 SMP, each core in the machine is treated separately. No data is shared between cores apart from message channels.

This paper is relevant as it shows a structure close to that of a microkernel with high scalability. However similar to Corey, the Barrelfish is an OS built from the ground up with scalability as one of its main goals. It seeks to present and define a new OS paradigm as a way forward in a future of massively multicore systems and does not optimise for the small case of only a few processors.

### 3.8 Microkernel Scalability

Microkernel scalability has also been investigated, with a scalable microkernel implemented with a dynamic locking scheme and dynamic granularity of locking. The kernel was capable of adjusting its locking scheme and granularity safely at run time, based on application feedback. This research was conducted on an earlier incarnation of L4, L4Ka::Pistachio [Uhl05].

The project shows that for very high loads and amounts of processors, fine-grained locking will always scale better. However, with its use of dynamic lock granularity it acknowledges that fine-grained locking can impact performance under low contention. The project itself solves the opposite problem to that which we are trying to solve — it attempts to develop a one size fits all locking scheme that is highly adaptable. For our purposes, we want to establish the trade-offs and scalability limits of different schemes for specific hardware goals. Additionally, the designs were aimed at non-uniform memory access architectures as opposed to SMPs.

## 3.9 Fine-grained Locking

Fine-grained locking has been subject to criticism previously. In a paper discussing the various tradeoffs involved in choosing between remote-memory access and remote invocation for kernel operations, Chaves et. al. [CDL<sup>+</sup>93] make the comment that "the impact of explicit synchronization on local operations is easy to underestimate", after finding that lock acquisition and release accounted for 49% of the total execution time in the absence of contention. The authors recommend a coarser granularity of locking, at the expense of greater potential concurrency. They note that a lock-free system could be used, however they posit that this would not offer any greater performance improvements due to the cost of atomic operations.

### **3.10** Kernel Instrumentation

Perl and Sites [PS96] present an example of using instrumentation to analyse an operating system. The authors used a tool called PatchRX to instrument the execution of Windows NT running some SPEC92 benchmarks and Microsoft SQL Server. They used the traces to investigate how they could speed up uniprocessor Windows NT and how they could get closer to linear scaling for multiprocessor Windows NT.

The instrumentation tool directly modified the operating system to record opcodes, timestamps and memory addresses. For multiprocessor traces, the processor number is also recorded. The log used is a 45 MiB portion of physical memory reserved at boot time. The authors were able to construct patterns of lock acquisition and measure lock contention using these techniques. Similar techniques are employed in this project, however we do not store quite as much information and use less compression.

## 3.11 Summary

Operating systems for SMPs is a widely explored topic, for monolithic operating systems and microkernel operating systems alike. Approaches from locking to applying distributed systems methods to avoiding locks at all by using lock-free data structures are all considered and explored heavily in the existing literature. However most research is focused on systems for a large amount of processors and for more general purpose operating systems. So far, lock-free and wait-free approaches are designed specifically for real-time systems that have only aspirations of running on an SMP system. The research conducted in this thesis applies specifically to systems targeted at a limited amount of processors and designed for tightly-coupled embedded systems. Additionally, previous research has shown that fine-grained locking on larger operating systems can cause significant overhead. Thus it is relevant and offers something new to an already diverse and detailed area.

## Chapter 4

## Approach

The purpose of this project is to evaluate a giant locking scheme and establish how well it scales. Given the very fast system calls of OKL4 and the tightly-coupled nature of the embedded systems it is targeted for, we believe giant locking will be a sufficient locking scheme for a larger scale than has been established on conventional, monolithic operating systems.

To show the distinct trade-offs between giant-locking and finer granularities of locking, we would take an ideal implementation of both methods and contrast their behaviour on a variety of ideal work-loads. However, as we only have access to a giant-locked microvisor, and the implementation of new synchronisation schemes is a non-trivial matter — beyond the scope and time constraints of this project — we need to be slightly more inventive. Additionally, ideal workloads for multiprocessor embedded devices are a substantial research topic in themselves.

Instead, we instrument and benchmark the current locking implementation to investigate its properties and limits. We use simulation to hypothesize about hardware with more processors and a practical coarse-grained locking model. In order to run accurate simulations, we implement a logging system for the microvisor that records the details of every system call that passes through the kernel.

### 4.1 Design

One code design goal of this thesis was the need to be able to produce detailed system traces with minimal impact to the operation of the microvisor. The system traces would then be used as the foundation for detailed analysis into how the giant-locking scheme behaves over 1 - 4 processors. Further, the traces operate as input for a discrete-event simulator that we develop in order to simulate the workloads to run on more processors and to use the workloads as a basis for simulating a finer granularity of locking.

The work done can be divided into three parts:

- **Instrumentation and Logging:** Develop an instrumentation and logging framework with low impact on the microvisor.

- **Workload benchmarking:** Identifying and running workloads to produce detailed system traces for analysis and as a basis for simulation.

- **Simulation:** Develop a simulator that could scale the system traces and model a finer granularity of locking.

## 4.2 Instrumentation and Logging

The goal of this part of the thesis was to be able to produce traces of all application accesses to the microvisor whilst simultaneously measuring various system properties and the length of certain operations. The following features require measuring to allow for detailed analysis:

Current processor: a unique ID of the processor that the current application is running on.

Current application: a unique ID for the current application executing a system call

System call ID: a unique id for the system call being executed.

**System call entry & exit time:** cost of switching between application and microvisor, as well as the system call entry and exit path.

Lock latency: cost added by the lock itself, without any waiting.

Lock-acquisition time: how long a processor waits to acquire the lock.

System call duration: the length of system calls in the microvisor.

Instrumentation overhead: any time added by the instrumentation.

**Contention at time of lock acquisition:** how many processors are currently trying to execute a system call.

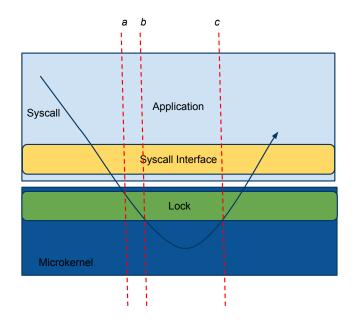

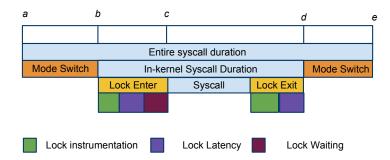

Of these values, lock latency and system call entry & exit cost are measured using separate microbenchmarks. Instrumentation overhead is also measured using micro-benchmarks. In order to measure the times we store timestamps at the points shown in Figure 4.1 and compute the differences.

Note that lock latency can be divided into two parts — lock exit latency and lock entry latency. We assume that lock exit latency is a stable value, changing only due to cache operations. Therefore we do not measure lock latency whilst establishing traces, but run a separate micro-benchmark to determine the cost. This reduces the amount of timestamps that need to be stored.

Base lock-entry latency is also established using a micro-benchmark, as it cannot be distinguished from lock acquisition time during runs without too much interference in the locking code. Any increases in lock-entry latency are then factored in with lock-acquisition time.

Figure 4.1: Points at which the cycle counter will be read.

## 4.3 Workload Benchmarking

The goal of choosing and benchmarking different workloads was to establish the limits of the giantlocking implementation and to generate variety of different traces, with different features, for input to the simulator. We chose to run all of our workloads on guest Linux instances running on the microvisor, as this provides a realistic base for an embedded device OS.

As locking scheme performance is directly related to the number and length of system calls made, we chose a variety of benchmarks that vary the system call rate.

Figure 4.2: The stages of a system call with reference to the instrumentation points shown in Figure 4.1.

Benchmarking is limited by the hardware we have available, which does not have many resources. For instance, whilst the hardware does have an Ethernet port, we can currently only connect one Linux instance to it, so cannot run network-related workloads on multiple Linux instances.

We chose CPU-intensive workloads from SPEC2000 as developed by the *Standard Performance Evaluation Corporation* (SPEC). SPEC have developed a more recent suite of benchmarks, however the platform we were running the tests on only had 256 MiB of RAM, and we needed to be able to run four copies of Linux, each running two copies of the application. 50 MiB of RAM was assigned to the microvisor, as it needs to keep enough kernel stack space for each Linux instance (as well as for the serial server and the time server). This left 50 MiB of RAM for each Linux instance. As a result, we were limited to choosing applications that only required up to 20 MiB of RAM each. This is why we chose our CPU intensive workloads from SPEC2000, not SPEC2006, as even SPEC2006 benchmarks designed to be CPU intensive and not memory intensive required too much RAM.

The different workloads are listed below:

- Lmbench

- 252.eon

- 300.twolf

- A hybrid workload

#### Lmbench

To assess the performance of the giant-locking scheme under a high system call rate, we ran the standard Linux benchmark, Imbench [MS96], as the application for this workload. Lmbench is a

series of micro-benchmarks intended to measure basic operating system and hardware system metrics. We do not present the results of lmbench, as we were using it as a workload for assessing the lock, and not as system evaluation.

#### 300.twolf

To assess the performance of the giant-locking scheme under high CPU utilisation, we chose the SPEC2000v1.3 benchmark, 300.twolf [Swa00]. This benchmark is an implementation of the Timber-WolfSC placement and global routing package that is used in the process of creating the lithography artwork needed for the production of microchips.

#### 252.eon

We ran one other SPEC2000v1.3 benchmark, 252.eon [SCZM99] in order to make sure the results based on the runs of twolf were not particular to that SPEC benchmark. Eon is a C++ implementation of a probabilistic ray tracer.

#### eon-Imbench hybrid

In order to get a workload more system call intensive than the SPEC benchmarks, and less system call intensive than lmbench, we chose to run a workload with lmbench and 252.eon running side-by-side.

## 4.4 Simulation

The goal of this part of the thesis was to be able to vary a variety of features of the system quickly. Building a simulator allowed us to vary:

- Lock latency, to theorise about the impact of different locking implementations on scalability.

- The number of locks in the system, to analyse how our workloads would scale over different locking schemes.

- To make claims based on simulating more processors than we have available in physical hardware.

We chose to implement a *discrete event simulator* using deterministic events produced from our system traces. A discrete event simulator represents a system as a chronological order of events.

The simulator keeps track of a global system time and a list of events for each processor. Events have locks associated with them, and will only be executed by the simulator if that lock is unlocked. Initially we had thought to implement a simulator that would generate random system call events from a distribution, but we decided that this would not properly reflect the characteristics of each workload.

## Chapter 5

## Implementation

The previous chapter went into detail describing the overall design and vision for this thesis project, as well as rationalising design decisions and the relationship between different components of the implementation. In this section, we will dive down into the details of the implementation for each separate component.

## 5.1 Instrumentation & Logging

#### 5.1.1 Log buffer

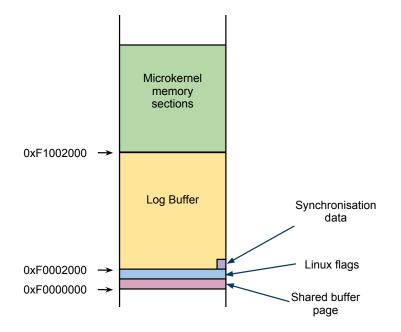

In order to store trace data, we allocated and pre-map a section of the microvisor's virtual memory region, accessible by all users, guest operating systems and the microvisor itself.

The layout of the log buffer can be seen in Figure 5.1. It is divided into four sections; a shared buffer page, a page for Linux flags, a few words of synchronisation data and the log buffer itself.

#### Shared buffer page

The first page is a shared page that is divided up among applications and guest OSs for the microvisor to write instrumentation values from the lock to. Each thread in the microvisor has its own address in the shared buffer to write to. This address is stored in the thread control block (TCB). Initially, for all applications and guests, this address is set to the first part of the shared buffer page. A system call has been implemented to retrieve the address of a unique, five-word section of the buffer. The system call also updates the entry in the respective TCB. By storing this address in the TCB, we avoid adding any expensive branch operations to the lock instrumentation code.

Figure 5.1: Layout of the log buffer and helper pages.

The layout of the values, as the instrumentation code writes them to a section of the shared buffer, is shown in Table 5.1.

| processor ID contention lock | k entry timestamp lock acquire | timestamp lock exit timestamp |

|------------------------------|--------------------------------|-------------------------------|

|------------------------------|--------------------------------|-------------------------------|

Table 5.1: Layout of a per-thread shared buffer as written to by the lock instrumentation code.

#### Log buffer

The log buffer itself is simply a large region of memory that we store all of our traces in. Users interact with the log buffer using the instrumentation library described in Section 5.1.4. After every system call, an instrumentation library function is called to copy values from the shared buffer to a new entry in the log. As the microvisor build system automatically generates the system call interface, the function call is simply added during the code generation stage of the build. Other values that can be read at user time are also inserted into the log at this point, including an application ID that is specified in the XML specification for the application, and the ID of the system call that has just completed executing.

| core id                                                        | application id       | system call id |  | contention value |    |  |

|----------------------------------------------------------------|----------------------|----------------|--|------------------|----|--|

| 0                                                              | 3 14                 |                |  | 24               | 31 |  |

|                                                                | lock entry timestamp |                |  |                  |    |  |

| 0                                                              |                      |                |  |                  | 31 |  |

| lock acquired timestamp delta system call exit timestamp delta |                      |                |  |                  |    |  |

| 0 16                                                           |                      |                |  | 31               |    |  |

The layout of the instrumentation values in one row in the log is shown in Figure 5.2.

Figure 5.2: Layout of data in the 3 words that form an entry in the log buffer.

One might wonder why we do not simply write the values directly into the log from within the lock instrumentation code. We do not do this to avoid adding any extra branching operations to the lock, and also to maintain temporal locality in the addresses accessed by the locking code. Additionally, we would still require more writes to the log in order to record the user-side records. Finally, to save time in the lock we simply write all the values as full words. However our log memory is not endless, so when copying the data out we also compress it.

#### Synchronisation data

Since multiple applications access the log buffer, we require some atomic variables to preserve the integrity of the log. The synchronisation data section includes a one word offset that represents the next available entry in the log. Whenever an application copies data across to the log, the first thing that occus is an atomic increment of this variable.

#### Linux flags

This page is used for flag values for Linux instances to read. These values need to be accessed both during Linux bootstrapping as well as afterwards. Descriptions of the usage of this region can be found in Section 5.1.4.

#### 5.1.2 Lock instrumentation

To minimise the effects of instrumentation on the lock, we narrowed down the values that we would measure in Section 4 and implemented all lock instrumentation in optimised assembly. Recall that we would measure the following: processor ID, contention, a lock entry timestamp, a lock acquire

timestamp and a lock exit timestamp. Lock instrumentation reads these five values and stores them in a five-word, per-thread shared buffer. To read the five values, we instrument the locking code in three different places.

```

#if defined(INSTRUMENTATION_ENABLED)

/* load the current thread struct*/

GET_CURRENT_THREAD_ASM(r12)

/* find contention */

ASM_GET_VADDR_GLOBAL(r9, r11)

ldr r11, [r9, #OFS_GLOBAL_NUM_CPUS_IN_KERNEL]

/* load the shared buffer address into r6 */

ldr r6, [r12, #OFS_THREAD_INSTRUMENTATION_SHARED_BUFFER]

/* Read CPU ID */

mrc p15, 0, r10, c0, c0, 5

/* read lock entry time stamp and store in the buffer*/

MRC p15, 0, r8, c15, c12, 2

/* store contention */

str r11, [r6, #4]

/* store the cpu id */

str r10, [r6, #16]

/* store time stamp*/

str r8, [r6]

#endif

ACQUIRE_GLOBAL_LOCK_SYSCALL

#if defined(INSTRUMENTATION_ENABLED)

/* read lock acquire timestamp */

MRC p15, 0, r11, c15, c12, 2 /* r11 is the lock acquire cycles */

/* store the timestamp */

str r11, [r6, #8]

#endif

```

Figure 5.3: Lock entry instrumentation

#### Before entering the lock

The lock is acquired on the system call execution path using the assembly macro ACQUIRE\_GLOBAL\_LOCK\_SYSCALL. The first instrumentation point is just before this macro is used. At this point we record the core ID, contention value and lock entry timestamp. Each value is trivial to read:

- **Core ID:** the microvisor already stores the ID of the currently executing CPU in one of the ID registers on the coprocessor, so we read it from there and copy the value to the shared buffer.

- **Contention:** a value for how many processors are in the kernel is also maintained by the microvisor at a specific memory address. We simply read from that address.

- **Lock entry timestamp:** We read counter register 0 set to increment every cycle to capture the timestamp.

After reading, we store each value in the same order that they were read, to the shared buffer. The location of the shared buffer is stored in the current thread structure.

#### After acquiring the lock

The second instrumentation point is just after the lock is acquired. At this point, we read just one value:

**Lock acquire time:** We read counter register 0 — set to increment every cycle — to capture the timestamp.

We do not need to recalculate the address of the shared buffer as we store this in r6, which is not clobbered by the locking code. The assembler code for the first two instrumentation points can be seen in Figure 5.3.

```

#if defined(INSTRUMENTATION_ENABLED)

/* read the shared buffer address */

ldr r12, [sp, #OFS_THREAD_INSTRUMENTATION_SHARED_BUFFER]

/* read the exit time */

MRC p15, 0, r8, c15, c12, 2

/* store in the buffer */

str r8, [r12, #12]

#endif

/* lr, r8,r9,r10,r11 will be clobbered */

RELEASE_GLOBAL_LOCK

```

Figure 5.4: Lock exit instrumentation

#### Before releasing the lock

The final place we instrument the lock is just before the lock exit code is executed with the RELEASE\_GLOBAL\_LOCK assembler macro. At this point, we read just one value:

**Lock exit time:** We read counter register 0 — set to increment every cycle — to capture the timestamp.

At this point a full system call has taken place, so we also need to recalculate the address of the shared buffer. The lock exit assembler code can be seen in Figure 5.4

#### 5.1.3 Microvisor system calls

We needed to implement several system calls for the microvisor to aid in benchmarking. Descriptions of each follow.

void \_okl4\_sys\_instrumentation\_n\_cycles(okl4\_word\_t n);

A system call to wait for an amount of time based on n. Our benchmarks did not require exactly n cycles to pass, rather we just needed to spend an varying amount of time in the kernel. As a result this system call does not wait exactly n cycles, but executes a for loop on a volatile variable, counting down from the argument variable

```

void _okl4_sys_null_syscall(void)

```

A system call that does nothing but return to user.

```

void _okl4_sys_instrumentation_zero_counters(void)

```

A system call to zero all of the coprocessor counters (counter 0, counter 1 and the cycle counter) on all running processors. We zero the current processor counter using the PMU (recall Section 2.3, and then send an interrupt to each other processor. When a processor receives that interrupt, they handle it by zeroing their own coprocessor counters.

```

struct _okl4_sys_instrumentation_read_counters_return

_okl4_sys_instrumentation_read_counters(void)

```

A system call to read all of the PMU counters (counter 0, counter 1 and the cycle counter). The return structure is automatically generated according to the OKL4 build system semantics for system calls with multiple return values.

```

okl4_word_t _okl4_sys_instrumentation_read_cycles(void)

```

A system call to read the PMU cycle counter for the current processor.

```

okl4_word_t _okl4_sys_instrumentation_retrieve_shared_buffer(void)

```

This system call allocates a part of the shared buffer page, assigns that section to the currently executing thread and returns the address of the allocated section to the user.

#### 5.1.4 Instrumentation library

We implemented an application level instrumentation library to manage the log buffer. Note that by application level, we mean application level with respect to the microvisor. This means that Linux applications do not have access to the instrumentation library, whilst Linux kernel instances do. As a result, the library contains a set of #ifdefine's to build slightly differently for Linux. In some cases, this simply means redefining printf to be the Linux equivalent printk or assert to be the Linux BUG\_ON macro. However, some functionality changes are required for Linux too. These functionality changes are outlined in the following description of the interface.

Specifically, this library handles copying from the per-application shared buffer into the log buffer. The library maintains an atomic offset that marks the next empty entry in the log buffer.

```

void instrumentation_setUpSharedBuffer(void)

```

This function uses the microvisor system call, \_okl4\_sys\_instrumentation\_retrieve\_shared\_buffer, to set up a shared buffer for the application. It also resets the current offset in the log to zero.

```

void instrumentation_logFromSharedBuffer(int syscallNumber)

```

This function is automatically called from every system call, as it is placed in the auto generated, user-level system call interface. It updates the atomic offset variable to work out which row of the log should be updated. It then writes the system call number, and the values from the shared buffer to the log.

Before performing any of this however, it checks whether a global variable representing the shared buffer has been set up and only logs data if the shared buffer address is not zero. However, the Linux version of this function differs. Instead of checking a global variable, it checks a predetermined address from the top of the log buffer region (see Section 5.1.1). This is due to the fact that Linux makes many system calls whilst starting, at which point any global variables in the instrumentation library may not be mapped in yet. We can fix this by forcing global variables in the instrumentation library into the .init section, however they will then be unmapped when then mappings for the .init section are flushed. In order to get around this whole problem, we simply use a part of our pre-mapped log instead.

```

void instrumentation_reset(void)

```

This function atomically resets the offset into the log buffer to 0.

void instrumentation\_dumpLogToSerial(void)

This is the first of two versions of this function, as both the prototype and behaviour differ wildly if this is a normal application or a Linux instance.

This version of the function simply prints out the contents of the entire log buffer, effectively dumping it to the serial port.

```

unsigned long instrumentation_dumpLogToSerial(unsigned long *addr); (Linux Version)

```

Using the serial port on our platform turned out to be a very slow way of extracting the data. Therefore, the Linux version of this function copies the entire log buffer across to user memory at addr, using Linux copy-out semantics. The user can then extract the buffer in anyway they desire. In our case, we connected to Linux via telnet over an ethernet port, used this function to copy the log buffer over, and then printed the buffer out on the telnet terminal.

#### 5.1.5 Linux system calls

Linux applications do not have access to system calls provided by the microvisor. As mentioned previously, only Linux kernel instances have access to the instrumentation library. As a result, we needed to implement system calls to perform either of these functions. The following describes each system call we implemented and used.

```

void sys_zero_counters(void)

```

This system call delegates to the microvisor, calling \_okl4\_sys\_instrumentation\_zero\_counters.

unsigned long sys\_read\_cycle\_counter(void)

This system call delegates to the microvisor, calling \_okl4\_sys\_instrumentation\_read\_cycles.

void sys\_register\_shared\_buffer(void)

This system call delegates to the instrumentation library, calling instrumentation\_setUpSharedBuffer. unsigned long sys\_dump\_buffer(unsigned long \*addr)

This system call delegates to the instrumentation library, calling instrumentation\_dumpLogToSerial.

### 5.1.6 Limitations of the logging implementation

One important part of the OKL4 microvisor lock implementation is that the Linux instances, serial server and timer server are not constantly on the same physical processor, and may change processor while waiting on the giant lock. Due to this fact, the lock timestamps are not completely precise. Consider the following situation:

- 1. a vCPU enters the lock on physical CPU 1.

- 2. The lock instrumentation records a lock entry timestamp using the cycle counter for CPU 1.

- 3. Whilst waiting on the lock, the vCPU is migrated to CPU 2.

- 4. After executing acquiring the lock and executing the system call, the vCPU reads the cycle counter on CPU 2.

The result is that the delta values we store for lock acquisition time and system call duration are occasionally read from different CPU cycle counters. Since the cycle counters are all zeroed at approximately the same time, the values should not be more than a few cycles out.

This problem could be solved by using the global cycle counter available on the snoop control unit (SCU), however this would increase the impact of lock instrumentation.

# 5.2 Simulator

As discussed in the previous chapter, in order to model coarse grained locking, scalability for over four processors, and to vary the lock latency, we have implemented a discrete event simulator. The simulator is designed to replay the traces recorded using the logging system.

The simulator is implemented in Java, in order to harness Java's convenient BigInteger library and benefit from the associated development speed improvements that come with using a higher level language.

#### 5.2.1 Implementation

The simulator operates on a processor abstraction, mapping all of the events from one real processor to multiple simulated processors.

Initial simulations were based on assigning application IDs to each processor to duplicate, to reliably add more workloads and to avoid increasing the system calls added to the logs by the timerserver and serial server. However, as timer-server and serial-server events would also increase with more Linux instances, we found that by mapping simulated processors to real processors a more realistic simulation was achieved.

The simulator has two stages: queue-building and simulation. Additionally, the simulator is configured by a configuration in JavaScript object notation (JSON) format, which is easily serialisable to Java objects.

#### Queue-building

In the queue-building stage, the simulator builds the event queues for each simulated processor from the input log file. One row from the log is given to a simulated processor if the following is true:

*simulated\_processor\_id* mod *num\_actual\_cores* == *actual\_processor\_id*

For each row from the log, we add a chain of events to each applicable simulated processor queue. Events are given a duration in cycles. The exact events for each row are added according to the *system call scheme*. A system call scheme simply refers to the events that are added for each system call. We implement two different system call schemes; a giant-locked scheme and a coarse-locked scheme. The duration of each event type comes from different sources. An idle event is also added at the start for each processor, with the duration being the first event for that processor, minus the first log row timestamp.

| A | lgori | thm | 1 Idl | le time | calcu | lation |

|---|-------|-----|-------|---------|-------|--------|

|---|-------|-----|-------|---------|-------|--------|

$prevLockExit \leftarrow prevLockEntryTimestamp + prevSyscallDuration + prevLockAcquire$  $idleDuration \leftarrow lockEntryTimestamp - prevLockExit$

#### Giant-locked system call scheme

The chain of events that is added to a simulated processor queue for each row is presented in Table 5.2. The same event chain is added for each row in the log, regardless of the system call number.

| Event name  | Duration source                                           |  |

|-------------|-----------------------------------------------------------|--|

| Mode switch | Configurable                                              |  |

| Lock entry  | Configurable                                              |  |

| System call | Duration is taken from the trace file                     |  |

| Lock exit   | Configurable or taken from a hard-coded distribution, its |  |

|             | generation is described in Section 6.1.5                  |  |

| Mode switch | Configurable                                              |  |

| Idle        | Calculated from the log - see Algorithm 1.                |  |

Table 5.2: Events generated for a row in a trace file for a giant-locked system call scheme.

#### **Coarse-grained system call scheme**

The coarse-grained system call scheme is more complicated than the giant-locked scheme as we use several different locks and exclude some system calls from locking at all. System calls are divided into two different categories: locked system calls and unlocked system calls. Table 5.3 shows the events added for a trace file for unlocked system calls.

| Event name  | Duration source                            |

|-------------|--------------------------------------------|

| Mode switch | Configurable                               |

| System call | Duration is taken from the trace file      |

| Mode switch | Configurable                               |

| Idle        | Calculated from the log - see Algorithm 1. |

Table 5.3: Events generated for a row in a trace file for an unlocked system call in a coarse-grained system call scheme.

Locked system calls generate many more events. To model coarse grained locking, we add multiple locks and divide up the system call duration into several parts. A sample set of events generated is shown in Table 5.4. Further detail of the exact coarse-grained locking model used is described later in Section 6.4.4.

#### Simulation

Following the queue building phase, the simulator starts the actual simulation. The simulator keeps track of a list of current events — one for each processor that has not yet finished. For every pass of the simulator, we choose the event that will finish soonest. An event is only executable if it is not blocked by a lock. We then subtract the duration of that event from every other executable event in the

| Event Name  | Duration source                                           |

|-------------|-----------------------------------------------------------|

| Mode switch | Configurable                                              |

| Lock entry  | Configurable                                              |

| System call | x% of duration taken from the trace file                  |

| Lock exit   | Configurable or taken from a hard-coded distribution, its |

|             | generation is described in Section 6.1.5                  |

| System call | y% of duration taken from the trace file                  |

| Lock entry  | Configurable                                              |

| System call | z% of duration taken from the trace file                  |