**UNSW**

AUSTRALIA

**School of Computer Science and Engineering**

**Faculty of Engineering**

**The University of New South Wales**

# **A Usable System Model for Time Protection**

by

**Varun Sethu**

Thesis submitted as a requirement for the degree of

Bachelor of Engineering in Computer Engineering

Submitted: November 2025

Supervisor: Prof. Gernot Heiser & Dr Rob Sison

Student ID: z5362311

# Abstract

This thesis explores how the current system model for time protection on seL4 can be extended to support cross-domain communication. To achieve this, it proposes and evaluates a design for cross-domain notifications and also proposes a design for cross-domain shared memory. Additionally, this thesis argues that a more efficient implementation of cross-domain shared memory is not presently achievable on the evaluation platform. Doing so would require introducing new hardware features or reworking the current time-protection implementation to adopt alternative LLC-partitioning schemes.

# Acknowledgments

I would firstly like to thank *Professor Gernot Heiser* and *Dr Rob Sison* for their invaluable guidance and supervision during this project. It has been an absolute blessing and really helped me stay on focus.

I would also like to thank *Julia Vassiliki* and *Nils Wistoff*. Their support was absolutely critical, as much of the work achieved during this thesis would have been practically impossible without them. I would like to thank Julia for all her work in setting up the remote Cheshire infrastructure and porting time protection to Cheshire, as well as for the help she provided when I was debugging finicky timing channels or dealing with arcane hardware issues I had never encountered before. I am also grateful for her patience in answering my many questions and guiding me through any problems I faced with tooling. I would like to thank Nils for answering all the random questions I had about Cheshire, despite being half-way across the world and busy with his PhD thesis.

I would like to thank *Lesley Rossouw*, *Sai Nair* and *Charran Kethees* for their discussions throughout the year about their honours work. Particularly Lesley, who has been an invaluable source of advice and guidance, acting as a sort of informal buddy at TS.

And finally, I would like to thank my friends and family, namely *Shaji*, *Bindu*, *Tarun* and *Prashansa* for all their support during what has been quite an intense year.

# Abbreviations

**CPU** Central Processing Unit

**TLB** Translation Lookaside Buffer

**MMU** Memory Management Unit

**LLC** Last Level Cache

**OS** Operating System

**DPLLC** Dynamically Partitionable Last Level Cache

**WCET** Worst-Case Execution Time

# Contents

|          |                                                  |          |

|----------|--------------------------------------------------|----------|

| <b>1</b> | <b>Introduction</b>                              | <b>1</b> |

| 1.1      | Covert Channels and Side Channels . . . . .      | 2        |

| 1.2      | seL4 and Time Protection . . . . .               | 2        |

| 1.3      | Extending the Model of Time Protection . . . . . | 3        |

| 1.3.1    | Shared memory . . . . .                          | 4        |

| 1.3.2    | Notifications . . . . .                          | 4        |

| 1.4      | Thesis Problem Statement and Outline . . . . .   | 4        |

| <b>2</b> | <b>Background</b>                                | <b>6</b> |

| 2.1      | Caches and Their Architecture . . . . .          | 6        |

| 2.1.1    | Address decomposition . . . . .                  | 6        |

| 2.1.2    | Cache architectures . . . . .                    | 7        |

| 2.1.3    | Cache colouring . . . . .                        | 8        |

| 2.1.4    | Cache hierarchy . . . . .                        | 9        |

| 2.2      | Timing Channels . . . . .                        | 10       |

| 2.2.1    | Flush + Reload . . . . .                         | 11       |

| 2.2.2    | Prime + Probe . . . . .                          | 11       |

| 2.3      | seL4 Background . . . . .                        | 12       |

| 2.3.1    | Capabilities . . . . .                           | 12       |

|          |                                             |           |

|----------|---------------------------------------------|-----------|

| 2.3.2    | Threads                                     | 13        |

| 2.3.3    | Virtual memory management                   | 13        |

| 2.3.4    | Notifications                               | 14        |

| 2.3.5    | Endpoints and IPC                           | 16        |

| 2.3.6    | IRQs                                        | 16        |

| 2.3.7    | Domains                                     | 16        |

| 2.4      | Cheshire                                    | 17        |

| 2.4.1    | LLC                                         | 17        |

| 2.4.2    | Microarchitectural flush                    | 18        |

| 2.4.3    | OpenSBI                                     | 18        |

| 2.5      | Time Protection in seL4                     | 18        |

| 2.5.1    | Requirement 1 for Time Protection           | 19        |

| 2.5.2    | Requirements 2 & 3 for Time Protection      | 20        |

| 2.5.3    | Requirement 4 for Time Protection           | 20        |

| 2.5.4    | Requirement 5 for Time Protection           | 21        |

| 2.5.5    | Time Protection on RISC-V                   | 21        |

| 2.5.6    | The domain switch on RISC-V                 | 22        |

| 2.6      | Time Protection in seL4 — Taking It Further | 23        |

| <b>3</b> | <b>Related Work</b>                         | <b>24</b> |

| 3.1      | Constant Time Programming                   | 24        |

| 3.2      | Pre-fetching and Forced Determinism         | 25        |

| 3.3      | Noise Injection                             | 26        |

| 3.4      | Time-Padding                                | 27        |

| 3.5      | Cache Partitioning                          | 28        |

| 3.5.1    | CATalyst                                    | 28        |

|          |                                                  |           |

|----------|--------------------------------------------------|-----------|

| 3.5.2    | SecDCP . . . . .                                 | 29        |

| 3.5.3    | Cheshire's dynamically partitioned LLC . . . . . | 29        |

| 3.5.4    | ARM MPAM . . . . .                               | 30        |

| 3.6      | Speculation Barriers . . . . .                   | 31        |

| 3.7      | Cross-Domain Notifications . . . . .             | 31        |

| 3.8      | Channel Benchmarking . . . . .                   | 32        |

| 3.9      | Summary . . . . .                                | 34        |

| <b>4</b> | <b>Benchmarking Methodology</b>                  | <b>35</b> |

| 4.1      | Quantifying Leakage . . . . .                    | 35        |

| 4.2      | Channel Matrices . . . . .                       | 35        |

| 4.3      | Benchmarking Environment . . . . .               | 36        |

| <b>5</b> | <b>Notification Design</b>                       | <b>37</b> |

| 5.1      | The Problem of Multiple Signals . . . . .        | 38        |

| 5.1.1    | $N$ signals awakens $N$ threads . . . . .        | 39        |

| 5.1.2    | $N$ signals awakens 1 thread . . . . .           | 40        |

| 5.2      | Notification Design and API . . . . .            | 40        |

| 5.2.1    | Signalling . . . . .                             | 40        |

| 5.2.2    | Waiting . . . . .                                | 41        |

| 5.2.3    | Polling . . . . .                                | 41        |

| 5.2.4    | Domain association . . . . .                     | 41        |

| 5.2.5    | API as a state machine . . . . .                 | 41        |

| 5.3      | Information Flow Requirements . . . . .          | 43        |

| 5.4      | Summary . . . . .                                | 44        |

|                                                   |           |

|---------------------------------------------------|-----------|

| <b>6 Notification Implementation</b>              | <b>45</b> |

| 6.1 General Implementation Details . . . . .      | 45        |

| 6.2 Signal Implementation . . . . .               | 45        |

| 6.3 Time-Padding . . . . .                        | 46        |

| 6.3.1 Solution 1 — Hardware support . . . . .     | 49        |

| 6.3.2 Solution 2 — Noise injection . . . . .      | 49        |

| 6.3.3 Solution 3 — Error correction . . . . .     | 52        |

| 6.3.4 Bounding the WCET . . . . .                 | 54        |

| 6.3.5 Evaluation and discussion . . . . .         | 54        |

| 6.4 Wait Implementation . . . . .                 | 55        |

| 6.5 Domain Switch Delivery . . . . .              | 56        |

| <b>7 Notification Evaluation &amp; Discussion</b> | <b>57</b> |

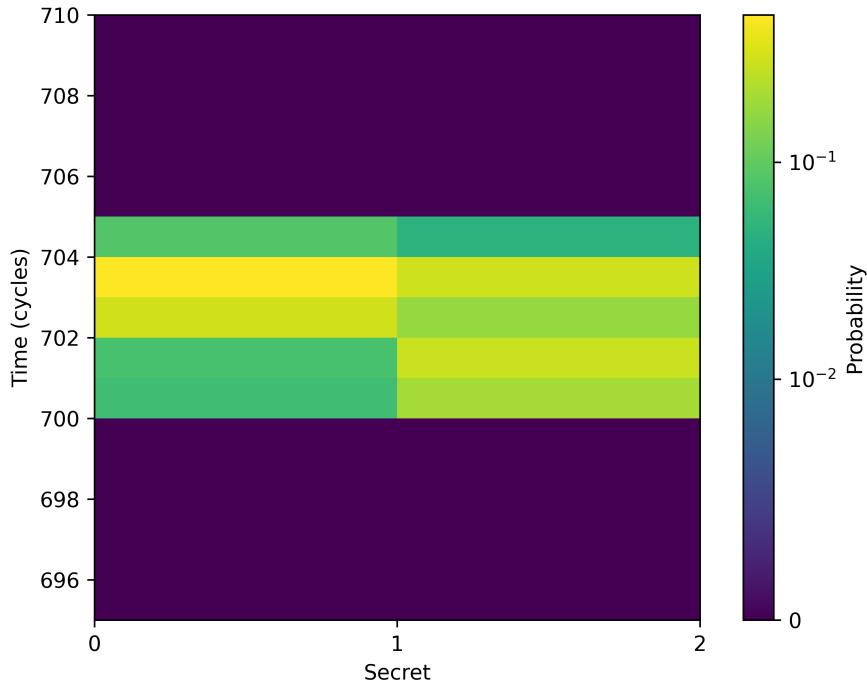

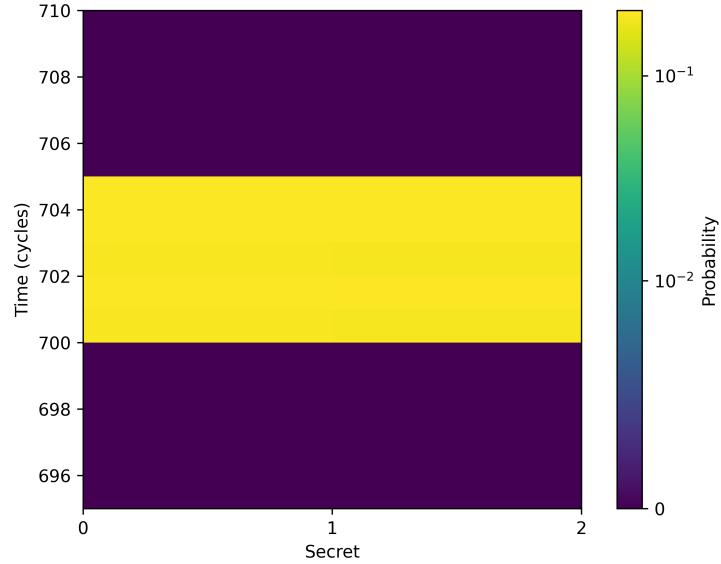

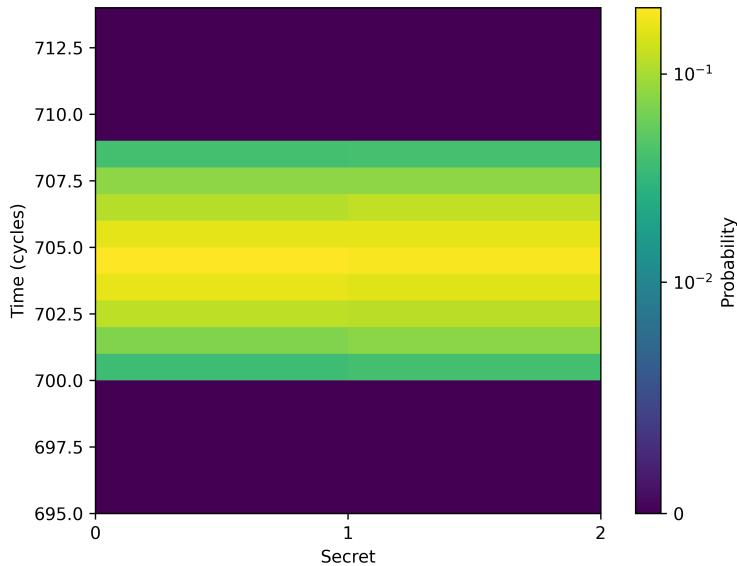

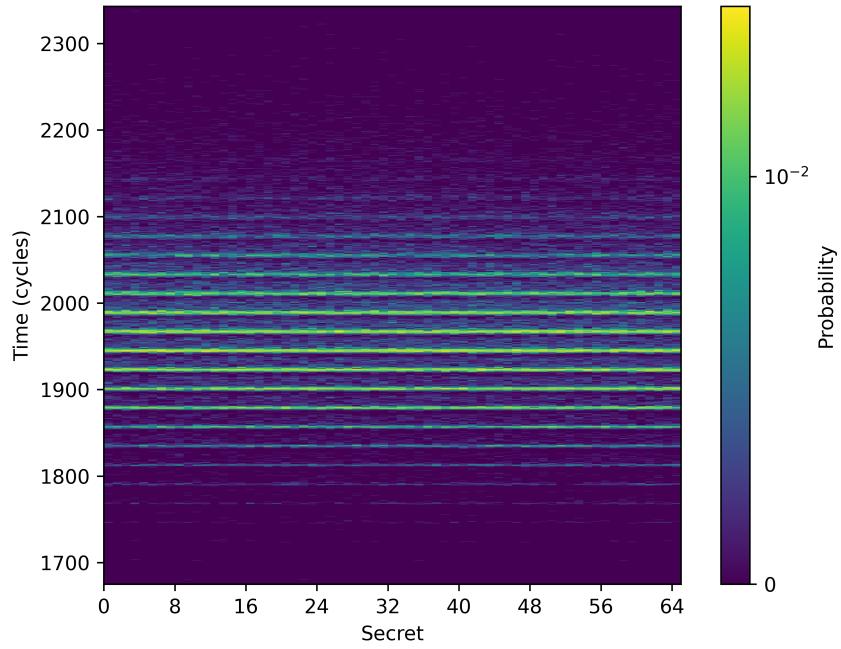

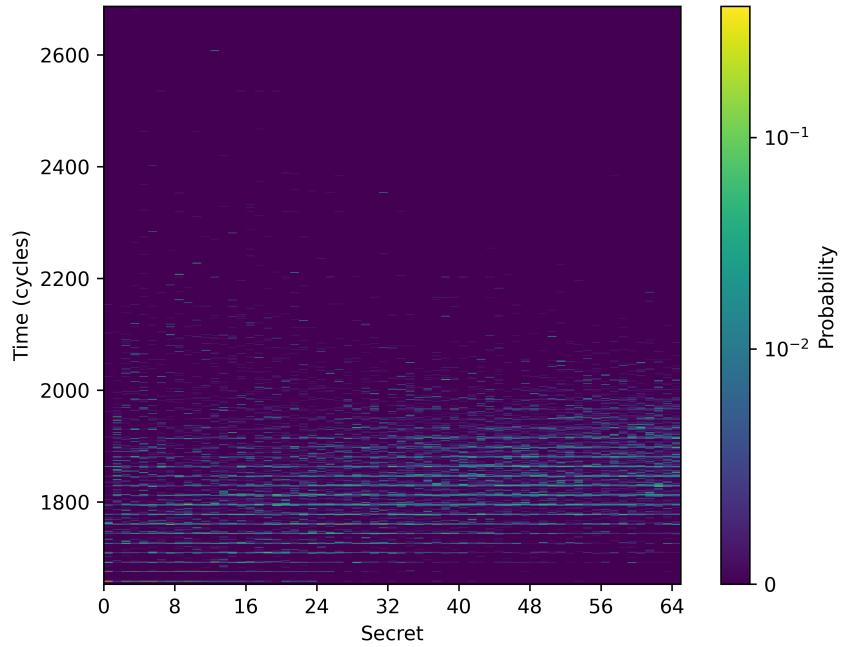

| 7.1 Timing Channel Benchmarks . . . . .           | 57        |

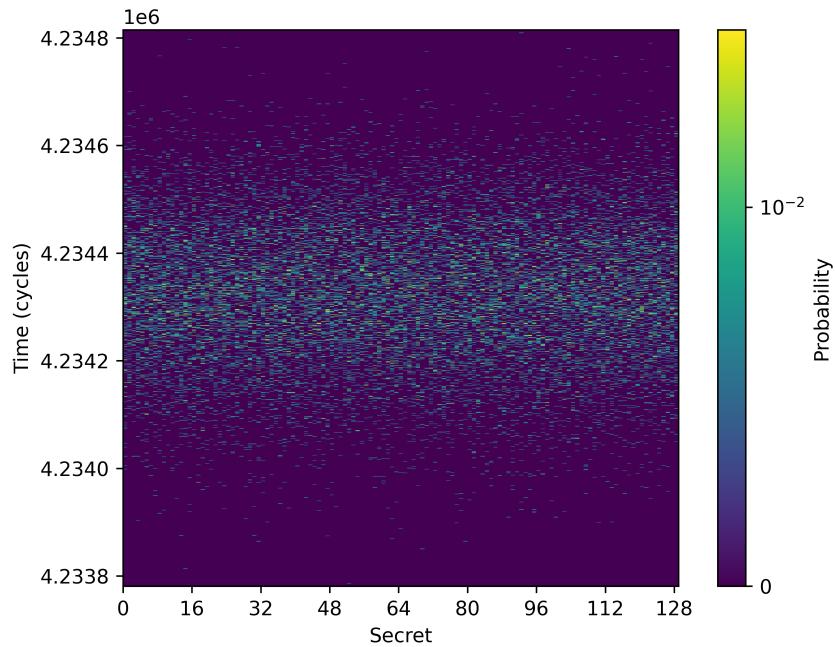

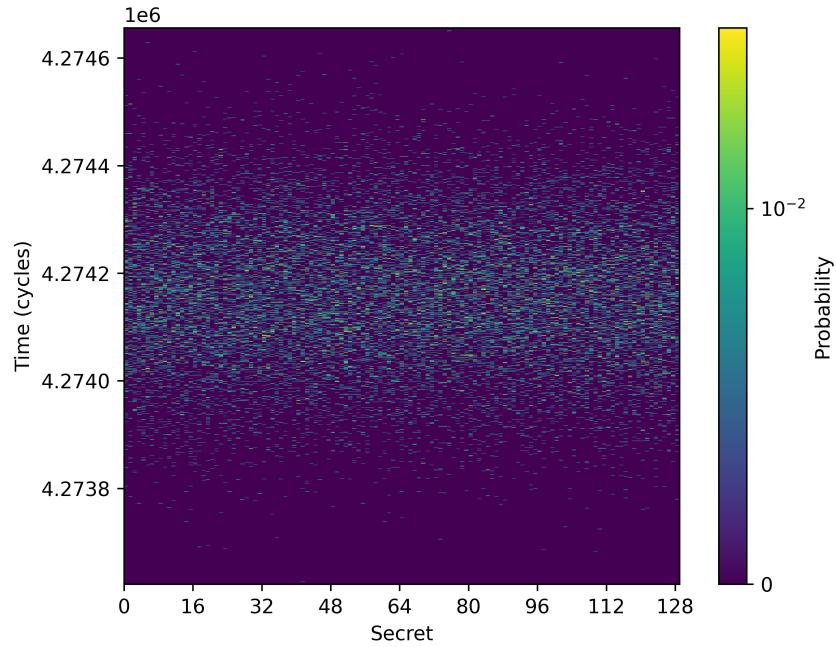

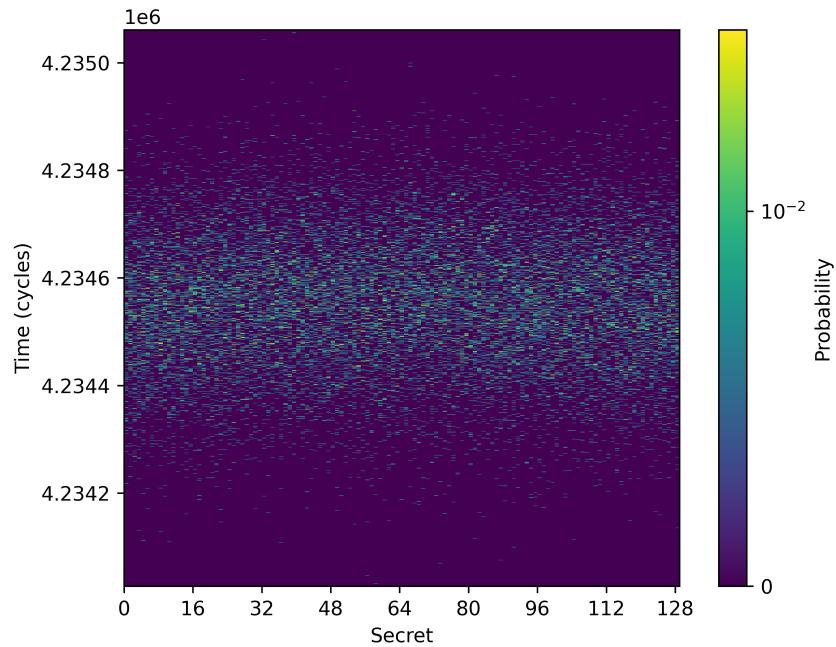

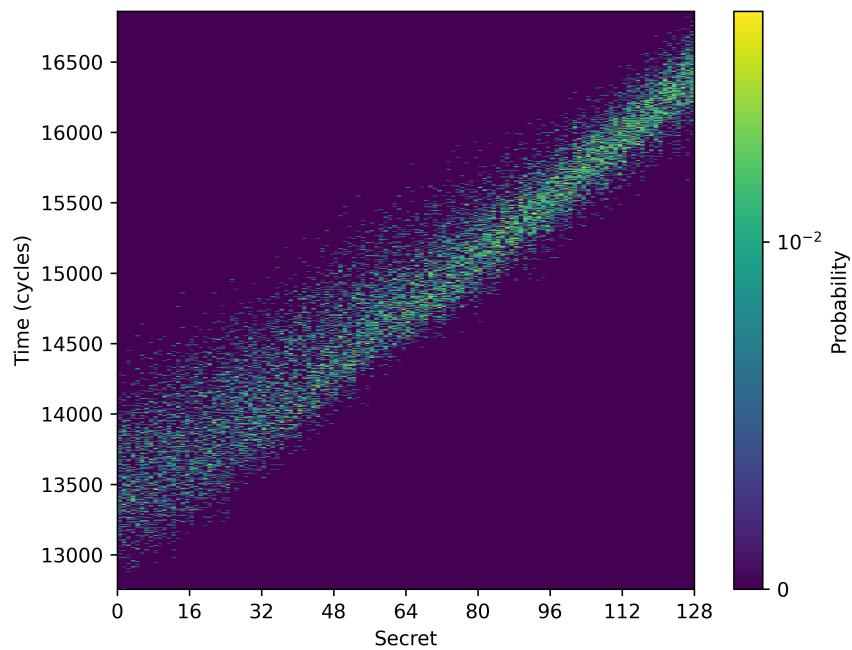

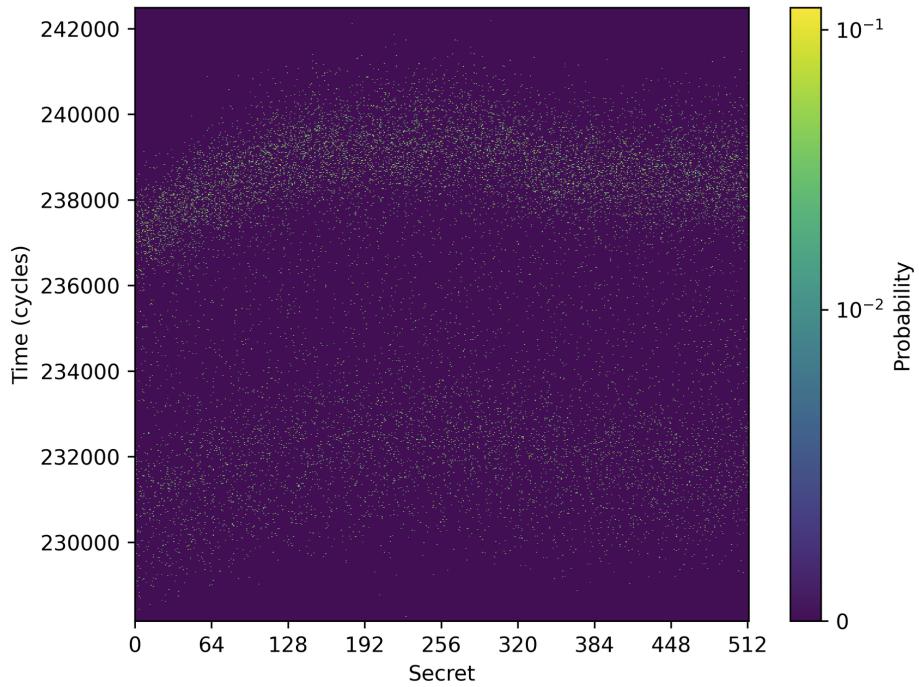

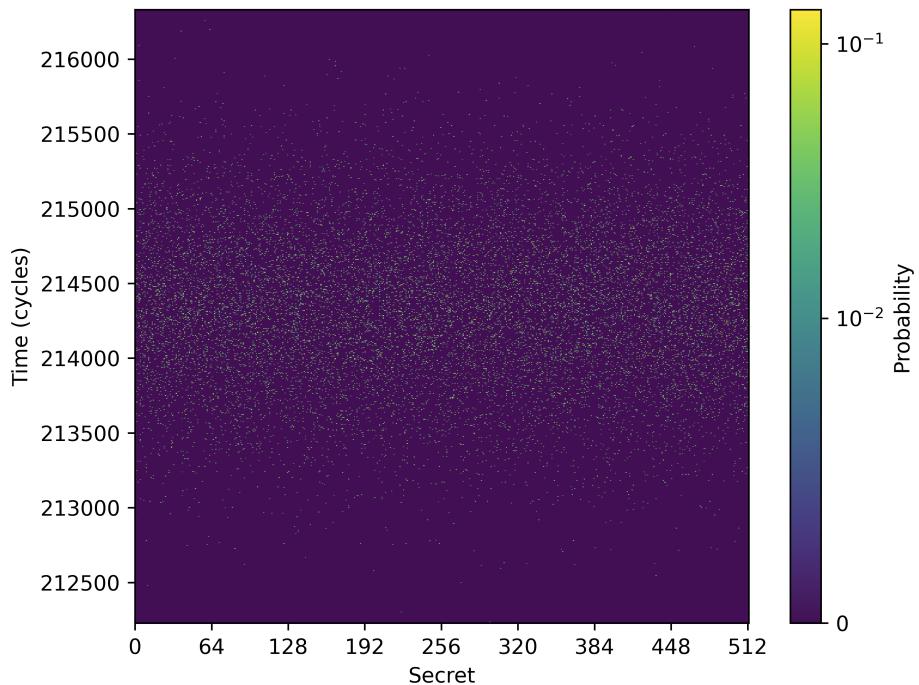

| 7.1.1 Unrelated information flow . . . . .        | 58        |

| 7.1.2 Backflow channel . . . . .                  | 62        |

| 7.1.3 Readiness channels . . . . .                | 63        |

| 7.1.4 Summary . . . . .                           | 66        |

| 7.2 Performance . . . . .                         | 70        |

| 7.2.1 Signal latency . . . . .                    | 70        |

| 7.2.2 Poll latency . . . . .                      | 71        |

| 7.2.3 Domain switch overhead . . . . .            | 71        |

| 7.3 Discussion . . . . .                          | 73        |

| 7.4 Further Work . . . . .                        | 73        |

|                                                             |           |

|-------------------------------------------------------------|-----------|

| <b>8 Shared Memory Design</b>                               | <b>75</b> |

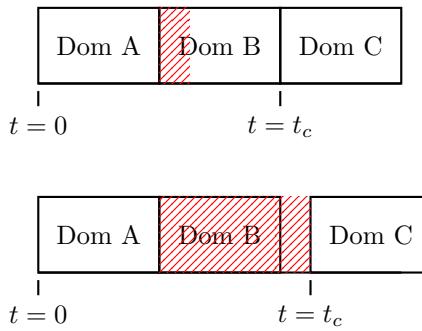

| 8.1 Determinisation on Domain Switch . . . . .              | 76        |

| 8.1.1 Cache inclusivity . . . . .                           | 76        |

| 8.1.2 Pre-fetching and a common colour . . . . .            | 77        |

| 8.1.3 Pre-fetching and a distinct colour . . . . .          | 80        |

| 8.1.4 Summary . . . . .                                     | 88        |

| 8.2 Copy-on-Domain-Switch . . . . .                         | 89        |

| 8.2.1 Copy performed by the kernel . . . . .                | 89        |

| 8.2.2 Copy performed by a trusted thread . . . . .          | 89        |

| 8.2.3 Which to implement? . . . . .                         | 91        |

| <b>9 Shared Memory Implementation</b>                       | <b>92</b> |

| 9.1 Kernel Approach . . . . .                               | 92        |

| 9.1.1 Domain and frame association . . . . .                | 92        |

| 9.1.2 Domain switch operations . . . . .                    | 93        |

| 9.2 User-Level Approach . . . . .                           | 94        |

| 9.2.1 Constant time-padding and bounding the WCET . . . . . | 94        |

| <b>10 Shared Memory Evaluation &amp; Discussion</b>         | <b>95</b> |

| 10.1 Timing Channel Benchmarks . . . . .                    | 95        |

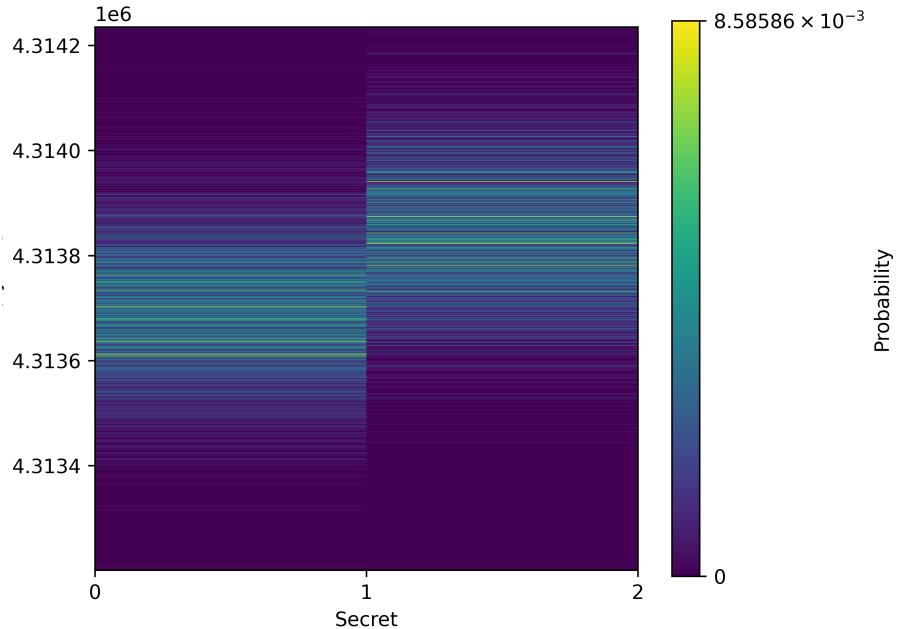

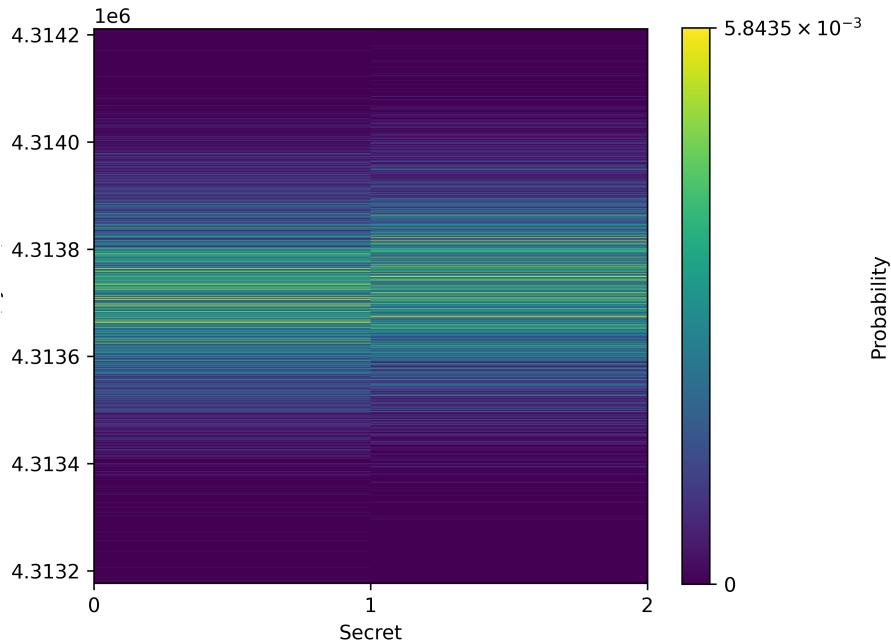

| 10.1.1 Direct reads/writes benchmark . . . . .              | 96        |

| 10.1.2 Copy latency benchmark . . . . .                     | 100       |

| 10.1.3 Unrelated activity benchmark . . . . .               | 105       |

| 10.1.4 Summary . . . . .                                    | 105       |

| 10.2 Performance . . . . .                                  | 108       |

| 10.3 Discussion . . . . .                                   | 110       |

| 10.4 Further Work . . . . .                                 | 110       |

|                                               |            |

|-----------------------------------------------|------------|

| <b>11 Conclusion</b>                          | <b>112</b> |

| 11.1 Notifications . . . . .                  | 112        |

| 11.2 Shared Memory . . . . .                  | 113        |

| <b>Appendix A — Proof of Noise Uniformity</b> | <b>114</b> |

| <b>Appendix B — Existing Timing Channels</b>  | <b>116</b> |

| B.1 VGA Controller Contention . . . . .       | 116        |

| B.2 Timer Drift Channel . . . . .             | 118        |

| B.3 Scheduler Data Channel . . . . .          | 119        |

| <b>Bibliography</b>                           | <b>121</b> |

## Chapter 1

# Introduction

As the global demand for computing grew, CPU manufacturers needed to come up with more innovative architectures and designs to improve the performance of their chips. To achieve this, manufacturers decoupled the interface from implementation to produce an *instruction set architecture* (ISA). The ISA acted as an API for the CPU, allowing manufacturers to scale the complexity of their implementation (known as the *microarchitecture*) without affecting existing software targeting the CPU. Over the years, several features have been introduced to improve the performance of CPUs, with two very specific examples being *caches* and *speculative execution*. Caches aim to reduce the cost of accessing main memory, acting as a temporary storage of data that was previously accessed by the CPU. The idea being that if a program had accessed a piece of data before, it was likely to access it again. Speculative execution, on the other hand, allowed the CPU to begin executing instructions for a branch point in a program that had not yet been taken, greatly speeding up many programs. There have been several other advancements in CPU design, all of which enable hardware to present a consistent interface to software while still achieving significant performance gains.

As CPU design progressed, there were warnings that the increasing complexity of the microarchitecture could be exploited by bad actors [Ge et al., 2017]. Many such warnings were ignored until 2018, when the Spectre [Kocher et al., 2019] and Meltdown [Lipp et al., 2018] attacks were introduced. These attacks relied on vulnerabilities around speculative execution's impact on caches, which unknowingly allowed attackers to read data that the *operating system* (OS) would otherwise not permit. At their core, these attacks stem from the increasing complexity of microarchitectures, which forced CPUs to manage more intricate interactions and the lasting effects these interactions had on the internal *microarchitectural state*. Kocher et al. [2019] exploited this complexity and discovered a mishandling of caches during speculative execution, where speculatively executed instructions left erroneous measurable traces in the CPU cache. Since the cache is shared between multiple threads and never reset, attacking processes could observe sensitive information that they should not have access to via these erroneous cache impacts.

## 1.1 Covert Channels and Side Channels

Secure systems maintain restrictions on which subcomponents can communicate with each other. However, when these rules are broken, and a method of communication opens up that does not use a legitimate or intended communication path, then the system maintains a *covert channel*. In contrast, *side channels* refer to the unintentional leakage of information within a system. Unlike covert channels, which require two parties to actively communicate, side channels allow an attacking process to gain information about a victim process without the victim’s knowledge.

Spectre and Meltdown demonstrated how channels can be used to leak information in a manner disallowed by a system’s security policy, specifically how *microarchitectural timing channels* can be used to achieve this goal. Microarchitectural timing channels exploit variations in program execution time – caused by microarchitectural state – to encode and transmit information. For example, if a CPU stores a piece of memory within its cache, subsequent accesses to that memory will be significantly faster. Two processes can exploit this behaviour to communicate via a shared, read-only memory buffer: one process accesses the first byte of the buffer to load it into the cache, while the other measures its access time for the same byte. A fast access may indicate a “1”, while a slow access may indicate a “0” – successfully sending information over a buffer that neither process has permission to write to.

Covert/side channels can be created through any mismanaged shared resource, and the increasing complexity of microarchitectures has provided fertile ground for the introduction of additional mismanaged resources. To address these issues, Ge et al. [2019] introduces *time protection* – a set of OS-level mechanisms aimed at preventing the creation of timing channels on increasingly complex microarchitectures. The authors demonstrate how these mechanisms can be applied to prevent timing channels within systems built on top of seL4.

## 1.2 seL4 and Time Protection

Microarchitectural timing channels exploit shared resources to transmit information that would otherwise be restricted by a system’s security policy. Therefore, any method aimed at eliminating timing channels must implement mechanisms to partition resources and restrict sharing. In the context of time protection, there are two primary methods for resource partitioning: *spatial partitioning*, which involves dividing state into non-overlapping regions, and *temporal partitioning*, which involves dividing shared resources across time [Ge et al., 2019]. While most microarchitectural state can only be partitioned temporally, certain components, such as the *last-level cache* (LLC), can also be partitioned spatially.

seL4 is a *microkernel* with security being a core pillar of its design, guaranteed by a small *trusted compute base* and thorough *formal verification* [Klein et al., 2009, 2014]. Significant engineering work has already gone into extending the kernel to support time-protection. The current system model for time protection in seL4 revolves around the idea of *domains*,

which are a collection of software components and processes that represent a single unit in a system’s security policy. Domains were initially introduced by Murray et al. [2013] to prevent leakage of information through scheduling decisions, but Ge et al. [2019] later extended them to prevent leakage via timing channels. seL4 identifies a few key shared resources that must be partitioned between these domains to achieve time protection:

1. Microarchitectural state that supports spatial partitioning (such as the LLC).

2. Microarchitectural state that does not support spatial partitioning (such as TLBs).

3. Interrupts.

4. The operating system kernel itself.

To spatially partition resources between domains, the model assigns each domain a specific region of the resource and ensures it can access only that region, preventing any observation or interference from others. Temporal partitioning is achieved by assigning domains a fixed *time slice*; at the end of a domain’s time slice, all resources that cannot be spatially partitioned are reset and flushed, preparing them for the next domain [Ge et al., 2019]. Since the kernel itself is a shared resource and difficult to partition, seL4 provides each domain with its own dedicated copy of the kernel, where each kernel copy maintains a unique text segment, stack, and global data segment [Ge et al., 2019].

While powerful, the model does not provide any mechanism for safe communication across domains, making it impractical for many real-world use cases. A natural next step in the development of this model is to introduce mechanisms that allow controlled communication between domains.

### 1.3 Extending the Model of Time Protection

All useful systems require the ability for subcomponents within the system to communicate. For a system built around traditional seL4, communication between threads of execution is achieved through *shared memory* and coordinated via an asynchronous signalling mechanism known as *notifications*. Unfortunately, as outlined earlier, systems built on top of time-protected seL4 have no similar mechanisms for communicating. Using the traditional methods directly would completely violate the time-protection guarantees that the time-protected kernel aims to provide.

As such, it then becomes natural for us to explore extending the existing model of time protection in seL4 to support communication. More specifically, explore how to introduce notifications and shared memory across temporally isolated domains. All communication primitives discussed in the remainder of this thesis involve a writer/sender domain and a reader/receiver domain, and are one-way. Information flows exclusively from the writer to the reader domain, and we take deliberate measures to ensure that no back channel exists from the reader to the writer. We will ensure that our designs prevent leaking information that the writer/sender did not intend on sending through the communication primitive.

### 1.3.1 Shared memory

A key design pillar of seL4 is the user-level management of memory, which allows user-level threads to share buffers of memory by mapping physical frames into multiple address spaces. This makes shared memory a simple way to achieve communication in seL4, and a technique that many applications will use to communicate large amounts of data quickly. Given this, it makes sense to explore introducing shared memory as a cross-domain communication mechanism within time-protected seL4. Extending the current system model to support shared memory is not straightforward. Simply mapping the buffer into each domain would violate the security guarantees the current model of time protection provides, as it would require domains to share portions of the LLC — something the model strictly prohibits. Additionally, special measures must be taken to prevent the introduction of a back channel from the reader to the writer.

### 1.3.2 Notifications

Notifications in seL4 act as *semaphores*, enabling threads to wait (block until a signal is received) and also signal (unblock the first thread that waited on the notification). Any model of communication using shared memory must also maintain a mechanism for coordinating access to this shared memory, which is precisely the problem notifications solve. It then becomes natural for us to attempt to generalise notifications such that they can be used across domains. Like shared memory, cross-domain notifications are not an easy feat. They are essentially a problem of coordinating communication across distinct copies of the kernel while still maintaining time protection and not introducing any back channels.

## 1.4 Thesis Problem Statement and Outline

Well-defined communication mechanisms between domains are essential for any system built on time-protected seL4. As such, this thesis will explore extending time-protection to enable strict one-way cross-domain shared memory and notifications. The proposed communication primitives are designed to prevent the leakage of information beyond what is explicitly conveyed through these primitives.

We will explore these primitives over several chapters. Chapter 5 and Chapter 6 will outline the design and implementation of a new cross-domain notification object, enabling threads in distinct domains to signal each other without leaking any additional information. Chapter 7 will then evaluate the presented design by conducting various *timing channel benchmarks*, demonstrating that no information, except signals, can flow between domains.

Chapter 8 will explore possible designs for cross-domain shared memory. It will argue that there is only one presently viable software-only method for implementing cross-domain

shared memory. The alternative method will require reworking the present implementation of time-protection on our target platform rather substantially. Chapter 8 will also demonstrate how the proposed design for cross-domain shared memory can be implemented without extending the kernel any further, only requiring a working implementation of cross-domain notifications. Chapter 9 will then discuss the implementation details of the presented designs. Finally, Chapter 10 will evaluate the presented design and implementation of cross-domain shared memory. It will demonstrate that no information can leak through shared memory buffers outside what is explicitly written to them. Our exploration of cross-domain shared memory will then conclude with a motivation for future work. Arguing that a more efficient implementation of cross-domain shared memory will require reworking the present implementation of time protection on our target platform slightly – particularly, the LLC partitioning mechanism that it employs.

## Chapter 2

# Background

Before continuing any further, we must first examine some key ideas and terminology that underpin this thesis.

### 2.1 Caches and Their Architecture

Caches are the key example of microarchitectural state within essentially all modern CPUs. They exist to mitigate the fact that accesses to main memory are significantly slower than CPU operations, aiming to speed up subsequent memory accesses by storing previously used data. At a high level, caches rely on two key principles: *temporal locality*, the idea that recently accessed data is likely to be accessed again; and *spatial locality*, the tendency for programs to access memory locations close to those previously used. When reading from main memory, a CPU will initially check the cache for the data being requested, and if present, will read it directly from the cache. If the requested address is not present, the CPU will read an entire cache line (typically 32 – 64 bytes) containing the target address from main memory and store the result within the cache. Reading an entire *cache line* instead of individual bytes allows the processor to exploit spatial locality, as subsequent requests for nearby addresses can be immediately serviced by the cache.

#### 2.1.1 Address decomposition

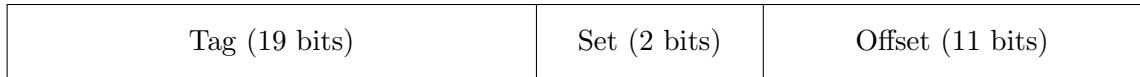

To understand how an address is decomposed and used to index a specific entry in a cache, we will consider a hypothetical 32-bit machine. On this machine, a cache line will consist of 2048 bytes; therefore, we require  $\log_2(2048)$ , or 11 bits to index an individual byte within this cache line. Alongside this, we will require some bits in the address to index into the actual cache itself, these bits are known as the *cache identifier*. On this hypothetical architecture, the top 21 bits are dedicated to the cache identifier and the

bottom 11 bits are dedicated to the *offset*, which is used to index bytes within a cache line. This decomposition is pictured in Figure 2.1.

Figure 2.1: Hypothetical decomposition.

The actual specifics as to how the identifier field is structured depends on the overall cache architecture. Upon a lookup, the cache will use the identifier to perform a search of all entries present within the cache. If the requested identifier is found, the CPU will use the offset bits to index the corresponding byte in the cache line.

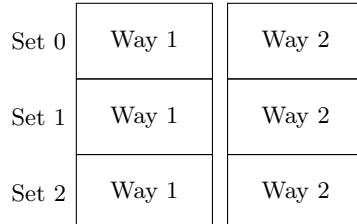

### 2.1.2 Cache architectures

There are many cache architectures, with the one most commonly used in practice known as a *set-associative* architecture. The set-associative architecture decomposes the cache into a set of buckets known as *sets*. These sets are then further broken down into smaller individual slots known as *ways*.

In a set-associative architecture with 4 sets, an address on a 32-bit machine with 2048 byte long cache lines is decomposed as a  $\log_2(2048) = 11$  bit offset,  $\log_2(4) = 2$  bit set identifier, and a 19 bit tag.

31

12

10

0

The set a cache line belongs to is determined purely by its address, specifically, the 2 set bits. When a cache line is inserted, the hardware uses these bits to determine the appropriate set for insertion and then places the line in the first free way in the set. If no ways are free, it will evict a way according to some eviction policy and place the cache line there. The story is similar for a lookup. The hardware will first determine what set a

line belongs to and then perform a parallel lookup for the tag within the set. If an entry with the same tag bits is identified, then it has successfully resolved the cache line to an entry in the cache.

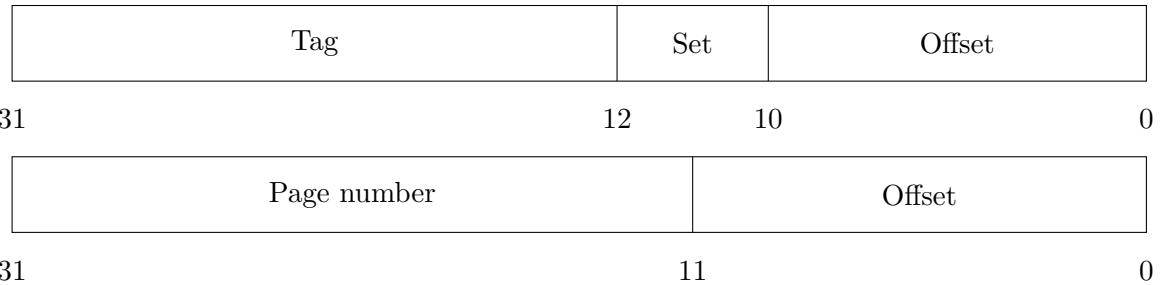

### 2.1.3 Cache colouring

Consider a set-associative cache on a 32-bit machine with 4 sets (2 set bits). In this cache, there are 11 bits dedicated to the offset and 19 bits dedicated to the tag. Alongside this, the machine also supports virtual memory, with the upper 20 bits of an address being used to determine the page number and the lower 12 bits being used to index into the page. This presents us with two differing ways that addresses are decomposed on the machine, with the first being how the cache deals with addresses and the second being how the *memory-management unit* (MMU) decomposes addresses.

The interplay between these two decomposition schemes give rise to an interesting property. Observe that the last bit in the page number coincides with the upper bit of the set identifier. It then follows that the cache lines residing in a page ending in 0 can only map to the sets 0 (00) and 1 (01), whereas a cache line residing in a page ending in a 1 can only map to sets 2 (10) and 3 (11). This situation is depicted more clearly in Figure 2.2.

The distinct regions of the cache that arise from this interplay between virtual memory and set-associative caching structures are known as *cache-colours*. The interesting insight is that addresses that reside in different cache colours will never map to the same cache sets within a cache. This insight will be of great value later when describing the present model of time protection as cache colouring is used to spatially partition specific caches.

Figure 2.2: Cache colouring [Heiser, 2024].

#### 2.1.4 Cache hierarchy

Caches within a machine are organised into strict hierarchies, typically the L1, L2 and L3 caches, with the last cache in any hierarchy being known as the *last-level cache* (LLC). These caches differ in their size and performance characteristics. The L1 cache, which is closest to the CPU, is optimised for fast reads, but maintains a rather small size (32 KiB on many modern chips). The L2 and L3 caches, on the other hand, lie further away from the CPU and maintain sizes on the order of a few MB (around 1 MB for the L2 and 4–64 MB for the L3). Alongside differing performance and size requirements, the caches differ in what addresses they use to index into the cache. Typically, L1 caches are *virtually indexed*, meaning that they use the virtual address when indexing into a cache. L2 and L3 caches, on the other hand, are *physically indexed*, using the physical address for cache lookups.

On many architectures, the L1 cache is split into two components: the *L1 data cache* (L1-D) and the *L1 instruction cache* (L1-I). The L1-D exclusively holds data, while the L1-I exclusively holds instructions. This split-cache design improves CPU performance by enabling the simultaneous access of both data and instructions.

The existence of multiple cache levels logically leads to the question of how data is duplicated between levels. In an *inclusive cache*, if data is present in the L1 cache, then it must also be present in the lower level L2 and L3 caches. The inverse holds for an *exclusive cache*, where data being present in the L1 cache implies that it is not present in either the L2 or L3 caches. Many ARM chips, such as the ARM Cortex series chips, maintain an exclusive policy between the L1 and L2 caches, whereas many Intel x86 chips maintain inclusive hierarchies.

The RISC-V *system-on-chip* (SoC) used for implementing the ideas discussed in this thesis

maintains a two-level cache hierarchy, one on-core cache (L1) and an LLC shared between multiple cores. The cache hierarchy guarantees that if a cache line is not present in the L1 cache, then a read of that line will bring it into both the L1 cache and LLC. The hierarchy does not maintain this inclusivity relationship forever though. It is possible for the same cache line to be later evicted from the L1 while still being present in the LLC, this presents interesting consequences when attempting to reason about the existence of a cache line within the cache hierarchy.

## 2.2 Timing Channels

Secure systems maintain restrictions on what subcomponents can communicate with each other. However, when these rules are broken, and a method of communication opens up that does not use a legitimate or intended communication path, then the system maintains a *covert channel*. Covert channels enable the unauthorised flow of information in a manner that the security policy of a system would otherwise disallow [Lampson, 1973]. Tangential to the idea of a covert channel is a *side channel*, which enables the unintentional leakage of data. Side channels consist of some victim and attacker process, with the attacker process using the side channel to spy on the victim process without its knowledge [Kocher, 1996]. The main distinction between a side channel and a covert channel is the covert channel’s requirement of cooperation to transmit information, this requirement also implies that covert channels maintain a significantly larger *capacity* and can transmit more information with a higher resolution. An interesting point is that despite requiring cooperation, covert channels can also be used to transmit information “unknowingly”, but they require introducing a *Trojan* to the victim process. Trojans are a piece of malicious code that is unknowingly introduced into a victim (usually via shared libraries) and leaks information to the attacking process silently [Anderson, 1972].

Shared microarchitectural state, such as caches discussed previously, enable the construction of *microarchitectural timing channels*. Microarchitectural timing channels exploit variations in program execution time – caused by microarchitectural state – to encode and transmit information. For example, if a CPU stores a piece of memory within its cache, subsequent accesses to that memory will be significantly faster. Two processes can exploit this behaviour to communicate via a shared, read-only memory buffer: one process accesses the first byte of the buffer to load it into the cache, while the other measures its access time for the same byte. A fast access may indicate a “1”, while a slow access may indicate a “0” – successfully sending information over a buffer that neither process has permission to write to. We exploit timing channels using *timing attacks*, with the two primary timing attacks used throughout this thesis being the Flush + Reload attack [Yarom and Falkner, 2014] and the Prime + Probe attack [Liu et al., 2015; Osvik et al., 2006; Percival, 2005], both of which can be used as an exfiltration technique in the Spectre and Meltdown attacks [Kocher et al., 2019; Lipp et al., 2018].

### 2.2.1 Flush + Reload

The Flush + Reload attack consists of a victim and an attacker process (also known as a spy), the attacker aims to learn something about the victim process by observing how the victim interacts with a buffer of memory shared between the two of them. When both processes share memory, they also inadvertently share parts of the last-level cache (LLC). The attacker exploits this by observing cache access patterns, allowing them to extract sensitive information from the victim in a way that violates the system's security policy [Yarom and Falkner, 2014].

The attack consists of three stages, first, the attacker flushes specific cache lines from the LLC using an instruction such as `clflush`, it then yields time to the victim process. The victim process runs for a bit and, with each memory access into the shared buffer, brings more data into the LLC. The spy, when it gets another time slice, will then time the amount of time it takes to access cache lines within the shared buffer. Fast access implies that the victim touched the cache line while running, whereas slow access implies that it did not. Using this information, the spy can infer what cache lines the victim accessed, and consequentially infer information regarding the victim's execution. This attack can be used to target RSA and trace the execution of the *square-and-multiply* routine, tracing this routine is sufficient to allow the attacker to break encryption [Yarom and Falkner, 2014].

```

while (true)

{

flush_llc();

yield_timeslice();

uint32_t start = current_time();

shared_buffer[0];

uint32_t elapsed = current_time() - start;

if (elapsed < threshold)

{

// Victim accessed this cache line

}

}

```

Listing 1: Example spy process.

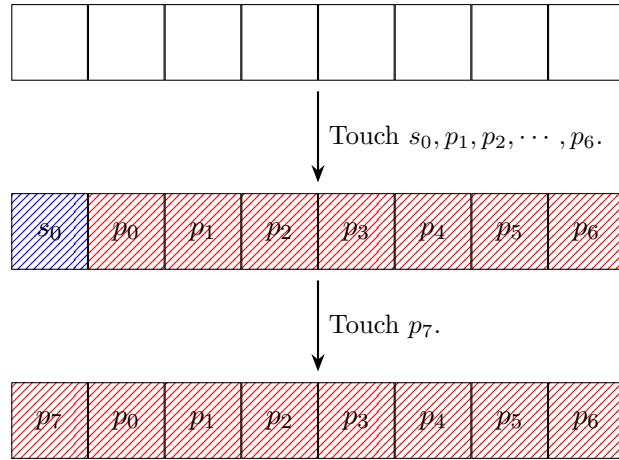

### 2.2.2 Prime + Probe

The previous attack relied on the existence of a shared buffer between the spy and victim process. In practice, this is not a requirement, and the Prime + Probe technique extends

cache timing channels to scenarios with no shared buffer. The attack introduces the notion of a *victim set*, which is a set of cache lines in the victim’s address space that the spy is interested in observing. The spy process must then determine how the victim set maps into its address space to construct an *eviction set* – a set of cache lines that overlap with the victim’s set. If the attack targets the virtually indexed L1 cache, this mapping is a straightforward one-to-one correspondence.

To begin the attack, the spy will first *prime* the eviction set by touching each cache line in the set, bringing them into the cache. Like the previous technique, the spy then yields its time-slice back to the victim. As the victim runs, it may potentially evict cache lines that the spy had brought into the cache. This is problematic, as when the spy is next allocated a time-slice, it can use this information to infer what cache lines the victim touched. In the final stage of the attack, the spy iterates through all the cache lines in its eviction set. If the access to a cache line is fast, it implies that the line was not accessed by the victim. Conversely, if the access is slow, it suggests that the victim evicted the spy’s entry by accessing the same cache set [Liu et al., 2015; Osvik et al., 2006; Percival, 2005].

To effectively pull off this attack, the spy must know how cache lines in its address space overlap with cache lines in the victim’s address space. This requirement is relatively easy to satisfy when targeting the L1 cache, as it is virtually indexed. However, there are still practical attacks that target the LLC using similar techniques [Liu et al., 2015; Osvik et al., 2006; Percival, 2005].

## 2.3 seL4 Background

seL4 is a capability-based microkernel with a strong focus on security and correctness. It is formally verified [Klein et al., 2009, 2014] to ensure both functional correctness and enforcement of its security properties [Murray et al., 2013; Sewell et al., 2011]. Being a microkernel, it provides a relatively small set of features and delegates most traditional OS-responsibilities to user-level threads that communicate over *IPC*. Typical seL4 based systems consist of some *initial thread* and upon boot, seL4 will hand information regarding the current system environment to this initial thread, from which it can create new threads and manage resources.

### 2.3.1 Capabilities

seL4 uses capabilities to control access to kernel resources, where a capability is defined as an unforgeable token representing the rights to access an entity or object [Dennis and Van Horn, 1966]. User-level threads interact with kernel resources via *invocations* on capabilities, with all kernel resources typically exposing their APIs via such invocations. Capabilities are organised into *CSpaces*, with a CSpace representing a structured tree of capabilities. To invoke a capability, user applications use a *CPtr* (capability pointer) to

index into a CSpace and identify the desired capability. In addition to invocations, capabilities support *copying* and *minting*, copying will create a duplicate of the capability with the same access rights whereas minting involves duplicating the capability with reduced rights [seL4 Foundation, 2024].

Memory management in seL4 is handled entirely at user-level, with the kernel having no method for dynamically allocating any data structures that it requires. As such, the kernel must provide an abstraction over physical memory that user-level applications can supply when requesting new kernel objects. This abstraction is known as *untyped memory*, with the kernel providing *untyped capabilities* for the management of this memory to the initial thread. These capabilities can be *retyped* into various data structures such as TCBs, notifications and physical frames of memory [seL4 Foundation, 2024]. Additionally, untyped capabilities have a boolean property `device` which indicates whether the memory is writeable by the kernel or not, as it may be in an area of RAM not addressable by the kernel. Device untyped capabilities can only be retyped into *frame* objects [seL4 Foundation, 2024].

### 2.3.2 Threads

Threads in seL4 model an execution context, allowing for the management of processor time [seL4 Foundation, 2024]. The key bookkeeping structure for a thread in seL4 is the *thread control block* (TCB) which maintains various metadata regarding a thread; namely the thread's CSpace and virtual address space (*VSpace*). On boot, the kernel constructs an initial thread with a basic CSpace. This thread uses the untyped capabilities provided to it to create additional threads for the system running on top of seL4. Threads are given a priority between 0 and 255. The seL4 scheduler will always schedule the thread with the highest priority if it is runnable. If there are multiple runnable threads with the maximal priority, then they are scheduled in a first-in-first-out, round-robin style fashion [seL4 Foundation, 2024].

### 2.3.3 Virtual memory management

seL4 provides virtual memory management through thin APIs over the hardware for manipulating hardware paging structures, rather than the higher-level abstractions found in systems like Linux. Common to all hardware architectures is the *Frame*, representing a frame of physical memory. Frames are mapped into VS spaces by manipulating the appropriate paging structures for the VSpace. The separation of frames and VS spaces also enables frames to be mapped into two separate address spaces, enabling shared memory between threads. It should be noted, however, that when attempting to map a frame into two distinct VS spaces, the capability for the frame must be duplicated and each mapping should correspond to a unique copy of the initial frame capability [seL4 Foundation, 2024].

### 2.3.4 Notifications

Notifications are a synchronisation primitive provided by seL4, they represent a set of binary semaphores and support the usage of small 32-bit badges to differentiate notifiers. They, like everything else in seL4, are allocated by retyping untyped memory, with the returned capability allowing for threads to either: *signal*, *poll* or *wait* on the notification. Signalling alerts any threads currently waiting on the notification, while waiting simply blocks the current thread until the target notification is signalled. The internal structure of a notification is simple, consisting of a 32-bit notification word and a queue of threads currently blocked on it [seL4 Foundation, 2024].

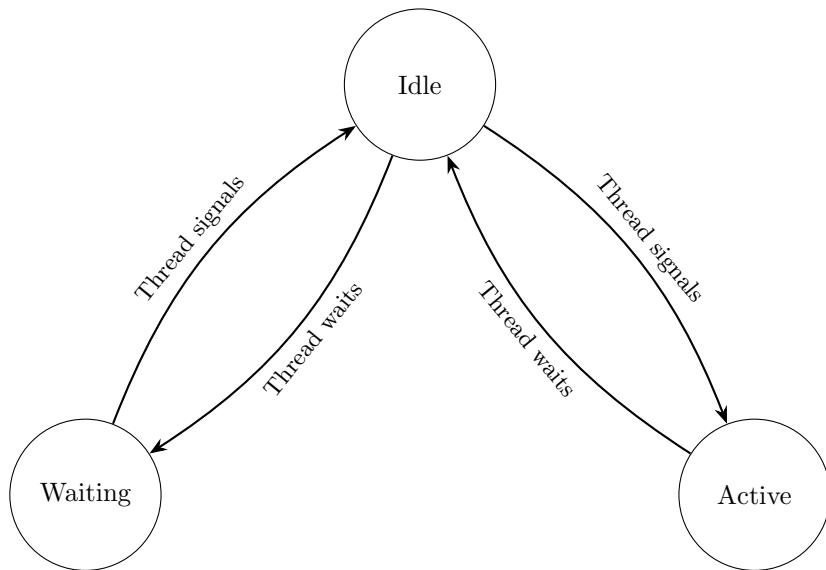

The exact behaviour of signalling or waiting on a notification depends on its internal state, which can be *waiting*, *active*, or *idle*. A notification enters the *waiting* state when a thread blocks on it, and transitions to the *active* state when it is signalled while no threads are waiting.

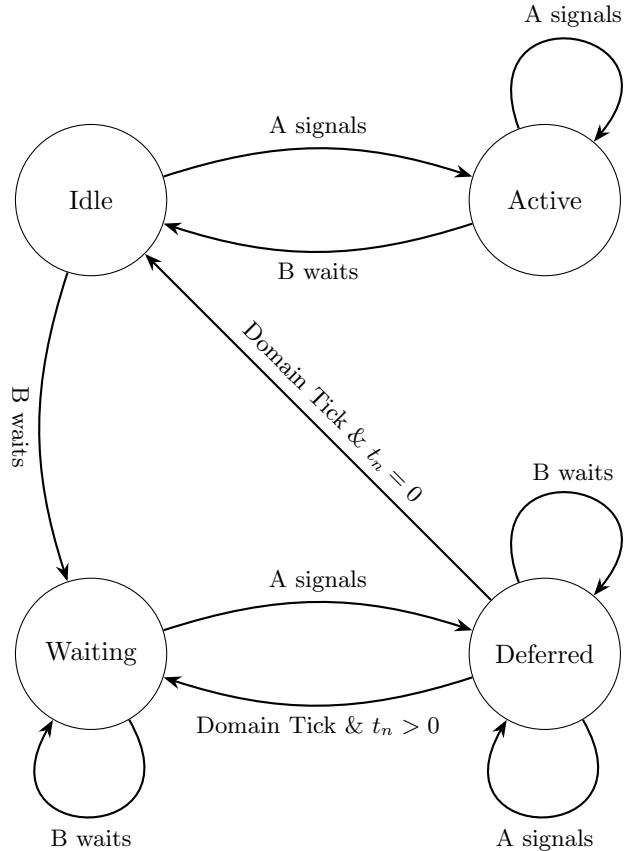

When signalling on an *idle* or *active* notification, the kernel will bitwise OR the badge value associated with the signal with the data word currently stored in the notification. If the notification is in the *waiting* state, however, the badge value is immediately delivered to the head of the blocked thread queue. When a thread waits on a *waiting* or *idle* notification, the requesting thread is added to the end of the thread queue, and the kernel marks the requesting thread as blocked. If, however, the notification is in the *active* state, the data word stored in the notification is immediately delivered to the thread and the notification's badge is reset to 0 [seL4 Foundation, 2024]. A state diagram outlining the above is illustrated in Figure 2.3 with pseudocode outlining the process in more detail being provided in Listing 2 and Listing 3.

Figure 2.3: Notification state diagram.

```

if (ntfn.state == IDLE || ntn.state == ACTIVE)

{

ntn.badge = bitwise_or(ntfn.badge, badge);

ntn.state = ACTIVE;

}

else if (ntfn.state == WAITING)

{

head = dequeue(ntfn tcb queue);

head.badge = badge;

head.state = RUNNING;

if (ntfn tcb queue is empty)

{

ntn.state = IDLE;

}

}

```

Listing 2: Signal pseudocode.

```

if (ntfn.state == IDLE || ntn.state == WAITING)

{

enqueue(ntfn tcb queue, thread_);

thread_.state = BLOCKED;

ntn.state = WAITING;

}

else if (ntfn.state == ACTIVE)

{

thread_.badge = ntn.badge;

ntn.badge = 0;

ntn.state = IDLE;

}

```

Listing 3: Wait pseudocode.

An important and interesting implementation detail regarding notifications is that since the kernel cannot perform any dynamic allocations, the queue of threads blocked on a notification is stored within the TCBs associated with the threads themselves. The notification maintains a pointer to the TCB for the first thread in its queue, and the *next* and *prev* pointers for the queue are maintained within each TCB.

### 2.3.5 Endpoints and IPC

seL4 use small kernel objects known as *endpoints* to perform *inter-process communication* (IPC). IPC is the microkernel mechanism for the transmission of small amounts of data and capabilities between threads. This same mechanism is also used for communication with kernel-provided services. Endpoints consist of a queue of threads waiting to send, wait or receive messages and can be optionally badged to distinguish senders on an endpoint [seL4 Foundation, 2024].

### 2.3.6 IRQs

Interrupts on seL4 are delivered as notifications, with a thread able to configure an interrupt to be delivered on a particular notification. A thread can then wait for the interrupt by blocking on the configured notification. seL4 introduces the `IRQHandler` capability to represent the ability for a thread to configure a notification to receive an interrupt [seL4 Foundation, 2024].

### 2.3.7 Domains

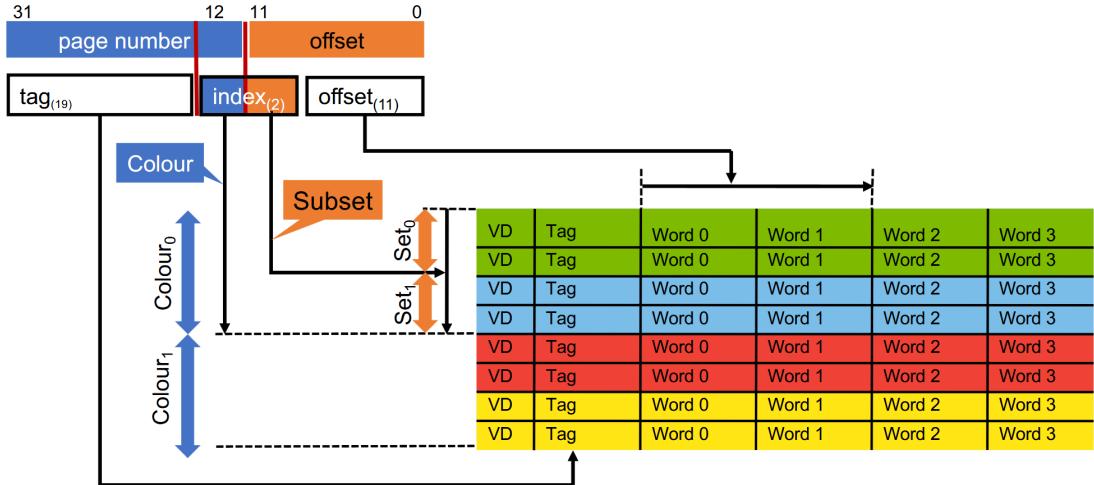

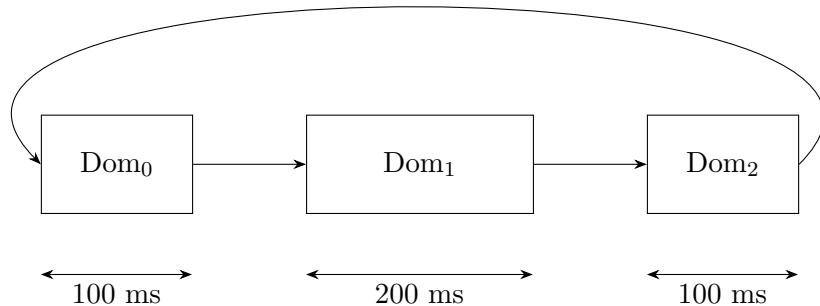

To maintain confidentiality, seL4 allows for threads to be associated with distinct scheduler partitions known as a *domains* [Murray et al., 2013]. Domains are statically configured at compile-time with a cyclical schedule and are not preemptible, an example domain schedule is provided in Figure 2.4. Threads can be associated with a domain, and the kernel will cycle between domains and only ever schedule the threads associated with the currently active domain. If there are no threads that can currently be scheduled in the domain's time-slice, then the kernel will schedule a dedicated *idle thread*.

Threads are assigned to domains via the `DomainSet_Set` invocation on the `Domain` capability passed to the initial thread. There is only one `Domain` capability, so the `Domain_Set` invocation differentiates domains with the domain number passed to it [seL4 Foundation, 2024]. The length of a domain's time-slice is provided as a multiple of the kernel *tick interval*, which is the duration of time between timer interrupts.

Figure 2.4: A static schedule for a hypothetical three domain system.

## 2.4 Cheshire

seL4 is capable of running on various platforms and devices. The platform of interest to us during this thesis is *Cheshire*. Cheshire is a minimal SoC built around the RISC-V CVA-6 core [Ottaviano et al., 2023]. Its goal is to provide a lightweight and configurable compute environment that is capable of easily targeting FPGAs with limited resources. Due to its highly configurable nature, different deployments of Cheshire can have different platform specs, the deployment used by this thesis for benchmarking has a core that runs at 50 MHz, maintains a 32 KiB L1 data-cache, a 16 KiB L1 instruction-cache, and a 128 KiB LLC.

### 2.4.1 LLC

Cheshire features a highly configurable set-associative LLC [Ottaviano et al., 2023]. This thesis uses a configuration of the LLC that consists of 64-byte cache lines and 256 distinct cache sets, with each cache set consisting of 8 distinct ways. All-in-all, this produces an 128 KiB LLC with 4 distinct cache colours. An interesting feature of Cheshire's LLC is the ability for each of its ways to be individually configured as *scratchpad memory* (SPM) at runtime, providing the host with fast on-chip SRAM [Ottaviano et al., 2023]. It is important to note that if a way is configured as SPM, it cannot be used for regular caching purposes, therefore configuring a single way as SPM will reduce the effective associativity of the cache by one. The LLC maintains a randomised eviction policy, whereby a way is evicted at random when a set is full. This randomised eviction policy maintains interesting consequences for the design of cross-domain shared memory, as will be discussed in Chapter 8.

### 2.4.2 Microarchitectural flush

Throughout this chapter, we have seen a lot of literature that demonstrate how microarchitectural state within a CPU can be used to exploit timing channels by constructing timing attacks. Existing work highlights the ineffectiveness of modern architectures to protect against such attacks due to the inability to reset microarchitecture state effectively [Ge et al., 2018].

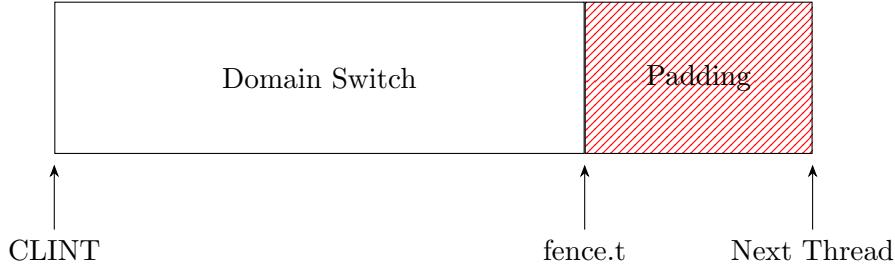

Drawing from these lessons, the CVA-6 core that Cheshire is built around introduces a special `fence.t` instruction that flushes the L1 cache and resets all other microarchitectural state within the CVA-6 core to a known state [Wistoff et al., 2021]. Since the latency of the `fence.t` operation depends on the state of said micro-architectural state, the instruction also features a simple time-padding mechanism that will pad the time between the last *core-local timer interrupt* (CLINT) and the `fence.t` invocation to some configured *worst-case execution time* (WCET) [Wistoff et al., 2023]. The fact that the instruction pads relative to the last timer interrupt allows it to be used to pad any operations that proceed `fence.t` to some WCET.

To enable time-padding, the implementation exposes a custom `cspad control-status register` (CSR), the core will read this value on the arrival of a timer-interrupt and use this when performing time-padding. It is also worth pointing out that `fence.t` is not the only instruction configured to flush the L1-D cache, Cheshire configures the CVA-6 core so that the regular `fence` instruction also flushes the L1-D cache.

### 2.4.3 OpenSBI

The RISC-V architecture maintains three privilege levels: machine-mode (highest privilege with unrestricted system access), supervisor-mode (for OS kernels), and user-mode (for applications). Since supervisor-mode is not the highest privilege level and does not have direct access to the hardware, many operating systems targeting RISC-V are deployed on-top of a thin firmware layer known as *OpenSBI*. Whenever the kernel attempts to access a CSR or any other hardware resource that it is not configured to have permissions for, Cheshire will trap into OpenSBI who will then interact with the hardware on behalf of the kernel [RISC-V International, 2025]. Cheshire maintains its own fork of OpenSBI with some minor platform-specific changes, this is the build of OpenSBI that we will use throughout this thesis [PULP Platform, 2025b].

## 2.5 Time Protection in seL4

Time protection refers to a collection of operating system mechanisms that jointly prevent interference between separate domains within a system, ensuring that it is impossible to construct a timing channel between what should be isolated domains [Ge et al., 2019]. To achieve time protection, the current model partitions all resources shared between

domains either *spatially*: which involves dividing state into non-overlapping regions, or *temporally*: which divides shared resources across time [Ge et al., 2019]. To spatially partition resources, the model ensures that each domain is assigned a specific region of the resource and guarantees that it can only access its dedicated region. Temporal partitioning is achieved by assigning each domain a fixed *time slice*; at the end of a domain’s time slice, all resources that cannot be spatially partitioned are reset and flushed in preparation for the next domain [Ge et al., 2019]. However, resource partitioning alone is insufficient to achieve time protection. To fully realise time protection, seL4 must enforce all the following requirements [Ge et al., 2019]:

- R1. When switching domains (known as a *domain switch*), the OS must reset microarchitectural state to a defined state, unless the hardware supports spatially partitioning such state.

- R2. Each domain must have its own private copy of the OS text, stack and global data (as much as possible).

- R3. Access to any remaining shared OS data must be deterministic to avoid leakage.

- R4. State flushing must be padded to its worst-cast latency.

- R5. When sharing a core, the OS must disable or partition any interrupts apart from the preemption timer.

### 2.5.1 Requirement 1 for Time Protection

Some microarchitectural state such as the LLC can be spatially partitioned using techniques such as cache colouring. Cache-colouring based partitioning assigns a unique colour to each domain to prevent interference between domains within the LLC. The implementation of this partitioning scheme in seL4-based systems is relatively straightforward and can be done with virtually no help from the kernel. On boot, the kernel will provide the initial thread with the `seL4_BootInfo` structure, which, alongside much else, contains a description of the physical ranges of memory associated with each untyped capability [seL4 Foundation, 2024]. Knowing the physical addresses associated with untyped capabilities allows the initial thread to divide memory into coloured “pools”, which can then be used to allocate kernel structures and memory frames of a specific colour. As long as the initial thread ensures that all data structures and frames for a domain are allocated from a single coloured memory pool, cache colouring guarantees that cache lines associated with different domains will not overlap, thereby effectively spatially partitioning the LLC among domains [Ge et al., 2019].

Not all microarchitectural state can be partitioned, and in such cases the kernel must reset this state upon a domain switch. The unfortunate reality however, is that the kernel is limited here by the extent to which the architecture it is targeting supports flushing microarchitectural state [Ge et al., 2018]. x86 provides limited support for resetting on-core state, while ARM supports flushing the L1 D-cache, TLB and branch-predictor. The story is slightly different on RISC-V with all SoCs built around CVA-6 supporting the `fence.t` microarchitectural flush and padding instruction [Wistoff et al., 2021, 2023].

### 2.5.2 Requirements 2 & 3 for Time Protection

System calls will leave some residual impact on microarchitectural state, i.e. they may maintain some cache footprint that is potentially observable outside the kernel [Ge et al., 2019]. This issue can be addressed by having each domain maintain a unique copy of the kernel to prevent the kernel from being used as a timing channel [Ge et al., 2019].

Ge et al. [2019] proposed a policy-free *kernel clone* mechanism, whereby the initial thread can construct a copy of the kernel from user-provided frames of memory. Each cloned kernel maintains its own kernel-code and read-only data segments. Realistically, some data needs to be shared between clones and special care is taken to ensure that accessing this shared data is sufficiently deterministic, i.e. by pre-fetching shared data when switching between kernels. The kernel clone mechanism enables the initial thread to construct a fully partitioned system, with each domain allocated its own unique kernel, backed by memory drawn from the domain’s coloured memory pool. It is worth pointing out that not all ports of time-protection maintain this kernel-cloning mechanism. Work done by Buckley et al. [2023] in porting the time-protected kernel to RISC-V introduced a static policy, where the kernel clone for each scheduler domain is created on boot. On the RISC-V port, the initial thread cannot create kernel clones and can only associate threads with an existing kernel clone by attaching them to a target domain.

### 2.5.3 Requirement 4 for Time Protection

As previously outlined, all resources that cannot be spatially partitioned must be temporally partitioned by flushing them during a domain switch. The latency of these flushing instructions typically depends on the contents of the resources [Ge et al., 2019]. For example, the flush latency of the L1 cache varies depending on the number of cache lines currently stored within it. It then becomes a requirement that all these microarchitectural flush operations be padded to their worst-case execution latency. If this is not done, then a channel exists via the flush latency.

In practice, time-padding is achieved by configuring an upper bound on the WCET of the domain switch latency. If there is no direct-hardware support for time-padding, then the kernel will busy-wait until this specified WCET has elapsed. On Cheshire and other CVA-6 based systems, there exists support for WCET padding via the `fence.t` instruction. CVA-6 allows for the time between the core-local timer interrupt and a subsequent `fence.t` invocation to be padded to some WCET [Wistoff et al., 2023]. Without padding, the next domain can observe variations in the domain switch latency, as the domain switch latency directly affects when the first thread in the new domain is scheduled [Ge et al., 2019].

Figure 2.5: Padding the domain switch latency.

#### 2.5.4 Requirement 5 for Time Protection

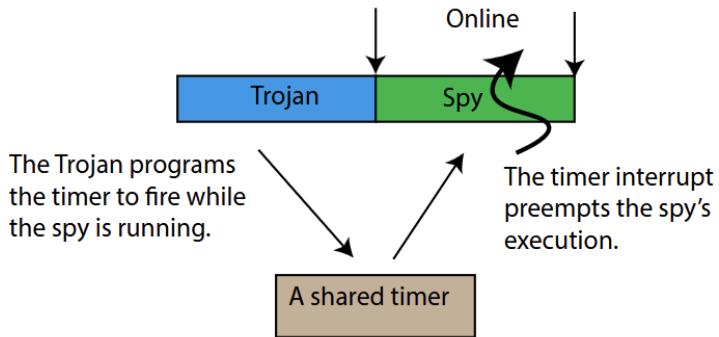

Interrupts can be used as a channel between domains, a Trojan can program interrupts to fire during the spy's time slice. This is problematic as the system clock at the time the interrupt is fired can be used to encode messages [Ge et al., 2019]. This channel, although maintaining a relatively low *bandwidth*, is still problematic. To mitigate this, the model allows for the partitioning of interrupts, with only some set of interrupts being associated with each domain [Ge et al., 2019].

Figure 2.6: Interrupt being used as a channel between domains [Ge, 2019].

#### 2.5.5 Time Protection on RISC-V

The original implementation of time-protection targeted the ARM and x86 architectures; however, due to the lack of architectural support, there was still at least one timing channel on each architecture that could not be closed [Ge, 2019; Ge et al., 2018]. By observing these limitations, it was argued that to fully realise time protection, a new hardware-software contract was required, one that allowed for microarchitectural state to be fully flushed [Ge et al., 2018].

Due to the limitations in x86 and ARM architectures, Wistoff et al. [2021] proposed the `fence.t` instruction as an extension to RISC-V. Further work carried out by Buckley et al. [2023] ported time-protection to RISC-V, more specifically a RISC-V based system using the CVA-6 core. Doing so allowed them to make use of the new `fence.t` instruction to flush on-core microarchitectural state. Additionally, this port made several simplifications to the model of time-protection, namely the fact that the provided implementation now constructs a unique kernel clone for each domain at boot, switching the currently active kernel image whenever there is a domain switch [Buckley et al., 2023].

Ge et al. [2019] used pre-fetching to determinise shared-kernel data in the LLC during domain switches. With time-protection now tied to seL4’s domain scheduler, most shared-kernel data can be partitioned, leaving only a small remainder accessed deterministically on domain-switches [Buckley et al., 2023]. Further unpublished work carried out by Julia Vassiliki, Nils Wistoff, Dr Rob Sison and Professor Gernot Heiser has ported the original RISC-V re-implementation to Cheshire. By doing so, all remaining shared kernel data can now be placed within scratchpad memory, thereby eliminating any potential timing channels as SPM is never cached by the LLC. The implication of this, however, is that the effective associativity of Cheshire’s LLC is now 7 instead of 8, as one way is marked as SPM. All the designs discussed in this thesis will be implemented on top of the Cheshire port.

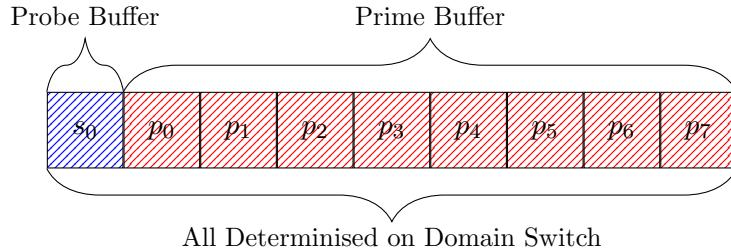

### 2.5.6 The domain switch on RISC-V

Understanding the domain switch operation will be of vital importance for the rest of this thesis so we will take some time now to look at it in more detail on RISC-V. On Cheshire, the domain switch is triggered by the arrival of a CLINT. On a CLINT, the interrupt handling path will reset the timer interrupt and schedule a new one to arrive some number of milliseconds in the future. After resetting the timer interrupt, the kernel will identify that the current domain’s time-slice has elapsed and trigger a domain switch.

The domain switch occurs in two distinct phases, during the first phase, the kernel will identify the next domain to schedule and switch to its kernel image. After switching the kernel image, the kernel now operates within the cache colour associated with the kernel of the new domain. The kernel will now perform a `fence.t` invocation to erase any impact the old domain had on the non-partitionable microarchitecture. The implication of performing the `fence.t` after switching the kernel image is that only the operations performed up to and including the `fence.t` are padded to a WCET. These operations are: handling the CLINT, resetting the timer, switching the kernel image, and invoking `fence.t`. The second half of the domain switch, while not strictly part of the domain switch itself, involves determining the first thread in the new domain to schedule and scheduling it. It is important to note that all the domain switch operations happen after resetting the time interrupt. As such, the latency of all these operations are charged to the new domain, and the new domain can observe this latency by observing when its first thread is scheduled.

## 2.6 Time Protection in seL4 — Taking It Further

The current model of time protection in seL4 requires all kernel data structures and memory frames used within a domain to be allocated from that domain’s coloured memory pool. As a result, there is no clear way for threads in two different domains to communicate with each other while still maintaining time protection. Communication in most deployments of seL4 involves using shared memory to transfer large amounts of data between threads, alongside the use of notifications to orchestrate the access to this data; it then becomes natural for us to explore extending these communication primitives such that they can be used across domains. The remainder of this thesis is dedicated to exploring this very problem. We explore cross-domain notifications in Chapter 5 and Chapter 6, and cross-domain shared memory in Chapter 8 and Chapter 9. Our exploration of cross-domain notifications and shared memory will lead to the introduction of new kernel objects that enable domains to signal each other and communicate without leaking information. We will also look at how the proposed design for cross-domain shared memory can be implemented at user-level, completely cutting the kernel out of the picture.

## Chapter 3

# Related Work

This chapter surveys various timing channel mitigation techniques and explores how they can potentially inform the design of cross-domain shared memory and notifications. We will also examine the existing literature on timing channel benchmarking and explore it may guide the method by which we may evaluate our proposed designs for cross-domain notification and shared memory.

### 3.1 Constant Time Programming

A common and recommended approach in many cryptographic applications is to use *constant-time programming* to eliminate channels [Bernstein, 2005]. To focus on how these techniques may be applied, we will look at Meier et al. [2021], who builds upon these principles to guide the implementation of the constant-time arithmetic library `saferith`. The authors build upon three key requirements that constant-time programming aims to maintain:

1. No loops that leak the number of iterations taken.

2. No memory accesses that leak the address or index that was accessed.

3. No conditional statements that leak which branch was taken.

The authors propose a simple API that ensures all applications using the library are compliant with the above requirements. While basic benchmarks are presented to demonstrate the constant-time behaviour of operations such as `Exp`, the evaluation lacks substantive evidence showing whether constant-time programming effectively eliminates timing channels in typical cryptographic algorithms. In fact, Schneider et al. [2024] demonstrates that many constant-time programming techniques are undermined during compilation, primarily due to aggressive compiler optimisations and the introduction of secret-dependent

instructions. This highlights the fragility of such techniques and the difficulty of implementing them correctly in practice. Additionally, certain constant time techniques such as avoiding secret-dependent table lookups require direct hardware support [Page, 2003].

### Discussion and Takeaways

The literature highlights that many constant time programming techniques are relatively fragile and difficult to implement, on top of this, many techniques offload the responsibility of time protection onto the application. seL4 aims to ensure that time protection is an abstraction provided by the OS, much like memory isolation; confining even untrusted programs from leaking information to the outside world. Relying on every application running on seL4 to use constant time techniques fundamentally breaks this abstraction.

While it is infeasible to expect all applications to use constant-time techniques when interacting with the communication primitives we construct, some of these ideas still provide practical guidance for the design of such primitives. When implementing primitives such as cross-domain notifications, it is crucial to maintain the invariant that operation latency remains independent of notification state. The principles of constant-time programming could find some applications here and act as a guide for maintaining such an invariant, but any design using these principles will require thorough benchmarking and verification.

## 3.2 Pre-fetching and Forced Determinism

Ge et al. [2019] illustrates the use of *pre-fetching* to ensure that all access to *shared kernel data* (SKD) within time-protected seL4 is sufficiently deterministic. The approach involves identifying all the cache lines associated with shared kernel data and then manually “touching” them on a domain switch to force them into the L1 cache and LLC [Ge et al., 2019]. The authors demonstrate the effectiveness of this approach when combined with separated kernel images in closing the timing channel associated with a shared kernel image. An important omission in the paper, however, is the sensitivity of the proposed method to specific cache implementation details, particularly the inclusiveness or exclusiveness of the cache hierarchy. In the absence of architectural guarantees, it remains unclear how the timing behaviour of subsequent accesses to pre-fetched cache lines are affected if those lines are evicted from any part of the cache hierarchy.

Buckley et al. [2023] extends this analysis and presents some insight into the use of pre-fetching for shared kernel data in time-protected seL4 on RISC-V. They highlight that pre-fetching is completely insufficient for closing timing channels through SKD, and the only principled solution for closing such channels is via targeted flushes of the address associated with shared kernel data from the LLC. They also highlight the verification challenges with pre-fetching, as verifying the effectiveness of pre-fetching requires a detailed model of the LLC’s eviction policy to truly prove correctness and safety. It is worth pointing out that these conclusions are drawn in the context of shared kernel data, where due to the lack of partitioning and colouring, the cache lines of which can be arbitrarily affected by the

activities of threads in partitioned domains. There remains the question of whether pre-fetching is effective when we can guarantee that threads cannot interfere with the cache sets associated with the pre-fetched memory block, aside from direct reads and writes, that is, when the memory being pre-fetched resides in a dedicated colour.

### Discussion and Takeaways

Buckley et al. [2023] argues that pre-fetching fails to close timing channels through shared kernel data. This implies that pre-fetching is not a suitable solution for implementing cross-domain shared memory if the colour used to back the shared memory is common to either the reader or writer domain. This stems from the fact that when cache lines belong to a common colour, as is the case with SKD and domain partitioned data, it becomes difficult to predict, without a formal model of the eviction policy, how pre-fetching interacts with cache lines that map to the same cache set(s) as SKD within the LLC, as well as how those overlapping lines, in turn, affect the data being pre-fetched.

There is still, however, a remaining question as to if pre-fetching works if the shared buffer is allocated its own dedicated colour. In this situation, we are no longer concerned with how pre-fetching affects overlapping cache lines that are unrelated to the buffer. Instead, we focus on how it affects the cache lines associated with the shared buffer. It is entirely plausible that even without a definitive conclusion about whether a specific cache line in the shared buffer is present, we may still conclude that pre-fetching ensures the *probability* of a cache line being present in the LLC is independent of the buffer’s state before pre-fetching. In such a situation, we would not be able to observe or construct a timing channel via the microarchitectural state of the buffer.

As such, pre-fetching *may* be an effective solution for determinising the microarchitectural state associated with a buffer, it is just that the results of Buckley et al. [2023] strongly suggest that it is ineffective if the colour of the buffer is a colour common to any other domain. Pre-fetching may be a viable approach, but any implementation of shared memory that uses it must be benchmarked thoroughly to demonstrate that no timing channel via the microarchitectural state of the buffer exists after pre-fetching.

### 3.3 Noise Injection

The noise injection technique aims to reduce the signal-to-noise ratio of a timing channel by introducing “noise” into the attacker’s measurements. This can be done either by injecting noise directly into timing measurements or by perturbing memory access patterns so that the attacker observes noisy behaviour. Approaches such as virtualised timestamps, as proposed by Vattikonda et al. [2011], attempt the former but remain largely infeasible under the current model of time protection due to lack of hardware support. Consequently, the more promising approach is the techniques that Brickell et al. [2006] employed to produce a secure AES implementation. The implementation outlined in the paper involves compacting, randomising and preloading lookup tables, which were sufficient in removing the timing vulnerabilities in AES outlined by Bernstein [2005].

### Discussion and Takeaways

A potential application of this technique would involve touching random cache lines associated with a shared buffer on a domain switch, thereby introducing noise to any information that could be leaked via this buffer. However, as Cock et al. [2014] points out, noise is usually an ineffective means of closing channels. As they state, what is really needed is noise that is *anti-correlated* to the distribution of the timing channel. In many situations, this is impossible or infeasible to generate, or it may incur a significant performance overhead. It should also be noted that noise injection is not a principled solution; it relies heavily on experimentation, as the amount of noise that must be introduced to mitigate a channel depends on the capacity and resolution of the channel. As such, it is unclear if this technique is truly one that will find much application in any design for cross-domain shared memory or notifications.

### 3.4 Time-Padding

Ge et al. [2019] outlines the use of *time-padding* to mitigate channels that arise due to the latency of operations with non-constant execution time. The authors employ this approach to close the *cache-flush* channel, which results from variable L1 flush latencies. The method involves padding operations with non-constant latencies to their worst-case execution time, and the authors provide empirical evidence to support the efficacy of this approach, as the cache-flush channel outlined in the paper is sufficiently closed. Time-padding has also been explored thoroughly before, Braun et al. [2015] used it to design a set of compiler directives for generating fixed time functions, they do this by employing software-based time-padding and use uniform random noise to handle secret dependent error.

### Discussion and Takeaways

This approach was effective in closing the cache-flush channel studied by Ge et al. [2019], as well as various other channels studied by Wistoff et al. [2023]. It is worth pointing that this method does have one fundamental flaw, failure to accurately bound the WCET latency will result in a complete failure of this mechanism to mitigate any timing channel. Additionally, a purely software-based approach to time-padding does present some performance overhead, justifying the introduction of a hardware-based padding primitive in Wistoff et al. [2023].

Regardless, this technique is clearly effective, and due to its integration within the existing system model, is very much a technique worth using when implementing cross-domain shared memory and notifications. It may find particular value if we ever encounter the need to flush or determinise the microarchitectural state associated with a shared memory buffer or pad signals on a notification to a constant time.

## 3.5 Cache Partitioning

The previous techniques focused on mitigating timing channels when resources are shared between domains. It is also important to explore partitioning schemes – particularly cache partitioning – and how these alternatives might support the construction of cross-domain notifications and shared memory. One possible direction for this thesis is to migrate seL4’s current time protection model to a dynamic cache partitioning scheme. This would allow cache partitions to be created on the fly and assigned to shared buffers or data structures between domains. However, unfortunately due to time constraints this avenue of work was not explored.

### 3.5.1 CATalyst

Liu et al. [2016] outlines a method for dynamically partitioning the LLC using Intel’s cache allocation technology (CAT). CAT allows for the creation of up to 4 “classes of service (COS)” and allows for the association of logical processors with a COS. The implication of this interface is that all threads on the same logical processor share a COS.

CATalyst introduces *secure pages* and splits the LLC in two, with one half used for pinning secure pages in the cache and the other for regular caching. This effectively turns the LLC into a “hybrid” cache, with the secure half acting as a software-managed cache and the unsecured half acting as a hardware-managed cache. At a high level, the idea is that a process will interact with the secure portion of the cache via the `map_sp` and `unmap_sp` system calls. The `map_sp` system call will load secure pages into the requesting process and pin them in the secure cache, the process can then use the secure page without fear of the page being evicted by cache contention.

The authors use this idea to close a side channel that they identified in *GnuPG*; using `map_sp` and `unmap_sp` to map/unmap the pages containing the “square routine” onto secure pages. The security evaluation provided in the paper illustrates that the technique is indeed capable of eliminating the identified side channel.

### Discussion and Takeaways

One potential application of CATalyst in the context of this thesis is to use secure pages to back shared buffers. However, this approach presents several challenges. The paper does not describe how one would map secure pages into multiple processes, requiring further exploration. Moreover, utilising CATalyst would constrain the approach to x86 architectures. Furthermore, it is unclear if CATalyst is compatible with seL4’s current use of cache colouring to partition the LLC, or if a suitable compatible alternative exists. Regardless, CATalyst provides a valuable exploration of an alternative cache partitioning scheme beyond cache colouring and introduces dynamic partitioning approaches that do not depend on static cache partitions.

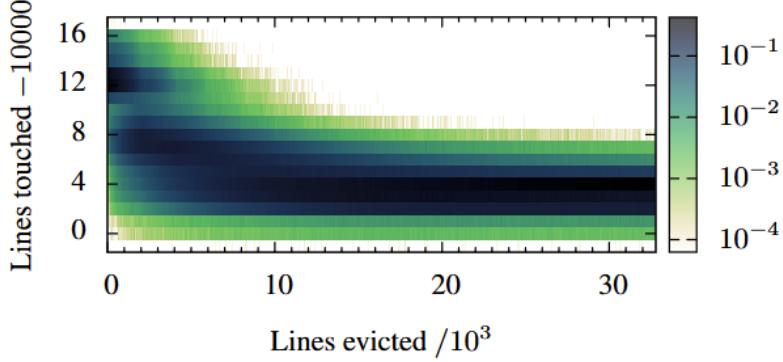

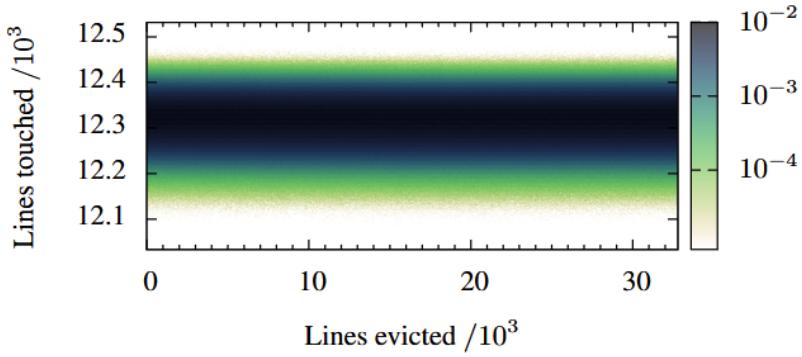

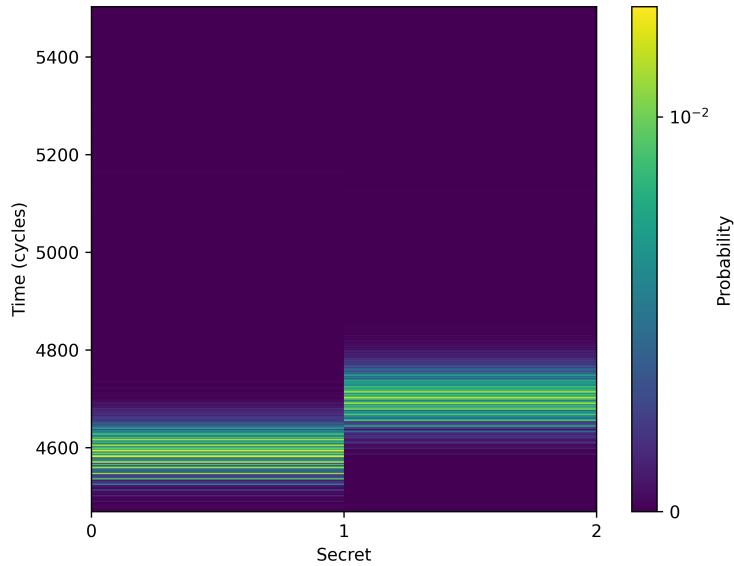

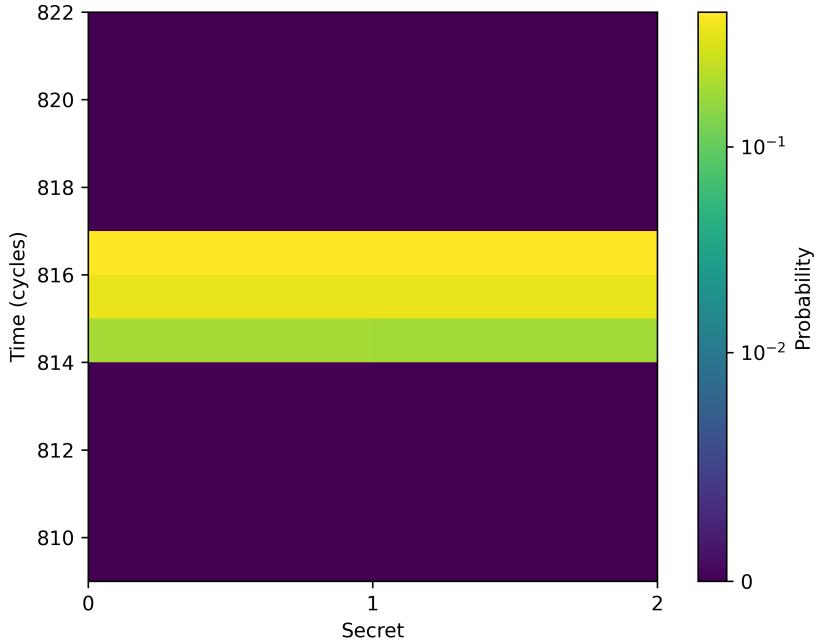

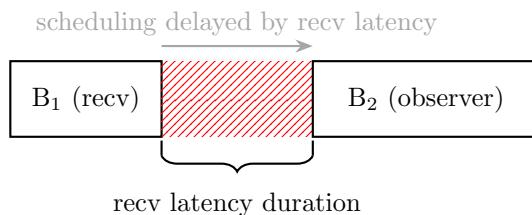

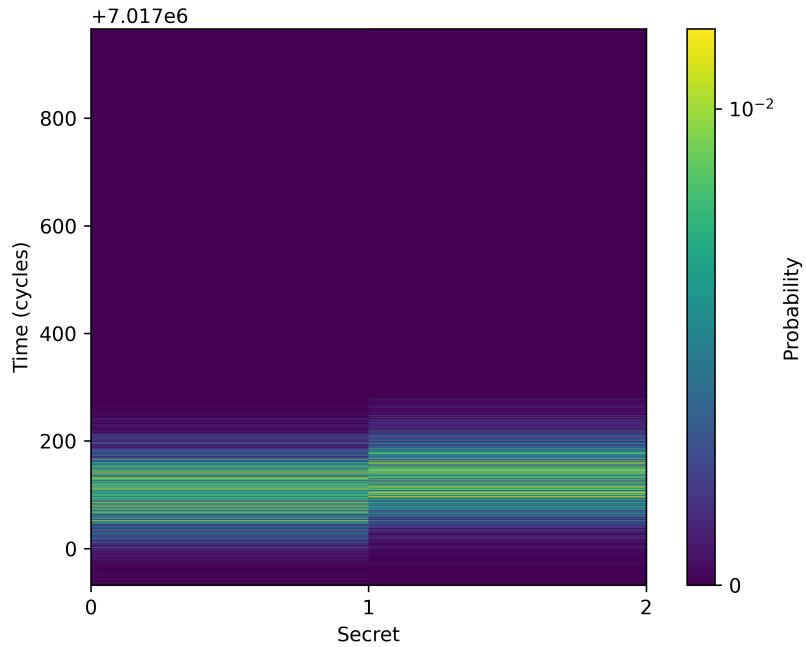

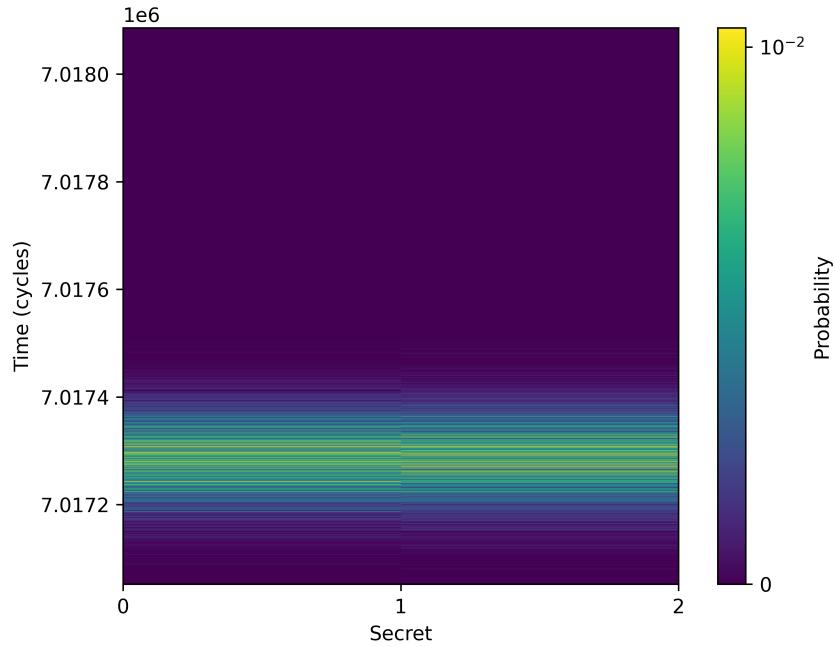

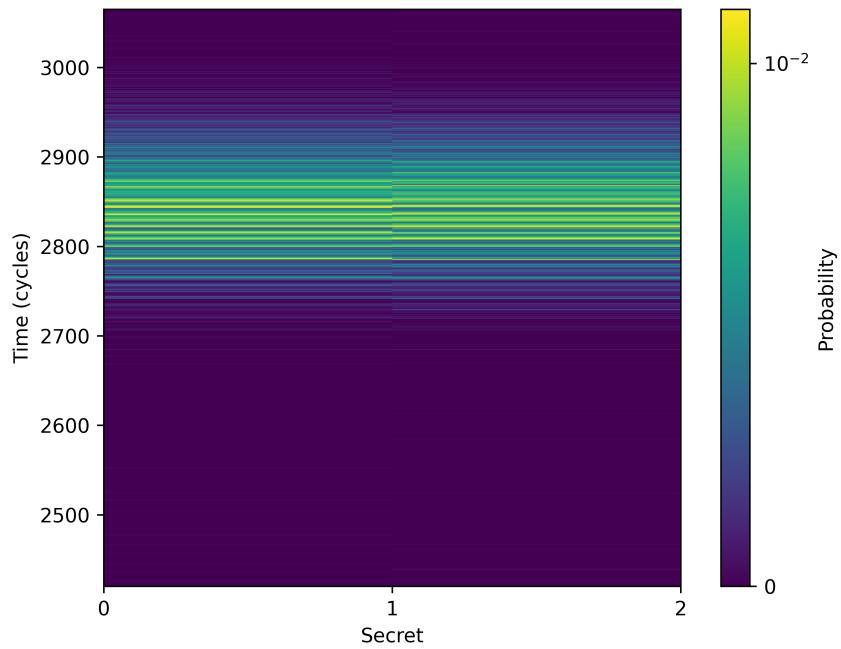

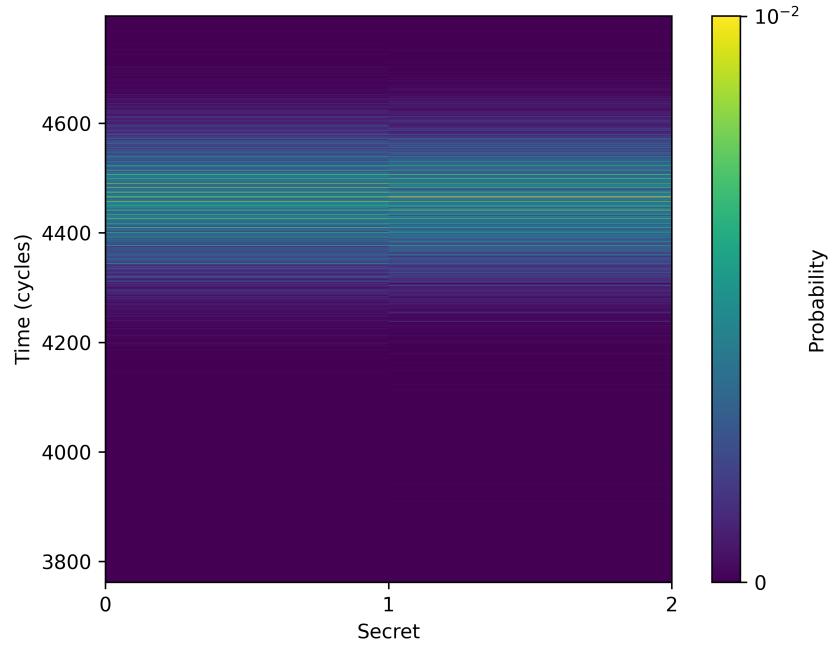

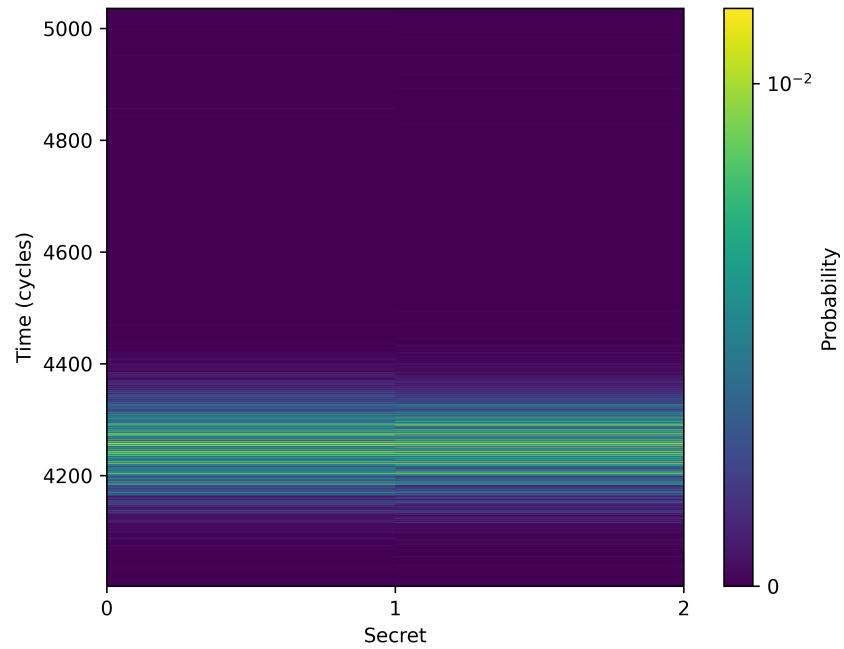

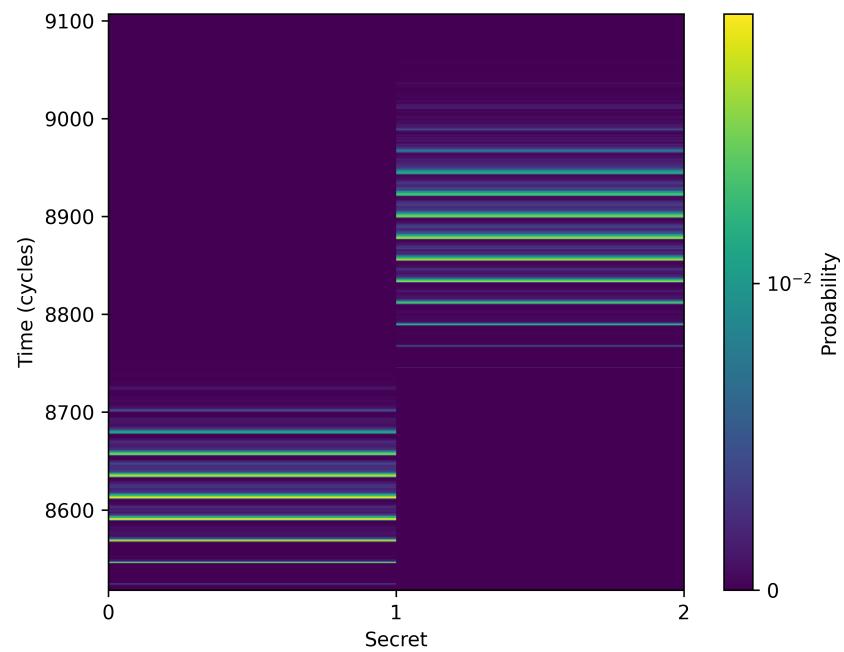

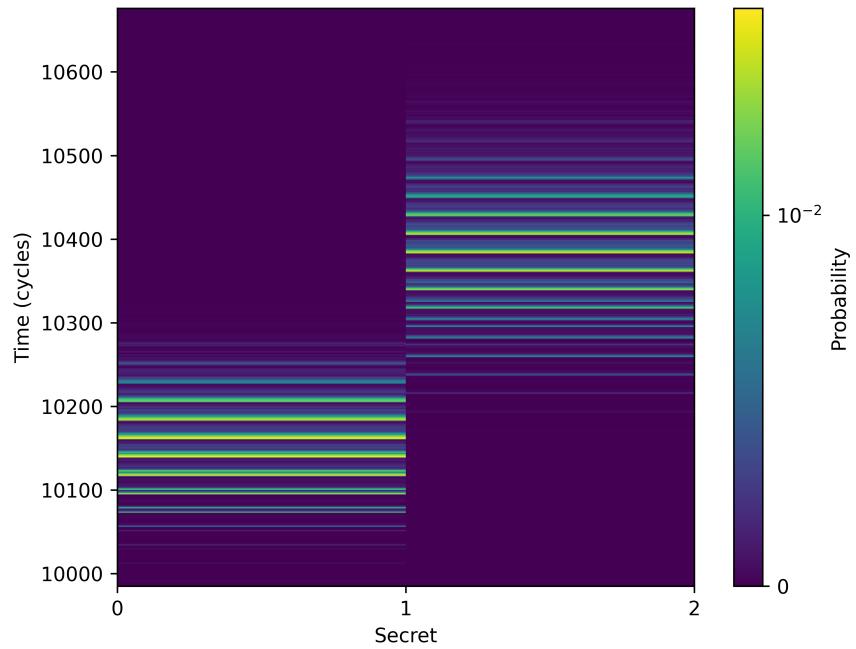

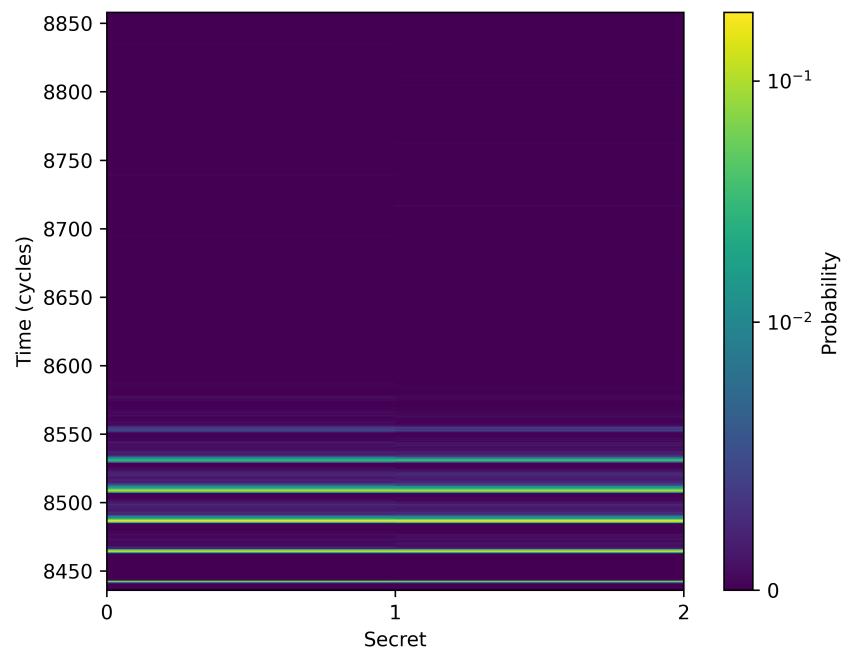

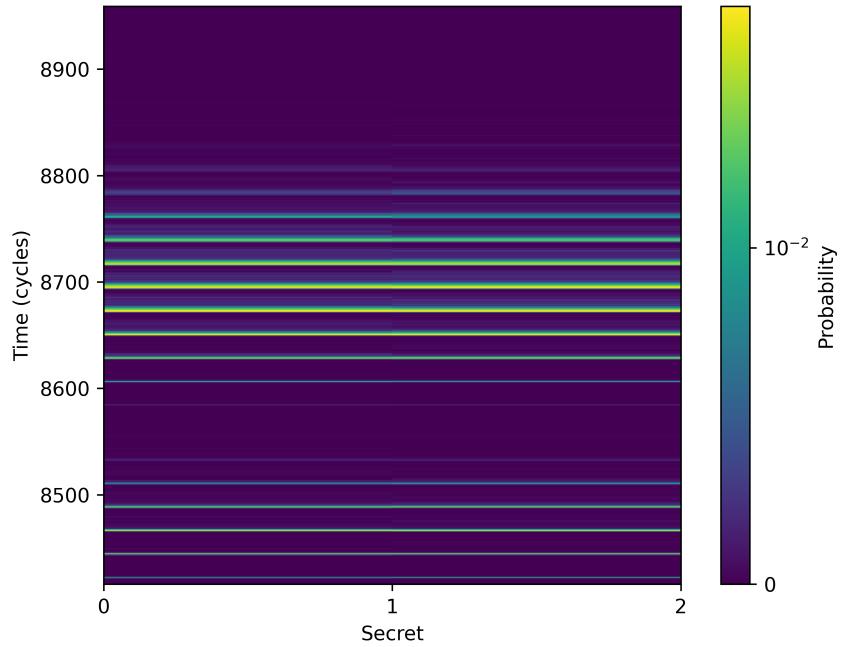

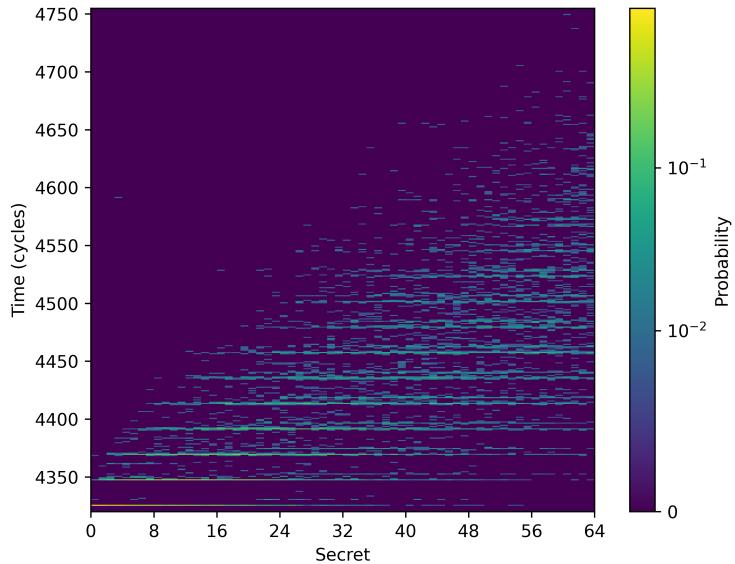

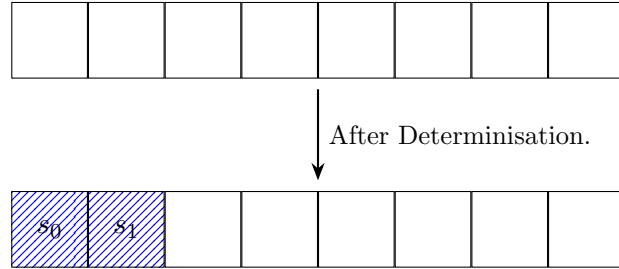

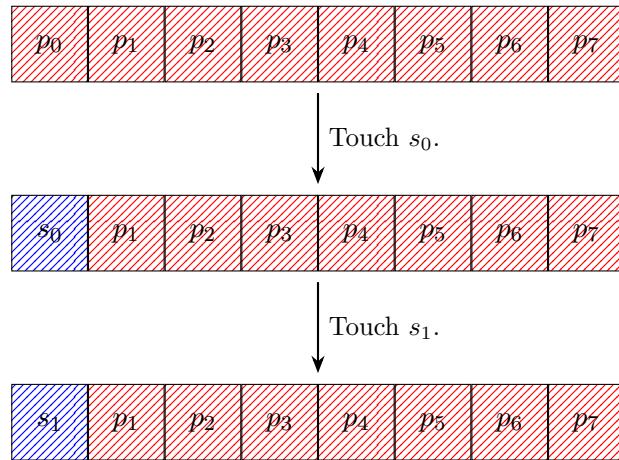

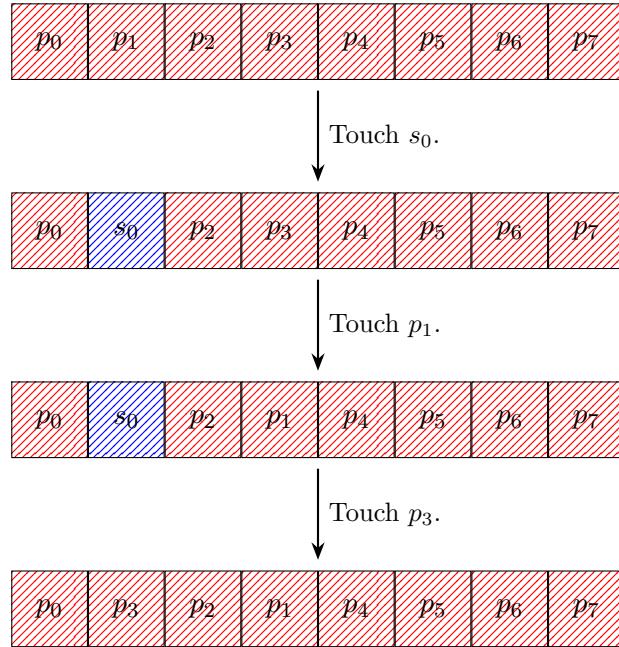

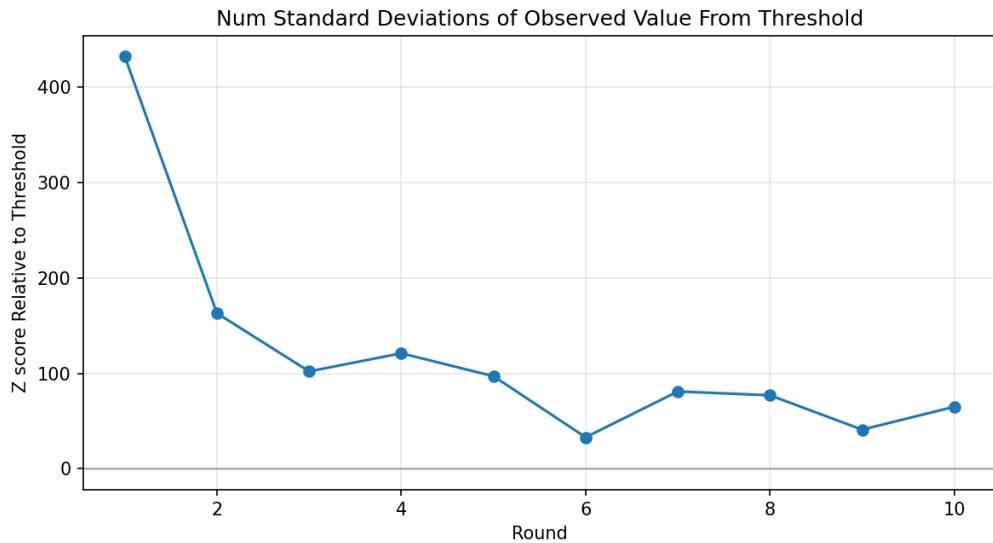

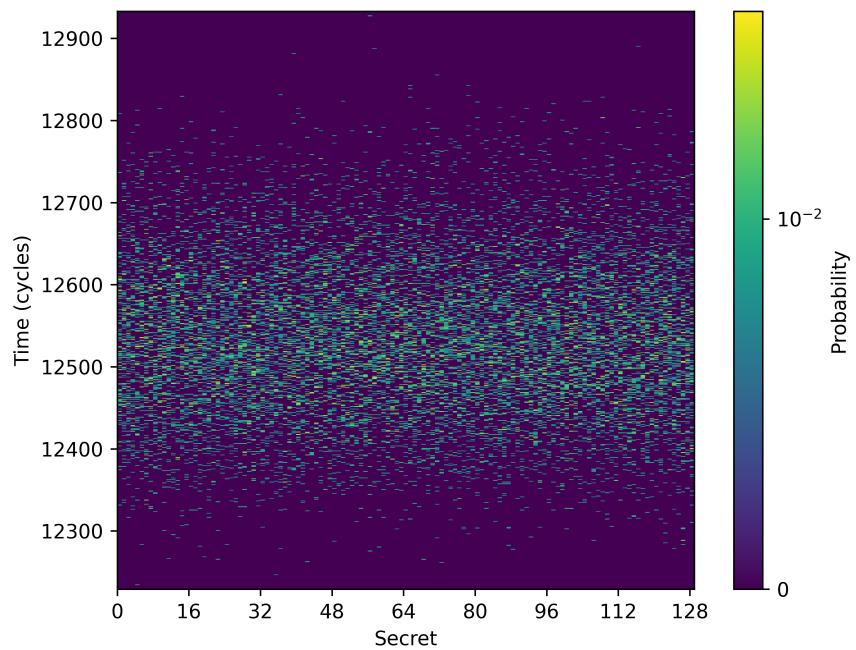

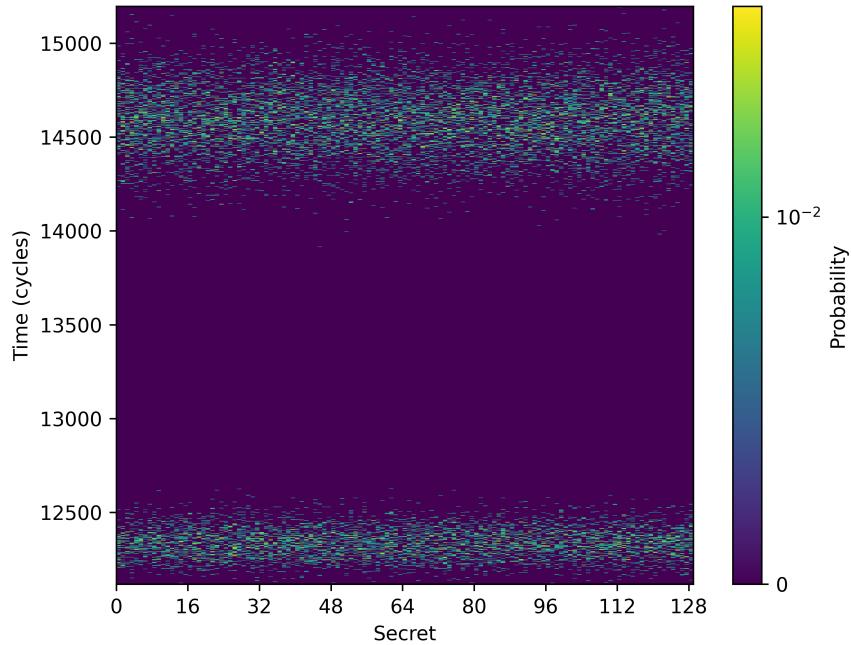

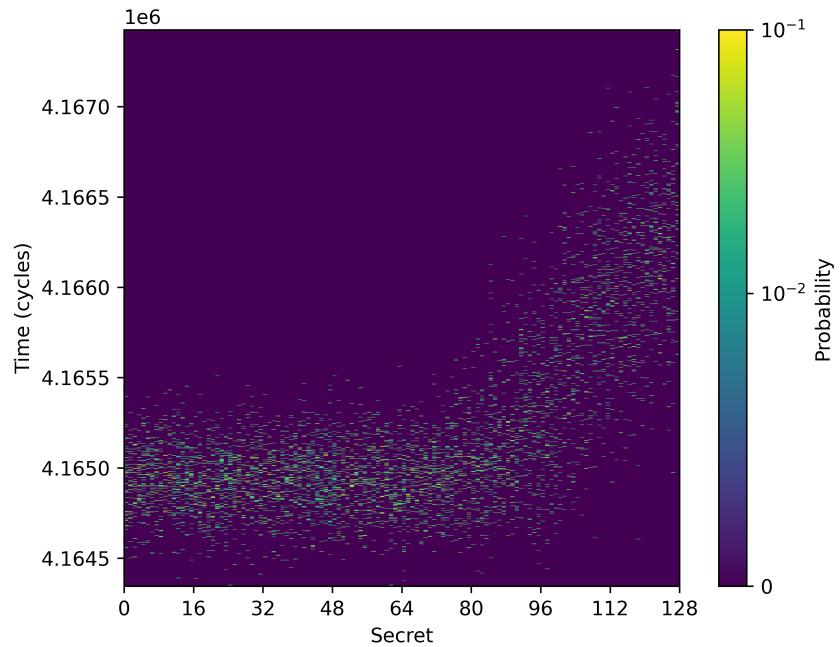

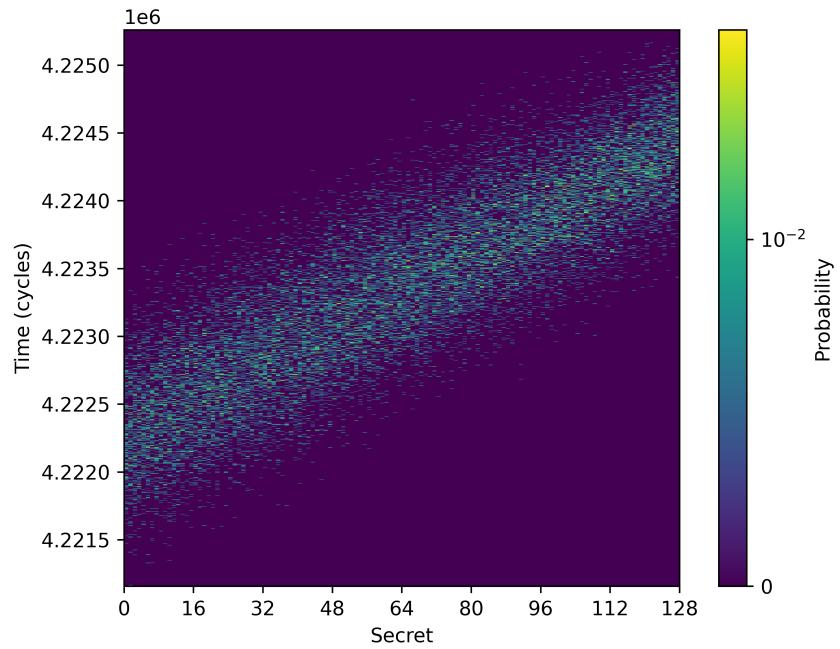

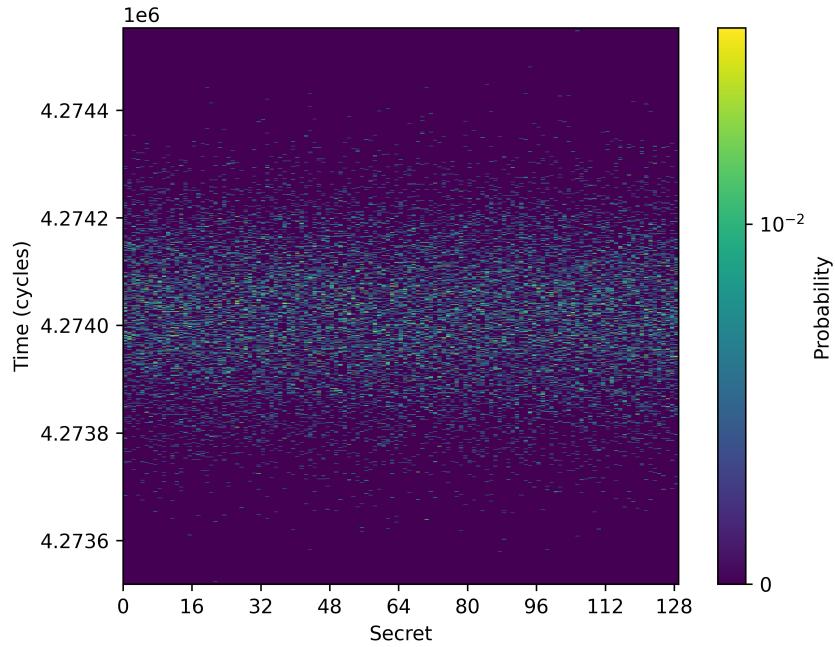

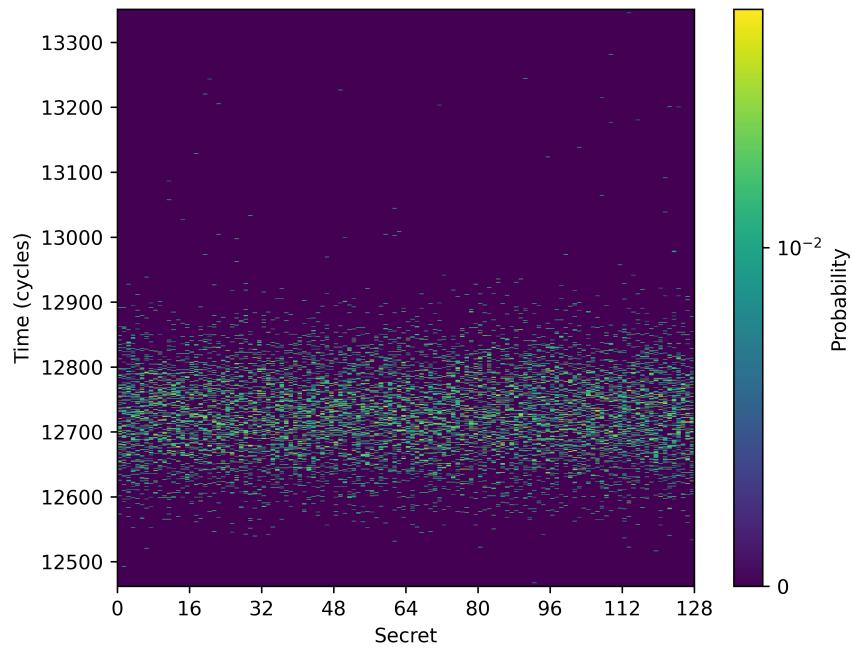

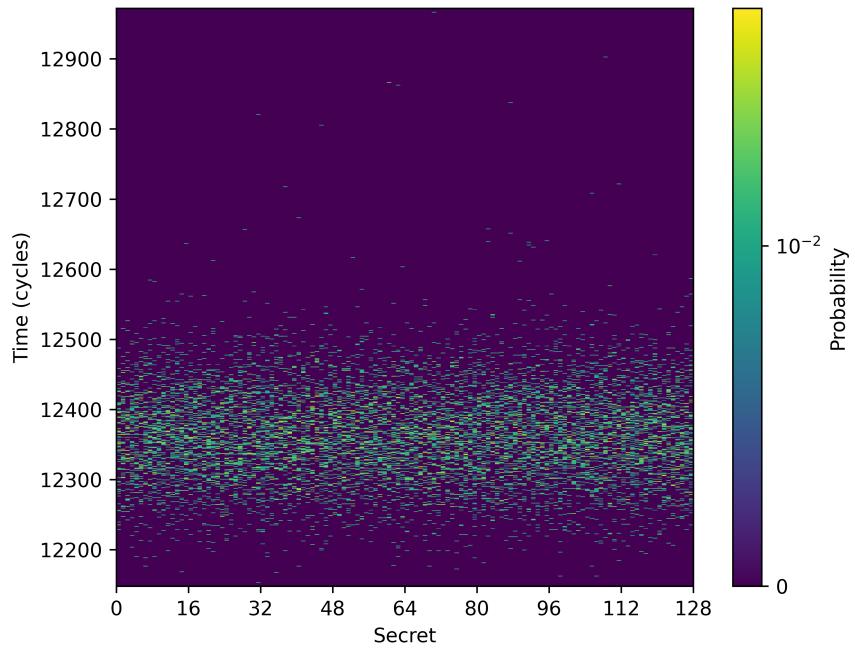

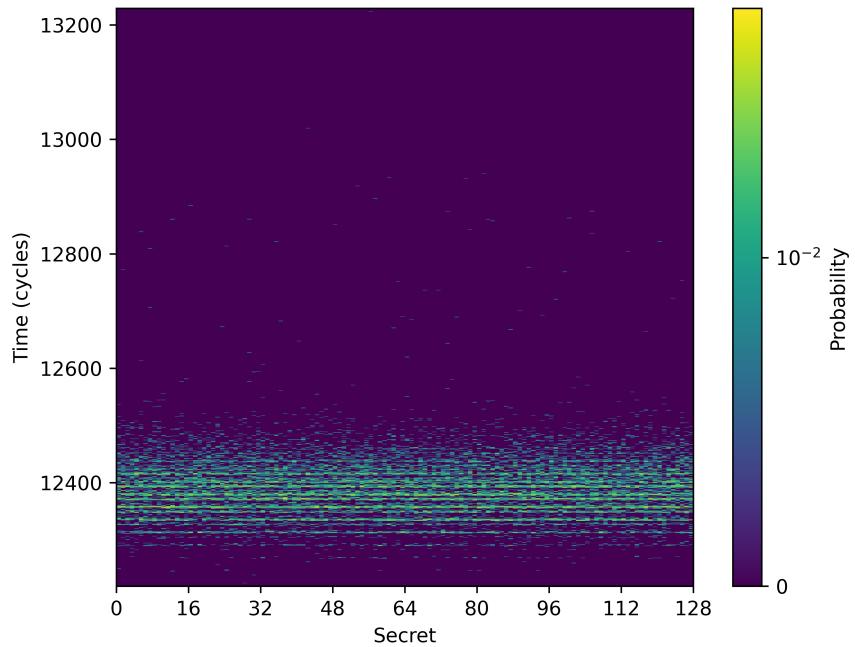

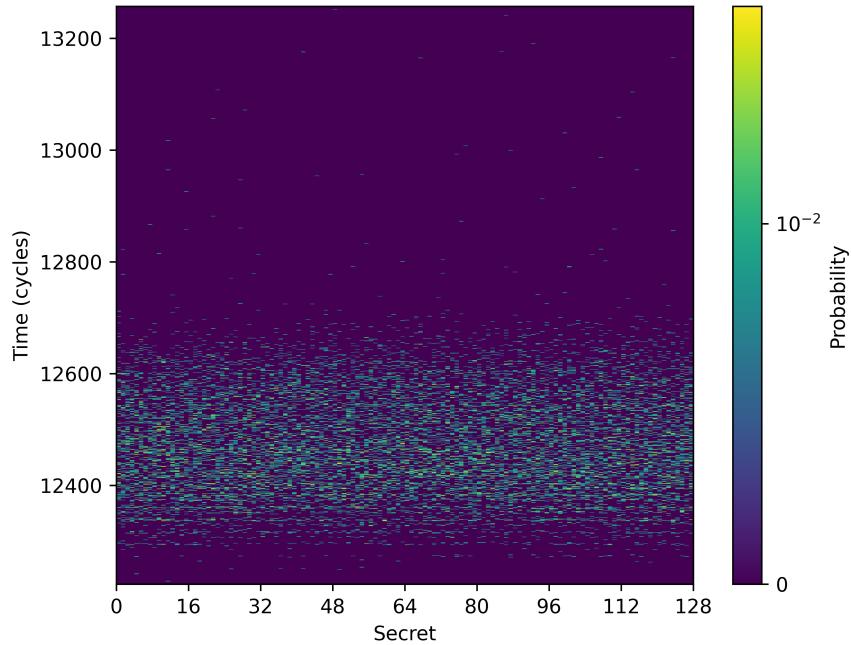

### 3.5.2 SecDCP